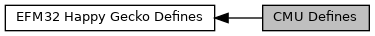

Defined Constants and Types for the EFM32HG Clock Management Unit More...

Enumerations | |

| enum | cmu_periph_clken { CMU_PCNT0 = _REG_BIT(0x078, 1) , CMU_USBLE = _REG_BIT(0x064, 0) , CMU_LEUART0 = _REG_BIT(0x060, 0) , CMU_RTC = _REG_BIT(0x058, 0) , CMU_I2C0 = _REG_BIT(0x044, 11) , CMU_ADC0 = _REG_BIT(0x044, 10) , CMU_VCMP = _REG_BIT(0x044, 9) , CMU_GPIO = _REG_BIT(0x044, 8) , CMU_IDAC0 = _REG_BIT(0x044, 7) , CMU_PRS = _REG_BIT(0x044, 6) , CMU_ACMP0 = _REG_BIT(0x044, 5) , CMU_USART1 = _REG_BIT(0x044, 4) , CMU_USART0 = _REG_BIT(0x044, 3) , CMU_TIMER2 = _REG_BIT(0x044, 2) , CMU_TIMER1 = _REG_BIT(0x044, 1) , CMU_TIMER0 = _REG_BIT(0x044, 0) , CMU_USB = _REG_BIT(0x040, 4) , CMU_USBC = _REG_BIT(0x040, 3) , CMU_LE = _REG_BIT(0x040, 2) , CMU_DMA = _REG_BIT(0x040, 1) } |

| enum | cmu_osc { HFRCO , LFRCO , HFXO , LFXO , AUXHFRCO , USHFRCO , USHFRCODIV2 } |

Functions | |

| void | cmu_enable_lock (void) |

| Enable CMU registers lock. More... | |

| void | cmu_disable_lock (void) |

| Disable CMU registers lock. More... | |

| bool | cmu_get_lock_flag (void) |

| Get CMU register lock flag. More... | |

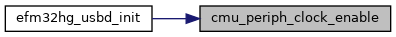

| void | cmu_periph_clock_enable (enum cmu_periph_clken periph) |

| Enable Peripheral Clock in running mode. More... | |

| void | cmu_periph_clock_disable (enum cmu_periph_clken periph) |

| Disable Peripheral Clock in running mode. More... | |

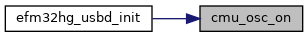

| void | cmu_osc_on (enum cmu_osc osc) |

| Turn on Oscillator. More... | |

| void | cmu_osc_off (enum cmu_osc osc) |

| Turn off Oscillator. More... | |

| bool | cmu_osc_ready_flag (enum cmu_osc osc) |

| Get Oscillator read flag. More... | |

| void | cmu_wait_for_osc_ready (enum cmu_osc osc) |

| Wait while oscillator is not ready. More... | |

| void | cmu_set_hfclk_source (enum cmu_osc osc) |

| Set HFCLK clock source. More... | |

| enum cmu_osc | cmu_get_hfclk_source (void) |

| Get HFCLK clock source. More... | |

| void | cmu_set_usbclk_source (enum cmu_osc osc) |

| Set USBCLK clock source. More... | |

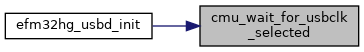

| void | cmu_wait_for_usbclk_selected (enum cmu_osc osc) |

| Wait while USBCLK is not selected. More... | |

Detailed Description

Defined Constants and Types for the EFM32HG Clock Management Unit

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ _REG_BIT

◆ CMU_AUXHFRCOCTR

◆ CMU_AUXHFRCOCTRL_BAND

| #define CMU_AUXHFRCOCTRL_BAND | ( | v | ) | (((v) << CMU_AUXHFRCOCTRL_BAND_SHIFT) & CMU_AUXHFRCOCTRL_BAND_MASK) |

◆ CMU_AUXHFRCOCTRL_BAND_11MHZ

| #define CMU_AUXHFRCOCTRL_BAND_11MHZ CMU_AUXHFRCOCTRL_BAND(1) |

◆ CMU_AUXHFRCOCTRL_BAND_14MHZ

| #define CMU_AUXHFRCOCTRL_BAND_14MHZ CMU_AUXHFRCOCTRL_BAND(0) |

◆ CMU_AUXHFRCOCTRL_BAND_1MHZ

| #define CMU_AUXHFRCOCTRL_BAND_1MHZ CMU_AUXHFRCOCTRL_BAND(3) |

◆ CMU_AUXHFRCOCTRL_BAND_21MHZ

| #define CMU_AUXHFRCOCTRL_BAND_21MHZ CMU_AUXHFRCOCTRL_BAND(7) |

◆ CMU_AUXHFRCOCTRL_BAND_28MHZ

| #define CMU_AUXHFRCOCTRL_BAND_28MHZ CMU_AUXHFRCOCTRL_BAND(6) |

◆ CMU_AUXHFRCOCTRL_BAND_7MHZ

| #define CMU_AUXHFRCOCTRL_BAND_7MHZ CMU_AUXHFRCOCTRL_BAND(2) |

◆ CMU_AUXHFRCOCTRL_BAND_MASK

| #define CMU_AUXHFRCOCTRL_BAND_MASK (0x7 << CMU_AUXHFRCOCTRL_BAND_SHIFT) |

◆ CMU_AUXHFRCOCTRL_BAND_SHIFT

◆ CMU_AUXHFRCOCTRL_TUNING

| #define CMU_AUXHFRCOCTRL_TUNING | ( | v | ) | (((v) << CMU_AUXHFRCOCTRL_TUNING_SHIFT) & CMU_AUXHFRCOCTRL_TUNING_MASK) |

◆ CMU_AUXHFRCOCTRL_TUNING_MASK

| #define CMU_AUXHFRCOCTRL_TUNING_MASK (0xFF << CMU_AUXHFRCOCTRL_TUNING_SHIFT) |

◆ CMU_AUXHFRCOCTRL_TUNING_SHIFT

◆ CMU_CALCNT

◆ CMU_CALCNT_CALCNT

| #define CMU_CALCNT_CALCNT | ( | v | ) | (((v) << CMU_CALCNT_CALCNT_SHIFT) & CMU_CALCNT_CALCNT_MASK) |

◆ CMU_CALCNT_CALCNT_MASK

| #define CMU_CALCNT_CALCNT_MASK (0xFFFFF << CMU_CALCNT_CALCNT_SHIFT) |

◆ CMU_CALCNT_CALCNT_SHIFT

◆ CMU_CALCTRL

◆ CMU_CALCTRL_CONT

◆ CMU_CALCTRL_DOWNSEL

| #define CMU_CALCTRL_DOWNSEL | ( | v | ) | (((v) << CMU_CALCTRL_DOWNSEL_SHIFT) & CMU_CALCTRL_DOWNSEL_MASK) |

◆ CMU_CALCTRL_DOWNSEL_AUXHFRCO

| #define CMU_CALCTRL_DOWNSEL_AUXHFRCO CMU_CALCTRL_DOWNSEL(5) |

◆ CMU_CALCTRL_DOWNSEL_HFCLK

| #define CMU_CALCTRL_DOWNSEL_HFCLK CMU_CALCTRL_DOWNSEL(0) |

◆ CMU_CALCTRL_DOWNSEL_HFRCO

| #define CMU_CALCTRL_DOWNSEL_HFRCO CMU_CALCTRL_DOWNSEL(3) |

◆ CMU_CALCTRL_DOWNSEL_HFXO

| #define CMU_CALCTRL_DOWNSEL_HFXO CMU_CALCTRL_DOWNSEL(1) |

◆ CMU_CALCTRL_DOWNSEL_LFRCO

| #define CMU_CALCTRL_DOWNSEL_LFRCO CMU_CALCTRL_DOWNSEL(4) |

◆ CMU_CALCTRL_DOWNSEL_LFXO

| #define CMU_CALCTRL_DOWNSEL_LFXO CMU_CALCTRL_DOWNSEL(2) |

◆ CMU_CALCTRL_DOWNSEL_MASK

| #define CMU_CALCTRL_DOWNSEL_MASK (0x7 << CMU_CALCTRL_DOWNSEL_SHIFT) |

◆ CMU_CALCTRL_DOWNSEL_SHIFT

◆ CMU_CALCTRL_DOWNSEL_USHFRCO

| #define CMU_CALCTRL_DOWNSEL_USHFRCO CMU_CALCTRL_DOWNSEL(6) |

◆ CMU_CALCTRL_UPSEL

| #define CMU_CALCTRL_UPSEL | ( | v | ) | (((v) << CMU_CALCTRL_UPSEL_SHIFT) & CMU_CALCTRL_UPSEL_MASK) |

◆ CMU_CALCTRL_UPSEL_AUXHFRCO

| #define CMU_CALCTRL_UPSEL_AUXHFRCO CMU_CALCTRL_UPSEL(4) |

◆ CMU_CALCTRL_UPSEL_HFRCO

| #define CMU_CALCTRL_UPSEL_HFRCO CMU_CALCTRL_UPSEL(2) |

◆ CMU_CALCTRL_UPSEL_HFXO

| #define CMU_CALCTRL_UPSEL_HFXO CMU_CALCTRL_UPSEL(0) |

◆ CMU_CALCTRL_UPSEL_LFRCO

| #define CMU_CALCTRL_UPSEL_LFRCO CMU_CALCTRL_UPSEL(3) |

◆ CMU_CALCTRL_UPSEL_LFXO

| #define CMU_CALCTRL_UPSEL_LFXO CMU_CALCTRL_UPSEL(1) |

◆ CMU_CALCTRL_UPSEL_MASK

| #define CMU_CALCTRL_UPSEL_MASK (0x7 << CMU_CALCTRL_UPSEL_SHIFT) |

◆ CMU_CALCTRL_UPSEL_SHIFT

◆ CMU_CALCTRL_UPSEL_USHFRCO

| #define CMU_CALCTRL_UPSEL_USHFRCO CMU_CALCTRL_UPSEL(5) |

◆ CMU_CMD

◆ CMU_CMD_CALSTART

◆ CMU_CMD_CALSTOP

◆ CMU_CMD_HFCLKSEL

| #define CMU_CMD_HFCLKSEL | ( | v | ) | (((v) << CMU_CMD_HFCLKSEL_SHIFT) & CMU_CMD_HFCLKSEL_MASK) |

◆ CMU_CMD_HFCLKSEL_HFRCO

| #define CMU_CMD_HFCLKSEL_HFRCO CMU_CMD_HFCLKSEL(1) |

◆ CMU_CMD_HFCLKSEL_HFXO

| #define CMU_CMD_HFCLKSEL_HFXO CMU_CMD_HFCLKSEL(2) |

◆ CMU_CMD_HFCLKSEL_LFRCO

| #define CMU_CMD_HFCLKSEL_LFRCO CMU_CMD_HFCLKSEL(3) |

◆ CMU_CMD_HFCLKSEL_LFXO

| #define CMU_CMD_HFCLKSEL_LFXO CMU_CMD_HFCLKSEL(4) |

◆ CMU_CMD_HFCLKSEL_MASK

| #define CMU_CMD_HFCLKSEL_MASK (0x7 << CMU_CMD_HFCLKSEL_SHIFT) |

◆ CMU_CMD_HFCLKSEL_SHIFT

◆ CMU_CMD_HFCLKSEL_USHFRCODIV2

| #define CMU_CMD_HFCLKSEL_USHFRCODIV2 CMU_CMD_HFCLKSEL(5) |

◆ CMU_CMD_USBCCLKSEL

| #define CMU_CMD_USBCCLKSEL | ( | v | ) | (((v) << CMU_CMD_USBCCLKSEL_SHIFT) & CMU_CMD_USBCCLKSEL_MASK) |

◆ CMU_CMD_USBCCLKSEL_LFRCO

| #define CMU_CMD_USBCCLKSEL_LFRCO CMU_CMD_USBCCLKSEL(3) |

◆ CMU_CMD_USBCCLKSEL_LFXO

| #define CMU_CMD_USBCCLKSEL_LFXO CMU_CMD_USBCCLKSEL(2) |

◆ CMU_CMD_USBCCLKSEL_MASK

| #define CMU_CMD_USBCCLKSEL_MASK (0x5 << CMU_CMD_USBCCLKSEL_SHIFT) |

◆ CMU_CMD_USBCCLKSEL_SHIFT

◆ CMU_CMD_USBCCLKSEL_USHFRCO

| #define CMU_CMD_USBCCLKSEL_USHFRCO CMU_CMD_USBCCLKSEL(4) |

◆ CMU_CTRL

◆ CMU_CTRL_CLKOUTSEL0

| #define CMU_CTRL_CLKOUTSEL0 | ( | v | ) | (((v) << CMU_CTRL_CLKOUTSEL0_SHIFT) & CMU_CTRL_CLKOUTSEL0_MASK) |

◆ CMU_CTRL_CLKOUTSEL0_AUXHFRCO

| #define CMU_CTRL_CLKOUTSEL0_AUXHFRCO CMU_CTRL_CLKOUTSEL0(7) |

◆ CMU_CTRL_CLKOUTSEL0_HFCLK16

| #define CMU_CTRL_CLKOUTSEL0_HFCLK16 CMU_CTRL_CLKOUTSEL0(5) |

◆ CMU_CTRL_CLKOUTSEL0_HFCLK2

| #define CMU_CTRL_CLKOUTSEL0_HFCLK2 CMU_CTRL_CLKOUTSEL0(2) |

◆ CMU_CTRL_CLKOUTSEL0_HFCLK4

| #define CMU_CTRL_CLKOUTSEL0_HFCLK4 CMU_CTRL_CLKOUTSEL0(3) |

◆ CMU_CTRL_CLKOUTSEL0_HFCLK8

| #define CMU_CTRL_CLKOUTSEL0_HFCLK8 CMU_CTRL_CLKOUTSEL0(4) |

◆ CMU_CTRL_CLKOUTSEL0_HFRCO

| #define CMU_CTRL_CLKOUTSEL0_HFRCO CMU_CTRL_CLKOUTSEL0(0) |

◆ CMU_CTRL_CLKOUTSEL0_HFXO

| #define CMU_CTRL_CLKOUTSEL0_HFXO CMU_CTRL_CLKOUTSEL0(1) |

◆ CMU_CTRL_CLKOUTSEL0_MASK

| #define CMU_CTRL_CLKOUTSEL0_MASK (0x7 << CMU_CTRL_CLKOUTSEL0_SHIFT) |

◆ CMU_CTRL_CLKOUTSEL0_SHIFT

◆ CMU_CTRL_CLKOUTSEL0_ULFRCO

| #define CMU_CTRL_CLKOUTSEL0_ULFRCO CMU_CTRL_CLKOUTSEL0(6) |

◆ CMU_CTRL_CLKOUTSEL1

| #define CMU_CTRL_CLKOUTSEL1 | ( | v | ) | (((v) << CMU_CTRL_CLKOUTSEL1_SHIFT) & CMU_CTRL_CLKOUTSEL1_MASK) |

◆ CMU_CTRL_CLKOUTSEL1_AUXHFRCOQ

| #define CMU_CTRL_CLKOUTSEL1_AUXHFRCOQ CMU_CTRL_CLKOUTSEL1(7) |

◆ CMU_CTRL_CLKOUTSEL1_HFCLK

| #define CMU_CTRL_CLKOUTSEL1_HFCLK CMU_CTRL_CLKOUTSEL1(2) |

◆ CMU_CTRL_CLKOUTSEL1_HFRCOQ

| #define CMU_CTRL_CLKOUTSEL1_HFRCOQ CMU_CTRL_CLKOUTSEL1(6) |

◆ CMU_CTRL_CLKOUTSEL1_HFXOQ

| #define CMU_CTRL_CLKOUTSEL1_HFXOQ CMU_CTRL_CLKOUTSEL1(4) |

◆ CMU_CTRL_CLKOUTSEL1_LFRCO

| #define CMU_CTRL_CLKOUTSEL1_LFRCO CMU_CTRL_CLKOUTSEL1(0) |

◆ CMU_CTRL_CLKOUTSEL1_LFRCOQ

| #define CMU_CTRL_CLKOUTSEL1_LFRCOQ CMU_CTRL_CLKOUTSEL1(5) |

◆ CMU_CTRL_CLKOUTSEL1_LFXO

| #define CMU_CTRL_CLKOUTSEL1_LFXO CMU_CTRL_CLKOUTSEL1(1) |

◆ CMU_CTRL_CLKOUTSEL1_LFXOQ

| #define CMU_CTRL_CLKOUTSEL1_LFXOQ CMU_CTRL_CLKOUTSEL1(3) |

◆ CMU_CTRL_CLKOUTSEL1_MASK

| #define CMU_CTRL_CLKOUTSEL1_MASK (0x7 << CMU_CTRL_CLKOUTSEL1_SHIFT) |

◆ CMU_CTRL_CLKOUTSEL1_SHIFT

◆ CMU_CTRL_CLKOUTSEL1_USHFRCO

| #define CMU_CTRL_CLKOUTSEL1_USHFRCO CMU_CTRL_CLKOUTSEL1(8) |

◆ CMU_CTRL_HFCLKDIV

| #define CMU_CTRL_HFCLKDIV | ( | v | ) | (((v) << CMU_CTRL_HFCLKDIV_SHIFT) & CMU_CTRL_HFCLKDIV_MASK) |

◆ CMU_CTRL_HFCLKDIV_DIV2

| #define CMU_CTRL_HFCLKDIV_DIV2 CMU_CTRL_HFCLKDIV(1) |

◆ CMU_CTRL_HFCLKDIV_DIV3

| #define CMU_CTRL_HFCLKDIV_DIV3 CMU_CTRL_HFCLKDIV(2) |

◆ CMU_CTRL_HFCLKDIV_DIV4

| #define CMU_CTRL_HFCLKDIV_DIV4 CMU_CTRL_HFCLKDIV(3) |

◆ CMU_CTRL_HFCLKDIV_DIV5

| #define CMU_CTRL_HFCLKDIV_DIV5 CMU_CTRL_HFCLKDIV(4) |

◆ CMU_CTRL_HFCLKDIV_DIV6

| #define CMU_CTRL_HFCLKDIV_DIV6 CMU_CTRL_HFCLKDIV(5) |

◆ CMU_CTRL_HFCLKDIV_DIV7

| #define CMU_CTRL_HFCLKDIV_DIV7 CMU_CTRL_HFCLKDIV(6) |

◆ CMU_CTRL_HFCLKDIV_DIV8

| #define CMU_CTRL_HFCLKDIV_DIV8 CMU_CTRL_HFCLKDIV(7) |

◆ CMU_CTRL_HFCLKDIV_MASK

| #define CMU_CTRL_HFCLKDIV_MASK (0x7 << CMU_CTRL_HFCLKDIV_SHIFT) |

◆ CMU_CTRL_HFCLKDIV_NODIV

| #define CMU_CTRL_HFCLKDIV_NODIV CMU_CTRL_HFCLKDIV(0) |

◆ CMU_CTRL_HFCLKDIV_SHIFT

◆ CMU_CTRL_HFXOBOOST

| #define CMU_CTRL_HFXOBOOST | ( | v | ) | (((v) << CMU_CTRL_HFXOBOOST_SHIFT) & CMU_CTRL_HFXOBOOST_MASK) |

◆ CMU_CTRL_HFXOBOOST_100PCENT

| #define CMU_CTRL_HFXOBOOST_100PCENT CMU_CTRL_HFXOBOOST(3) |

◆ CMU_CTRL_HFXOBOOST_50PCENT

| #define CMU_CTRL_HFXOBOOST_50PCENT CMU_CTRL_HFXOBOOST(0) |

◆ CMU_CTRL_HFXOBOOST_70PCENT

| #define CMU_CTRL_HFXOBOOST_70PCENT CMU_CTRL_HFXOBOOST(1) |

◆ CMU_CTRL_HFXOBOOST_80PCENT

| #define CMU_CTRL_HFXOBOOST_80PCENT CMU_CTRL_HFXOBOOST(2) |

◆ CMU_CTRL_HFXOBOOST_MASK

| #define CMU_CTRL_HFXOBOOST_MASK (0x3 << CMU_CTRL_HFXOBOOST_SHIFT) |

◆ CMU_CTRL_HFXOBOOST_SHIFT

◆ CMU_CTRL_HFXOBUFCUR_MASK

◆ CMU_CTRL_HFXOGLITCHDETEN

◆ CMU_CTRL_HFXOMODE

| #define CMU_CTRL_HFXOMODE | ( | v | ) | (((v) << CMU_CTRL_HFXOMODE_SHIFT) & CMU_CTRL_HFXOMODE_MASK) |

◆ CMU_CTRL_HFXOMODE_BUFEXTCLK

| #define CMU_CTRL_HFXOMODE_BUFEXTCLK CMU_CTRL_HFXOMODE(1) |

◆ CMU_CTRL_HFXOMODE_DIGEXTCLK

| #define CMU_CTRL_HFXOMODE_DIGEXTCLK CMU_CTRL_HFXOMODE(2) |

◆ CMU_CTRL_HFXOMODE_MASK

| #define CMU_CTRL_HFXOMODE_MASK (0x3 << CMU_CTRL_HFXOMODE_SHIFT) |

◆ CMU_CTRL_HFXOMODE_SHIFT

◆ CMU_CTRL_HFXOMODE_XTAL

| #define CMU_CTRL_HFXOMODE_XTAL CMU_CTRL_HFXOMODE(0) |

◆ CMU_CTRL_HFXOTIMEOUT

| #define CMU_CTRL_HFXOTIMEOUT | ( | v | ) | (((v) << CMU_CTRL_HFXOTIMEOUT_SHIFT) & CMU_CTRL_HFXOTIMEOUT_MASK) |

◆ CMU_CTRL_HFXOTIMEOUT_16KCYCLES

| #define CMU_CTRL_HFXOTIMEOUT_16KCYCLES CMU_CTRL_HFXOTIMEOUT(3) |

◆ CMU_CTRL_HFXOTIMEOUT_1KCYCLES

| #define CMU_CTRL_HFXOTIMEOUT_1KCYCLES CMU_CTRL_HFXOTIMEOUT(2) |

◆ CMU_CTRL_HFXOTIMEOUT_256CYCLES

| #define CMU_CTRL_HFXOTIMEOUT_256CYCLES CMU_CTRL_HFXOTIMEOUT(1) |

◆ CMU_CTRL_HFXOTIMEOUT_8CYCLES

| #define CMU_CTRL_HFXOTIMEOUT_8CYCLES CMU_CTRL_HFXOTIMEOUT(0) |

◆ CMU_CTRL_HFXOTIMEOUT_MASK

| #define CMU_CTRL_HFXOTIMEOUT_MASK (0x3 << CMU_CTRL_HFXOTIMEOUT_SHIFT) |

◆ CMU_CTRL_HFXOTIMEOUT_SHIFT

◆ CMU_CTRL_LFXOBOOST

◆ CMU_CTRL_LFXOBUFCUR

◆ CMU_CTRL_LFXOMODE

| #define CMU_CTRL_LFXOMODE | ( | v | ) | (((v) << CMU_CTRL_LFXOMODE_SHIFT) & CMU_CTRL_LFXOMODE_MASK) |

◆ CMU_CTRL_LFXOMODE_BUFEXTCLK

| #define CMU_CTRL_LFXOMODE_BUFEXTCLK CMU_CTRL_LFXOMODE(1) |

◆ CMU_CTRL_LFXOMODE_DIGEXTCLK

| #define CMU_CTRL_LFXOMODE_DIGEXTCLK CMU_CTRL_LFXOMODE(2) |

◆ CMU_CTRL_LFXOMODE_MASK

| #define CMU_CTRL_LFXOMODE_MASK (0x3 << CMU_CTRL_LFXOMODE_SHIFT) |

◆ CMU_CTRL_LFXOMODE_SHIFT

◆ CMU_CTRL_LFXOMODE_XTAL

| #define CMU_CTRL_LFXOMODE_XTAL CMU_CTRL_LFXOMODE(0) |

◆ CMU_CTRL_LFXOTIMEOUT

| #define CMU_CTRL_LFXOTIMEOUT | ( | v | ) | (((v) << CMU_CTRL_LFXOTIMEOUT_SHIFT) & CMU_CTRL_LFXOTIMEOUT_MASK) |

◆ CMU_CTRL_LFXOTIMEOUT_16KCYCLES

| #define CMU_CTRL_LFXOTIMEOUT_16KCYCLES CMU_CTRL_LFXOTIMEOUT(2) |

◆ CMU_CTRL_LFXOTIMEOUT_1KCYCLES

| #define CMU_CTRL_LFXOTIMEOUT_1KCYCLES CMU_CTRL_LFXOTIMEOUT(1) |

◆ CMU_CTRL_LFXOTIMEOUT_32KCYCLES

| #define CMU_CTRL_LFXOTIMEOUT_32KCYCLES CMU_CTRL_LFXOTIMEOUT(3) |

◆ CMU_CTRL_LFXOTIMEOUT_8CYCLES

| #define CMU_CTRL_LFXOTIMEOUT_8CYCLES CMU_CTRL_LFXOTIMEOUT(0) |

◆ CMU_CTRL_LFXOTIMEOUT_MASK

| #define CMU_CTRL_LFXOTIMEOUT_MASK (0x3 << CMU_CTRL_LFXOTIMEOUT_SHIFT) |

◆ CMU_CTRL_LFXOTIMEOUT_SHIFT

◆ CMU_FREEZE

◆ CMU_FREEZE_REGFREEZE

◆ CMU_HFCORECLKDIV

◆ CMU_HFCORECLKDIV_HFCORECLKDIV

| #define CMU_HFCORECLKDIV_HFCORECLKDIV | ( | v | ) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV128

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV128 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK128 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV16

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV16 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK16 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV2

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV2 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK2 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV256

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV256 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK256 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV32

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV32 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK32 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV4

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV4 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK4 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV512

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV512 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK512 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV64

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV64 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK64 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_DIV8

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_DIV8 CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK8 |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK CMU_HFCORECLKDIV_HFCORECLKDIV(0) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK128

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK128 CMU_HFCORECLKDIV_HFCORECLKDIV(7) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK16

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK16 CMU_HFCORECLKDIV_HFCORECLKDIV(4) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK2

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK2 CMU_HFCORECLKDIV_HFCORECLKDIV(1) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK256

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK256 CMU_HFCORECLKDIV_HFCORECLKDIV(8) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK32

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK32 CMU_HFCORECLKDIV_HFCORECLKDIV(5) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK4

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK4 CMU_HFCORECLKDIV_HFCORECLKDIV(2) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK512

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK512 CMU_HFCORECLKDIV_HFCORECLKDIV(9) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK64

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK64 CMU_HFCORECLKDIV_HFCORECLKDIV(6) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK8

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK8 CMU_HFCORECLKDIV_HFCORECLKDIV(3) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_MASK

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_MASK (0xF << CMU_HFCORECLKDIV_HFCORECLKDIV_SHIFT) |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_NODIV

| #define CMU_HFCORECLKDIV_HFCORECLKDIV_NODIV CMU_HFCORECLKDIV_HFCORECLKDIV_HFCLK |

◆ CMU_HFCORECLKDIV_HFCORECLKDIV_SHIFT

◆ CMU_HFCORECLKDIV_HFCORECLKLEDIV

◆ CMU_HFCORECLKEN0

◆ CMU_HFCORECLKEN0_AES

◆ CMU_HFCORECLKEN0_DMA

◆ CMU_HFCORECLKEN0_LE

◆ CMU_HFCORECLKEN0_USB

◆ CMU_HFCORECLKEN0_USBC

◆ CMU_HFPERCLKDIV

◆ CMU_HFPERCLKDIV_HFPERCLKDIV

| #define CMU_HFPERCLKDIV_HFPERCLKDIV | ( | v | ) |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV128

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV128 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK128 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV16

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV16 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK16 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV2

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV2 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK2 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV256

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV256 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK256 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV32

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV32 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK32 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV4

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV4 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK4 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV512

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV512 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK512 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV64

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV64 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK64 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_DIV8

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_DIV8 CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK8 |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_MASK

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_MASK (0xF << CMU_HFPERCLKDIV_HFPERCLKDIV_SHIFT) |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_NODIV

| #define CMU_HFPERCLKDIV_HFPERCLKDIV_NODIV CMU_HFPERCLKDIV_HFPERCLKDIV_HFCLK |

◆ CMU_HFPERCLKDIV_HFPERCLKDIV_SHIFT

◆ CMU_HFPERCLKDIV_HFPERCLKEN

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK CMU_HFPERCLKDIV_HFPERCLKDIV(0) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK128

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK128 CMU_HFPERCLKDIV_HFPERCLKDIV(7) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK16

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK16 CMU_HFPERCLKDIV_HFPERCLKDIV(4) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK2

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK2 CMU_HFPERCLKDIV_HFPERCLKDIV(1) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK256

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK256 CMU_HFPERCLKDIV_HFPERCLKDIV(8) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK32

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK32 CMU_HFPERCLKDIV_HFPERCLKDIV(5) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK4

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK4 CMU_HFPERCLKDIV_HFPERCLKDIV(2) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK512

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK512 CMU_HFPERCLKDIV_HFPERCLKDIV(9) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK64

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK64 CMU_HFPERCLKDIV_HFPERCLKDIV(6) |

◆ CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK8

| #define CMU_HFPERCLKDIV_HFPERCLKHFCLK_HFCLK8 CMU_HFPERCLKDIV_HFPERCLKDIV(3) |

◆ CMU_HFPERCLKEN0

◆ CMU_HFPERCLKEN0_ACMP0

◆ CMU_HFPERCLKEN0_ADC0

◆ CMU_HFPERCLKEN0_GPIO

◆ CMU_HFPERCLKEN0_I2C0

◆ CMU_HFPERCLKEN0_IDAC0

◆ CMU_HFPERCLKEN0_PRS

◆ CMU_HFPERCLKEN0_TIMER0

◆ CMU_HFPERCLKEN0_TIMER1

◆ CMU_HFPERCLKEN0_TIMER2

◆ CMU_HFPERCLKEN0_USART0

◆ CMU_HFPERCLKEN0_USART1

◆ CMU_HFPERCLKEN0_VCMP

◆ CMU_HFRCOCTRL

◆ CMU_HFRCOCTRL_BAND

| #define CMU_HFRCOCTRL_BAND | ( | v | ) | (((v) << CMU_HFRCOCTRL_BAND_SHIFT) & CMU_HFRCOCTRL_BAND_MASK) |

◆ CMU_HFRCOCTRL_BAND_11MHZ

| #define CMU_HFRCOCTRL_BAND_11MHZ CMU_HFRCOCTRL_BAND(2) |

◆ CMU_HFRCOCTRL_BAND_14MHZ

| #define CMU_HFRCOCTRL_BAND_14MHZ CMU_HFRCOCTRL_BAND(3) |

◆ CMU_HFRCOCTRL_BAND_1MHZ

| #define CMU_HFRCOCTRL_BAND_1MHZ CMU_HFRCOCTRL_BAND(0) |

◆ CMU_HFRCOCTRL_BAND_21MHZ

| #define CMU_HFRCOCTRL_BAND_21MHZ CMU_HFRCOCTRL_BAND(4) |

◆ CMU_HFRCOCTRL_BAND_7MHZ

| #define CMU_HFRCOCTRL_BAND_7MHZ CMU_HFRCOCTRL_BAND(1) |

◆ CMU_HFRCOCTRL_BAND_MASK

| #define CMU_HFRCOCTRL_BAND_MASK (0x7 << CMU_HFRCOCTRL_BAND_SHIFT) |

◆ CMU_HFRCOCTRL_BAND_SHIFT

◆ CMU_HFRCOCTRL_SUDELAY

| #define CMU_HFRCOCTRL_SUDELAY | ( | v | ) | ((((v) << CMU_HFRCOCTRL_SUDELAY_SHIFT) & CMU_HFRCOCTRL_SUDELAY_MASK)) |

◆ CMU_HFRCOCTRL_SUDELAY_MASK

| #define CMU_HFRCOCTRL_SUDELAY_MASK (0x1F << CMU_HFRCOCTRL_SUDELAY_SHIFT) |

◆ CMU_HFRCOCTRL_SUDELAY_SHIFT

◆ CMU_HFRCOCTRL_TUNING

| #define CMU_HFRCOCTRL_TUNING | ( | v | ) | (((v) << CMU_HFRCOCTRL_TUNING_SHIFT) & CMU_HFRCOCTRL_TUNING_MASK) |

◆ CMU_HFRCOCTRL_TUNING_MASK

| #define CMU_HFRCOCTRL_TUNING_MASK (0xFF << CMU_HFRCOCTRL_TUNING_SHIFT) |

◆ CMU_HFRCOCTRL_TUNING_SHIFT

◆ CMU_IEN

◆ CMU_IEN_AUXHFRCORDY

◆ CMU_IEN_CALOF

◆ CMU_IEN_CALRDY

◆ CMU_IEN_HFRCORDY

◆ CMU_IEN_HFXORDY

◆ CMU_IEN_LFRCORDY

◆ CMU_IEN_LFXORDY

◆ CMU_IEN_USBCHFOSCSEL

◆ CMU_IEN_USHFRCORDY

◆ CMU_IF

◆ CMU_IF_AUXHFRCORDY

◆ CMU_IF_CALOF

◆ CMU_IF_CALRDY

◆ CMU_IF_HFRCORDY

◆ CMU_IF_HFXORDY

◆ CMU_IF_LFRCORDY

◆ CMU_IF_LFXORDY

◆ CMU_IF_USBCHFOSCSEL

◆ CMU_IF_USHFRCORDY

◆ CMU_IFC

◆ CMU_IFC_AUXHFRCORDY

◆ CMU_IFC_CALOF

◆ CMU_IFC_CALRDY

◆ CMU_IFC_HFRCORDY

◆ CMU_IFC_HFXORDY

◆ CMU_IFC_LFRCORDY

◆ CMU_IFC_LFXORDY

◆ CMU_IFC_USBCHFOSCSEL

◆ CMU_IFC_USHFRCORDY

◆ CMU_IFS

◆ CMU_IFS_AUXHFRCORDY

◆ CMU_IFS_CALOF

◆ CMU_IFS_CALRDY

◆ CMU_IFS_HFRCORDY

◆ CMU_IFS_HFXORDY

◆ CMU_IFS_LFRCORDY

◆ CMU_IFS_LFXORDY

◆ CMU_IFS_USBCHFOSCSEL

◆ CMU_IFS_USHFRCORDY

◆ CMU_LFACLKEN0

◆ CMU_LFACLKEN0_RTC

◆ CMU_LFAPRESC0

◆ CMU_LFAPRESC0_RTC

| #define CMU_LFAPRESC0_RTC | ( | v | ) | (((v) << CMU_LFAPRESC0_RTC_SHIFT) & CMU_LFAPRESC0_RTC_MASK) |

◆ CMU_LFAPRESC0_RTC_DIV1

| #define CMU_LFAPRESC0_RTC_DIV1 CMU_LFAPRESC0_RTC(0) |

◆ CMU_LFAPRESC0_RTC_DIV1024

| #define CMU_LFAPRESC0_RTC_DIV1024 CMU_LFAPRESC0_RTC(10) |

◆ CMU_LFAPRESC0_RTC_DIV128

| #define CMU_LFAPRESC0_RTC_DIV128 CMU_LFAPRESC0_RTC(7) |

◆ CMU_LFAPRESC0_RTC_DIV16

| #define CMU_LFAPRESC0_RTC_DIV16 CMU_LFAPRESC0_RTC(4) |

◆ CMU_LFAPRESC0_RTC_DIV16384

| #define CMU_LFAPRESC0_RTC_DIV16384 CMU_LFAPRESC0_RTC(14) |

◆ CMU_LFAPRESC0_RTC_DIV2

| #define CMU_LFAPRESC0_RTC_DIV2 CMU_LFAPRESC0_RTC(1) |

◆ CMU_LFAPRESC0_RTC_DIV2048

| #define CMU_LFAPRESC0_RTC_DIV2048 CMU_LFAPRESC0_RTC(11) |

◆ CMU_LFAPRESC0_RTC_DIV256

| #define CMU_LFAPRESC0_RTC_DIV256 CMU_LFAPRESC0_RTC(8) |

◆ CMU_LFAPRESC0_RTC_DIV32

| #define CMU_LFAPRESC0_RTC_DIV32 CMU_LFAPRESC0_RTC(5) |

◆ CMU_LFAPRESC0_RTC_DIV32768

| #define CMU_LFAPRESC0_RTC_DIV32768 CMU_LFAPRESC0_RTC(15) |

◆ CMU_LFAPRESC0_RTC_DIV4

| #define CMU_LFAPRESC0_RTC_DIV4 CMU_LFAPRESC0_RTC(2) |

◆ CMU_LFAPRESC0_RTC_DIV4096

| #define CMU_LFAPRESC0_RTC_DIV4096 CMU_LFAPRESC0_RTC(12) |

◆ CMU_LFAPRESC0_RTC_DIV512

| #define CMU_LFAPRESC0_RTC_DIV512 CMU_LFAPRESC0_RTC(9) |

◆ CMU_LFAPRESC0_RTC_DIV64

| #define CMU_LFAPRESC0_RTC_DIV64 CMU_LFAPRESC0_RTC(6) |

◆ CMU_LFAPRESC0_RTC_DIV8

| #define CMU_LFAPRESC0_RTC_DIV8 CMU_LFAPRESC0_RTC(3) |

◆ CMU_LFAPRESC0_RTC_DIV8192

| #define CMU_LFAPRESC0_RTC_DIV8192 CMU_LFAPRESC0_RTC(13) |

◆ CMU_LFAPRESC0_RTC_MASK

| #define CMU_LFAPRESC0_RTC_MASK (0xF << CMU_LFAPRESC0_RTC_SHIFT) |

◆ CMU_LFAPRESC0_RTC_NODIV

| #define CMU_LFAPRESC0_RTC_NODIV CMU_LFAPRESC0_RTC_DIV1 |

◆ CMU_LFAPRESC0_RTC_SHIFT

◆ CMU_LFBCLKEN0

◆ CMU_LFBCLKEN0_LEUART0

◆ CMU_LFBPRESC0

◆ CMU_LFBPRESC0_LEUART0

| #define CMU_LFBPRESC0_LEUART0 | ( | v | ) | (((v) << CMU_LFBPRESC0_LEUART0_SHIFT) & CMU_LFBPRESC0_LEUART0_MASK) |

◆ CMU_LFBPRESC0_LEUART0_DIV1

| #define CMU_LFBPRESC0_LEUART0_DIV1 CMU_LFBPRESC0_LEUART0(0) |

◆ CMU_LFBPRESC0_LEUART0_DIV2

| #define CMU_LFBPRESC0_LEUART0_DIV2 CMU_LFBPRESC0_LEUART0(1) |

◆ CMU_LFBPRESC0_LEUART0_DIV4

| #define CMU_LFBPRESC0_LEUART0_DIV4 CMU_LFBPRESC0_LEUART0(2) |

◆ CMU_LFBPRESC0_LEUART0_DIV8

| #define CMU_LFBPRESC0_LEUART0_DIV8 CMU_LFBPRESC0_LEUART0(3) |

◆ CMU_LFBPRESC0_LEUART0_MASK

| #define CMU_LFBPRESC0_LEUART0_MASK (0x3 << CMU_LFBPRESC0_LEUART0_SHIFT) |

◆ CMU_LFBPRESC0_LEUART0_NODIV

| #define CMU_LFBPRESC0_LEUART0_NODIV CMU_LFBPRESC0_LEUART0_DIV1 |

◆ CMU_LFBPRESC0_LEUART0_SHIFT

◆ CMU_LFCCLKEN0

◆ CMU_LFCCLKEN0_USBLE

◆ CMU_LFCLKSEL

◆ CMU_LFCLKSEL_LFA

| #define CMU_LFCLKSEL_LFA | ( | v | ) | (((v) << CMU_LFCLKSEL_LFA_SHIFT) & CMU_LFCLKSEL_LFA_MASK) |

◆ CMU_LFCLKSEL_LFA_MASK

| #define CMU_LFCLKSEL_LFA_MASK (0x3 << CMU_LFCLKSEL_LFA_SHIFT) |

◆ CMU_LFCLKSEL_LFA_SHIFT

◆ CMU_LFCLKSEL_LFAE

◆ CMU_LFCLKSEL_LFB

| #define CMU_LFCLKSEL_LFB | ( | v | ) | (((v) << CMU_LFCLKSEL_LFB_SHIFT) & CMU_LFCLKSEL_LFB_MASK) |

◆ CMU_LFCLKSEL_LFB_MASK

| #define CMU_LFCLKSEL_LFB_MASK (0x3 << CMU_LFCLKSEL_LFB_SHIFT) |

◆ CMU_LFCLKSEL_LFB_SHIFT

◆ CMU_LFCLKSEL_LFBE

◆ CMU_LFCLKSEL_LFC

| #define CMU_LFCLKSEL_LFC | ( | v | ) | (((v) << CMU_LFCLKSEL_LFC_SHIFT) & CMU_LFCLKSEL_LFC_MASK) |

◆ CMU_LFCLKSEL_LFC_DISABLED

| #define CMU_LFCLKSEL_LFC_DISABLED CMU_LFCLKSEL_LFC(0) |

◆ CMU_LFCLKSEL_LFC_LFRCO

| #define CMU_LFCLKSEL_LFC_LFRCO CMU_LFCLKSEL_LFC(1) |

◆ CMU_LFCLKSEL_LFC_LFXO

| #define CMU_LFCLKSEL_LFC_LFXO CMU_LFCLKSEL_LFC(2) |

◆ CMU_LFCLKSEL_LFC_MASK

| #define CMU_LFCLKSEL_LFC_MASK (0x3 << CMU_LFCLKSEL_LFC_SHIFT) |

◆ CMU_LFCLKSEL_LFC_SHIFT

◆ CMU_LFRCOCTRL

◆ CMU_LFRCOCTRL_TUNING

| #define CMU_LFRCOCTRL_TUNING | ( | v | ) | (((v) << CMU_LFRCOCTRL_TUNING_SHIFT) & CMU_LFRCOCTRL_TUNING_MASK) |

◆ CMU_LFRCOCTRL_TUNING_MASK

| #define CMU_LFRCOCTRL_TUNING_MASK (0xFF << CMU_LFRCOCTRL_TUNING_SHIFT) |

◆ CMU_LFRCOCTRL_TUNING_SHIFT

◆ CMU_LOCK

◆ CMU_LOCK_LOCKKEY_LOCK

| #define CMU_LOCK_LOCKKEY_LOCK (0x0000 << CMU_LOCK_LOCKKEY_SHIFT) |

◆ CMU_LOCK_LOCKKEY_LOCKED

| #define CMU_LOCK_LOCKKEY_LOCKED (0x0001 << CMU_LOCK_LOCKKEY_SHIFT) |

◆ CMU_LOCK_LOCKKEY_MASK

| #define CMU_LOCK_LOCKKEY_MASK (0xFFFF << CMU_LOCK_LOCKKEY_SHIFT) |

◆ CMU_LOCK_LOCKKEY_SHIFT

◆ CMU_LOCK_LOCKKEY_UNLOCK

| #define CMU_LOCK_LOCKKEY_UNLOCK (0x580E << CMU_LOCK_LOCKKEY_SHIFT) |

◆ CMU_LOCK_LOCKKEY_UNLOCKED

| #define CMU_LOCK_LOCKKEY_UNLOCKED (0x0000 << CMU_LOCK_LOCKKEY_SHIFT) |

◆ CMU_OSCENCMD

◆ CMU_OSCENCMD_AUXHFRCODIS

◆ CMU_OSCENCMD_AUXHFRCOEN

◆ CMU_OSCENCMD_HFRCODIS

◆ CMU_OSCENCMD_HFRCOEN

◆ CMU_OSCENCMD_HFXODIS

◆ CMU_OSCENCMD_HFXOEN

◆ CMU_OSCENCMD_LFRCODIS

◆ CMU_OSCENCMD_LFRCOEN

◆ CMU_OSCENCMD_LFXODIS

◆ CMU_OSCENCMD_LFXOEN

◆ CMU_OSCENCMD_USHFRCODIS

◆ CMU_OSCENCMD_USHFRCOEN

◆ CMU_PCNTCTRL

◆ CMU_PCNTCTRL_PCNT0CLKEN

◆ CMU_PCNTCTRL_PCNT0CLKSEL

◆ CMU_ROUTE

◆ CMU_ROUTE_CLKOUT0PEN

◆ CMU_ROUTE_CLKOUT1PEN

◆ CMU_ROUTE_LOCATION_LOC0

| #define CMU_ROUTE_LOCATION_LOC0 CMU_ROUTE_LOCATION_LOCx(0) |

◆ CMU_ROUTE_LOCATION_LOC1

| #define CMU_ROUTE_LOCATION_LOC1 CMU_ROUTE_LOCATION_LOCx(1) |

◆ CMU_ROUTE_LOCATION_LOC2

| #define CMU_ROUTE_LOCATION_LOC2 CMU_ROUTE_LOCATION_LOCx(2) |

◆ CMU_ROUTE_LOCATION_LOC3

| #define CMU_ROUTE_LOCATION_LOC3 CMU_ROUTE_LOCATION_LOCx(3) |

◆ CMU_ROUTE_LOCATION_LOCx

| #define CMU_ROUTE_LOCATION_LOCx | ( | i | ) | (((i) << CMU_ROUTE_LOCATION_SHIFT) & CMU_ROUTE_LOCATION_MASK) |

◆ CMU_ROUTE_LOCATION_MASK

| #define CMU_ROUTE_LOCATION_MASK (0x7 << CMU_ROUTE_LOCATION_SHIFT) |

◆ CMU_ROUTE_LOCATION_SHIFT

◆ CMU_STATUS

◆ CMU_STATUS_AUXHFRCOENS

◆ CMU_STATUS_AUXHFRCORDY

◆ CMU_STATUS_CALBSY

◆ CMU_STATUS_HFRCOENS

◆ CMU_STATUS_HFRCORDY

◆ CMU_STATUS_HFRCOSEL

◆ CMU_STATUS_HFXOENS

◆ CMU_STATUS_HFXORDY

◆ CMU_STATUS_HFXOSEL

◆ CMU_STATUS_LFRCOENS

◆ CMU_STATUS_LFRCORDY

◆ CMU_STATUS_LFRCOSEL

◆ CMU_STATUS_LFXOENS

◆ CMU_STATUS_LFXORDY

◆ CMU_STATUS_LFXOSEL

◆ CMU_STATUS_USBCHFCLKSYNC

◆ CMU_STATUS_USBCLFRCOSEL

◆ CMU_STATUS_USBCLFXOSEL

◆ CMU_STATUS_USBCUSHFRCOSEL

◆ CMU_STATUS_USHFRCODIV2SEL

◆ CMU_STATUS_USHFRCOENS

◆ CMU_STATUS_USHFRCORDY

◆ CMU_STATUS_USHFRCOSUSPEND

◆ CMU_SYNCBUSY

◆ CMU_SYNCBUSY_LFACLKEN0

◆ CMU_SYNCBUSY_LFAPRESC0

◆ CMU_SYNCBUSY_LFBCLKEN0

◆ CMU_SYNCBUSY_LFBPRESC0

◆ CMU_SYNCBUSY_LFCCLKEN0

◆ CMU_USBCRCTRL

◆ CMU_USBCRCTRL_EN

◆ CMU_USBCRCTRL_LSMODE

◆ CMU_USHFRCOCONF

◆ CMU_USHFRCOCONF_BAND_24MHZ

◆ CMU_USHFRCOCONF_BAND_48MHZ

◆ CMU_USHFRCOCONF_BAND_MASK

◆ CMU_USHFRCOCTRL

◆ CMU_USHFRCOCTRL_DITHEN

◆ CMU_USHFRCOCTRL_SUSPEND

◆ CMU_USHFRCOCTRL_TIMEOUT_MASK

◆ CMU_USHFRCOCTRL_TUNING_MASK

◆ CMU_USHFRCOTUNE

◆ CMU_USHFRCOTUNE_FINETUNING_MASK

◆ CMU_USHFRCOTUNE_USHFRCODIV2DIS

Enumeration Type Documentation

◆ cmu_osc

| enum cmu_osc |

◆ cmu_periph_clken

| enum cmu_periph_clken |

Function Documentation

◆ cmu_disable_lock()

| void cmu_disable_lock | ( | void | ) |

Disable CMU registers lock.

Definition at line 39 of file cmu.c.

References CMU_LOCK, and CMU_LOCK_LOCKKEY_UNLOCK.

◆ cmu_enable_lock()

| void cmu_enable_lock | ( | void | ) |

Enable CMU registers lock.

Definition at line 31 of file cmu.c.

References CMU_LOCK, and CMU_LOCK_LOCKKEY_LOCK.

◆ cmu_get_hfclk_source()

| enum cmu_osc cmu_get_hfclk_source | ( | void | ) |

Get HFCLK clock source.

- Return values

-

enum cmu_osc Oscillator name

Definition at line 251 of file cmu.c.

References CMU_STATUS, CMU_STATUS_HFRCOSEL, CMU_STATUS_HFXOSEL, CMU_STATUS_LFRCOSEL, CMU_STATUS_LFXOSEL, CMU_STATUS_USHFRCODIV2SEL, HFRCO, HFXO, LFRCO, LFXO, and USHFRCODIV2.

◆ cmu_get_lock_flag()

| bool cmu_get_lock_flag | ( | void | ) |

Get CMU register lock flag.

- Return values

-

true if flag is set false if flag is not set

Definition at line 49 of file cmu.c.

References CMU_LOCK, CMU_LOCK_LOCKKEY_LOCKED, and CMU_LOCK_LOCKKEY_MASK.

◆ cmu_osc_off()

| void cmu_osc_off | ( | enum cmu_osc | osc | ) |

Turn off Oscillator.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

Definition at line 123 of file cmu.c.

References AUXHFRCO, CMU_OSCENCMD, CMU_OSCENCMD_AUXHFRCODIS, CMU_OSCENCMD_HFRCODIS, CMU_OSCENCMD_HFXODIS, CMU_OSCENCMD_LFRCODIS, CMU_OSCENCMD_LFXODIS, CMU_OSCENCMD_USHFRCODIS, HFRCO, HFXO, LFRCO, LFXO, and USHFRCO.

◆ cmu_osc_on()

| void cmu_osc_on | ( | enum cmu_osc | osc | ) |

Turn on Oscillator.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

Definition at line 92 of file cmu.c.

References AUXHFRCO, CMU_OSCENCMD, CMU_OSCENCMD_AUXHFRCOEN, CMU_OSCENCMD_HFRCOEN, CMU_OSCENCMD_HFXOEN, CMU_OSCENCMD_LFRCOEN, CMU_OSCENCMD_LFXOEN, CMU_OSCENCMD_USHFRCOEN, HFRCO, HFXO, LFRCO, LFXO, and USHFRCO.

Referenced by efm32hg_usbd_init().

◆ cmu_osc_ready_flag()

| bool cmu_osc_ready_flag | ( | enum cmu_osc | osc | ) |

Get Oscillator read flag.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

- Return values

-

true if flag is set false if flag is not set

Definition at line 156 of file cmu.c.

References AUXHFRCO, CMU_STATUS, CMU_STATUS_AUXHFRCORDY, CMU_STATUS_HFRCORDY, CMU_STATUS_HFXORDY, CMU_STATUS_LFRCORDY, CMU_STATUS_LFXORDY, CMU_STATUS_USHFRCORDY, HFRCO, HFXO, LFRCO, LFXO, and USHFRCO.

◆ cmu_periph_clock_disable()

| void cmu_periph_clock_disable | ( | enum cmu_periph_clken | clken | ) |

◆ cmu_periph_clock_enable()

| void cmu_periph_clock_enable | ( | enum cmu_periph_clken | clken | ) |

Enable Peripheral Clock in running mode.

Enable the clock on particular peripheral.

- Parameters

-

[in] clken Peripheral Name

For available constants, see enum::cmu_periph_clken (CMU_LEUART1 for example)

Definition at line 68 of file cmu.c.

References _CMU_BIT, and _CMU_REG.

Referenced by efm32hg_usbd_init().

◆ cmu_set_hfclk_source()

| void cmu_set_hfclk_source | ( | enum cmu_osc | osc | ) |

Set HFCLK clock source.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

- Note

- calling cmu_set_hfclk_source() do not set source immediately, use cmu_get_hfclk_source() to verify that the source has been set.

- See also

- cmu_get_hfclk_source()

Definition at line 223 of file cmu.c.

References CMU_CMD, CMU_CMD_HFCLKSEL_HFRCO, CMU_CMD_HFCLKSEL_HFXO, CMU_CMD_HFCLKSEL_LFRCO, CMU_CMD_HFCLKSEL_LFXO, CMU_CMD_HFCLKSEL_USHFRCODIV2, HFRCO, HFXO, LFRCO, LFXO, and USHFRCODIV2.

◆ cmu_set_usbclk_source()

| void cmu_set_usbclk_source | ( | enum cmu_osc | osc | ) |

Set USBCLK clock source.

- Parameters

-

osc Oscillator name

Definition at line 274 of file cmu.c.

References CMU_CMD, CMU_CMD_USBCCLKSEL_LFRCO, CMU_CMD_USBCCLKSEL_LFXO, CMU_CMD_USBCCLKSEL_USHFRCO, LFRCO, LFXO, and USHFRCO.

Referenced by efm32hg_usbd_init().

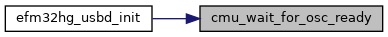

◆ cmu_wait_for_osc_ready()

| void cmu_wait_for_osc_ready | ( | enum cmu_osc | osc | ) |

Wait while oscillator is not ready.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

Definition at line 189 of file cmu.c.

References AUXHFRCO, CMU_STATUS, CMU_STATUS_AUXHFRCORDY, CMU_STATUS_HFRCORDY, CMU_STATUS_HFXORDY, CMU_STATUS_LFRCORDY, CMU_STATUS_LFXORDY, CMU_STATUS_USHFRCORDY, HFRCO, HFXO, LFRCO, LFXO, and USHFRCO.

Referenced by efm32hg_usbd_init().

◆ cmu_wait_for_usbclk_selected()

| void cmu_wait_for_usbclk_selected | ( | enum cmu_osc | osc | ) |

Wait while USBCLK is not selected.

- Parameters

-

[in] osc enum cmu_osc Oscillator name

Definition at line 296 of file cmu.c.

References CMU_STATUS, CMU_STATUS_USBCLFRCOSEL, CMU_STATUS_USBCLFXOSEL, CMU_STATUS_USBCUSHFRCOSEL, LFRCO, LFXO, and USHFRCO.

Referenced by efm32hg_usbd_init().