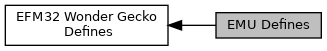

Defined Constants and Types for the Energy Management Unit More...

Detailed Description

Defined Constants and Types for the Energy Management Unit

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ EMU_AUXCTRL

Definition at line 31 of file emu_common.h.

◆ EMU_AUXCTRL_HRCCLR

| #define EMU_AUXCTRL_HRCCLR (1 << 0) |

Definition at line 61 of file emu_common.h.

◆ EMU_BUACT

Definition at line 36 of file emu_common.h.

◆ EMU_BUACT_BUEXRANGE

| #define EMU_BUACT_BUEXRANGE | ( | v | ) | (((v) << EMU_BUACT_BUEXRANGE_SHIFT) & EMU_BUACT_BUEXRANGE_MASK) |

Definition at line 139 of file emu_common.h.

◆ EMU_BUACT_BUEXRANGE_MASK

| #define EMU_BUACT_BUEXRANGE_MASK (0x3 << EMU_BUACT_BUEXRANGE_SHIFT) |

Definition at line 138 of file emu_common.h.

◆ EMU_BUACT_BUEXRANGE_SHIFT

| #define EMU_BUACT_BUEXRANGE_SHIFT (3) |

Definition at line 137 of file emu_common.h.

◆ EMU_BUACT_BUEXTHRES

| #define EMU_BUACT_BUEXTHRES | ( | v | ) | (((v) << EMU_BUACT_BUEXTHRES_SHIFT) & EMU_BUACT_BUEXTHRES_MASK) |

Definition at line 144 of file emu_common.h.

◆ EMU_BUACT_BUEXTHRES_MASK

| #define EMU_BUACT_BUEXTHRES_MASK (0x7 << EMU_BUACT_BUEXTHRES_SHIFT) |

Definition at line 143 of file emu_common.h.

◆ EMU_BUACT_BUEXTHRES_SHIFT

| #define EMU_BUACT_BUEXTHRES_SHIFT (0) |

Definition at line 142 of file emu_common.h.

◆ EMU_BUACT_PWRCON

| #define EMU_BUACT_PWRCON | ( | v | ) | (((v) << EMU_BUACT_PWRCON_SHIFT) & EMU_BUACT_PWRCON_MASK) |

Definition at line 130 of file emu_common.h.

◆ EMU_BUACT_PWRCON_BUMAIN

| #define EMU_BUACT_PWRCON_BUMAIN 1 |

Definition at line 133 of file emu_common.h.

◆ EMU_BUACT_PWRCON_MAINBU

| #define EMU_BUACT_PWRCON_MAINBU 2 |

Definition at line 134 of file emu_common.h.

◆ EMU_BUACT_PWRCON_MASK

| #define EMU_BUACT_PWRCON_MASK (0x3 << EMU_BUACT_PWRCON_SHIFT) |

Definition at line 129 of file emu_common.h.

◆ EMU_BUACT_PWRCON_NODIODE

| #define EMU_BUACT_PWRCON_NODIODE 3 |

Definition at line 135 of file emu_common.h.

◆ EMU_BUACT_PWRCON_NONE

| #define EMU_BUACT_PWRCON_NONE 0 |

Definition at line 132 of file emu_common.h.

◆ EMU_BUACT_PWRCON_SHIFT

| #define EMU_BUACT_PWRCON_SHIFT (5) |

Definition at line 128 of file emu_common.h.

◆ EMU_BUBODBUVINCAL

Definition at line 43 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_RANGE

| #define EMU_BUBODBUVINCAL_RANGE | ( | v | ) |

Definition at line 168 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_RANGE_MASK

| #define EMU_BUBODBUVINCAL_RANGE_MASK (0x3 << EMU_BUBODBUVINCAL_RANGE_SHIFT) |

Definition at line 167 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_RANGE_SHIFT

| #define EMU_BUBODBUVINCAL_RANGE_SHIFT (3) |

Definition at line 166 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_THRES

| #define EMU_BUBODBUVINCAL_THRES | ( | v | ) |

Definition at line 174 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_THRES_MASK

| #define EMU_BUBODBUVINCAL_THRES_MASK (0x7 << EMU_BUBODBUVINCAL_THRES_SHIFT) |

Definition at line 173 of file emu_common.h.

◆ EMU_BUBODBUVINCAL_THRES_SHIFT

| #define EMU_BUBODBUVINCAL_THRES_SHIFT (0) |

Definition at line 172 of file emu_common.h.

◆ EMU_BUBODUNREGCAL

Definition at line 44 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_RANGE

| #define EMU_BUBODUNREGCAL_RANGE | ( | v | ) |

Definition at line 181 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_RANGE_MASK

| #define EMU_BUBODUNREGCAL_RANGE_MASK (0x3 << EMU_BUBODUNREGCAL_RANGE_SHIFT) |

Definition at line 180 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_RANGE_SHIFT

| #define EMU_BUBODUNREGCAL_RANGE_SHIFT (3) |

Definition at line 179 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_THRES

| #define EMU_BUBODUNREGCAL_THRES | ( | v | ) |

Definition at line 187 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_THRES_MASK

| #define EMU_BUBODUNREGCAL_THRES_MASK (0x7 << EMU_BUBODUNREGCAL_THRES_SHIFT) |

Definition at line 186 of file emu_common.h.

◆ EMU_BUBODUNREGCAL_THRES_SHIFT

| #define EMU_BUBODUNREGCAL_THRES_SHIFT (0) |

Definition at line 185 of file emu_common.h.

◆ EMU_BUCTRL

Definition at line 33 of file emu_common.h.

◆ EMU_BUCTRL_BODCAL

| #define EMU_BUCTRL_BODCAL (1 << 2) |

Definition at line 89 of file emu_common.h.

◆ EMU_BUCTRL_BUMODEBODEN

| #define EMU_BUCTRL_BUMODEBODEN (1 << 3) |

Definition at line 88 of file emu_common.h.

◆ EMU_BUCTRL_EN

| #define EMU_BUCTRL_EN (1 << 0) |

Definition at line 91 of file emu_common.h.

◆ EMU_BUCTRL_PROBE

| #define EMU_BUCTRL_PROBE | ( | v | ) | (((v) << EMU_BUCTRL_PROBE_SHIFT) & EMU_BUCTRL_PROBE_MASK) |

Definition at line 81 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_BUIN

| #define EMU_BUCTRL_PROBE_BUIN 2 |

Definition at line 85 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_BUOUT

| #define EMU_BUCTRL_PROBE_BUOUT 3 |

Definition at line 86 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_DISABLE

| #define EMU_BUCTRL_PROBE_DISABLE 0 |

Definition at line 83 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_MASK

| #define EMU_BUCTRL_PROBE_MASK (0x3 << EMU_BUCTRL_PROBE_SHIFT) |

Definition at line 80 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_SHIFT

| #define EMU_BUCTRL_PROBE_SHIFT (5) |

Definition at line 79 of file emu_common.h.

◆ EMU_BUCTRL_PROBE_VDDDREG

| #define EMU_BUCTRL_PROBE_VDDDREG 1 |

Definition at line 84 of file emu_common.h.

◆ EMU_BUCTRL_STATEN

| #define EMU_BUCTRL_STATEN (1 << 1) |

Definition at line 90 of file emu_common.h.

◆ EMU_BUINACT

Definition at line 35 of file emu_common.h.

◆ EMU_BUINACT_BUENRANGE

| #define EMU_BUINACT_BUENRANGE | ( | v | ) | (((v) << EMU_BUINACT_BUENRANGE_SHIFT) & EMU_BUINACT_BUENRANGE_MASK) |

Definition at line 119 of file emu_common.h.

◆ EMU_BUINACT_BUENRANGE_MASK

| #define EMU_BUINACT_BUENRANGE_MASK (0x3 << EMU_BUINACT_BUENRANGE_SHIFT) |

Definition at line 118 of file emu_common.h.

◆ EMU_BUINACT_BUENRANGE_SHIFT

| #define EMU_BUINACT_BUENRANGE_SHIFT (3) |

Definition at line 117 of file emu_common.h.

◆ EMU_BUINACT_BUENTHRES

| #define EMU_BUINACT_BUENTHRES | ( | v | ) | (((v) << EMU_BUINACT_BUENTHRES_SHIFT) & EMU_BUINACT_BUENTHRES_MASK) |

Definition at line 124 of file emu_common.h.

◆ EMU_BUINACT_BUENTHRES_MASK

| #define EMU_BUINACT_BUENTHRES_MASK (0x7 << EMU_BUINACT_BUENTHRES_SHIFT) |

Definition at line 123 of file emu_common.h.

◆ EMU_BUINACT_BUENTHRES_SHIFT

| #define EMU_BUINACT_BUENTHRES_SHIFT (0) |

Definition at line 122 of file emu_common.h.

◆ EMU_BUINACT_PWRCON

| #define EMU_BUINACT_PWRCON | ( | v | ) | (((v) << EMU_BUINACT_PWRCON_SHIFT) & EMU_BUINACT_PWRCON_MASK) |

Definition at line 110 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_BUMAIN

| #define EMU_BUINACT_PWRCON_BUMAIN 1 |

Definition at line 113 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_MAINBU

| #define EMU_BUINACT_PWRCON_MAINBU 2 |

Definition at line 114 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_MASK

| #define EMU_BUINACT_PWRCON_MASK (0x3 << EMU_BUINACT_PWRCON_SHIFT) |

Definition at line 109 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_NODIODE

| #define EMU_BUINACT_PWRCON_NODIODE 3 |

Definition at line 115 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_NONE

| #define EMU_BUINACT_PWRCON_NONE 0 |

Definition at line 112 of file emu_common.h.

◆ EMU_BUINACT_PWRCON_SHIFT

| #define EMU_BUINACT_PWRCON_SHIFT (5) |

Definition at line 108 of file emu_common.h.

◆ EMU_CTLR_EM4CTRL

| #define EMU_CTLR_EM4CTRL | ( | v | ) | (((v) << EMU_CTRL_EM4CTRL_SHIFT) & EMU_CTRL_EM4CTRL_MASK) |

Definition at line 49 of file emu_common.h.

◆ EMU_CTRL

Definition at line 29 of file emu_common.h.

◆ EMU_CTRL_EM2BLOCK

| #define EMU_CTRL_EM2BLOCK (1 << 1) |

Definition at line 52 of file emu_common.h.

◆ EMU_CTRL_EM4CTRL_MASK

| #define EMU_CTRL_EM4CTRL_MASK (0x3 << EMU_CTRL_EM4CTRL_SHIFT) |

Definition at line 48 of file emu_common.h.

◆ EMU_CTRL_EM4CTRL_SHIFT

| #define EMU_CTRL_EM4CTRL_SHIFT (2) |

Definition at line 47 of file emu_common.h.

◆ EMU_CTRL_EMVREG

| #define EMU_CTRL_EMVREG (1 << 0) |

Definition at line 53 of file emu_common.h.

◆ EMU_EM4CONF

Definition at line 32 of file emu_common.h.

◆ EMU_EM4CONF_BUBODRSTDIS

| #define EMU_EM4CONF_BUBODRSTDIS (1 << 4) |

Definition at line 65 of file emu_common.h.

◆ EMU_EM4CONF_BURTCWU

| #define EMU_EM4CONF_BURTCWU (1 << 1) |

Definition at line 75 of file emu_common.h.

◆ EMU_EM4CONF_LOCKCONF

| #define EMU_EM4CONF_LOCKCONF (1 << 16) |

Definition at line 64 of file emu_common.h.

◆ EMU_EM4CONF_OSC

| #define EMU_EM4CONF_OSC | ( | v | ) | (((v) << EMU_EM4CONF_OSC_SHIFT) & EMU_EM4CONF_OSC_MASK) |

Definition at line 69 of file emu_common.h.

◆ EMU_EM4CONF_OSC_LFRCO

| #define EMU_EM4CONF_OSC_LFRCO 1 |

Definition at line 72 of file emu_common.h.

◆ EMU_EM4CONF_OSC_LFXO

| #define EMU_EM4CONF_OSC_LFXO 2 |

Definition at line 73 of file emu_common.h.

◆ EMU_EM4CONF_OSC_MASK

| #define EMU_EM4CONF_OSC_MASK (0x3 << EMU_EM4CONF_OSC_SHIFT) |

Definition at line 68 of file emu_common.h.

◆ EMU_EM4CONF_OSC_SHIFT

| #define EMU_EM4CONF_OSC_SHIFT (2) |

Definition at line 67 of file emu_common.h.

◆ EMU_EM4CONF_OSC_ULFRCO

| #define EMU_EM4CONF_OSC_ULFRCO 0 |

Definition at line 71 of file emu_common.h.

◆ EMU_EM4CONF_VREGEN

| #define EMU_EM4CONF_VREGEN (1 << 0) |

Definition at line 76 of file emu_common.h.

◆ EMU_IEN

Definition at line 42 of file emu_common.h.

◆ EMU_IEN_BURDY

| #define EMU_IEN_BURDY (1 << 0) |

Definition at line 163 of file emu_common.h.

◆ EMU_IF

Definition at line 39 of file emu_common.h.

◆ EMU_IF_BURDY

| #define EMU_IF_BURDY (1 << 0) |

Definition at line 154 of file emu_common.h.

◆ EMU_IFC

Definition at line 41 of file emu_common.h.

◆ EMU_IFC_BURDY

| #define EMU_IFC_BURDY (1 << 0) |

Definition at line 160 of file emu_common.h.

◆ EMU_IFS

Definition at line 40 of file emu_common.h.

◆ EMU_IFS_BURDY

| #define EMU_IFS_BURDY (1 << 0) |

Definition at line 157 of file emu_common.h.

◆ EMU_LOCK

Definition at line 30 of file emu_common.h.

◆ EMU_LOCK_LOCKKEY_LOCK

| #define EMU_LOCK_LOCKKEY_LOCK (0) |

Definition at line 57 of file emu_common.h.

◆ EMU_LOCK_LOCKKEY_MASK

| #define EMU_LOCK_LOCKKEY_MASK (0xFFFF) |

Definition at line 56 of file emu_common.h.

◆ EMU_LOCK_LOCKKEY_UNLOCK

| #define EMU_LOCK_LOCKKEY_UNLOCK (0xADE8) |

Definition at line 58 of file emu_common.h.

◆ EMU_PWRCONF

Definition at line 34 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES

| #define EMU_PWRCONF_PWRRES | ( | v | ) | (((v) << EMU_PWRCONF_PWRRES_SHIFT) & EMU_PWRCONF_PWRRES_MASK) |

Definition at line 96 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_BUIN

| #define EMU_PWRCONF_PWRRES_BUIN 2 |

Definition at line 100 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_BUOUT

| #define EMU_PWRCONF_PWRRES_BUOUT 3 |

Definition at line 101 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_DISABLE

| #define EMU_PWRCONF_PWRRES_DISABLE 0 |

Definition at line 98 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_MASK

| #define EMU_PWRCONF_PWRRES_MASK (0x3 << EMU_PWRCONF_PWRRES_SHIFT) |

Definition at line 95 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_SHIFT

| #define EMU_PWRCONF_PWRRES_SHIFT (3) |

Definition at line 94 of file emu_common.h.

◆ EMU_PWRCONF_PWRRES_VDDDREG

| #define EMU_PWRCONF_PWRRES_VDDDREG 1 |

Definition at line 99 of file emu_common.h.

◆ EMU_PWRCONF_VOUTMED

| #define EMU_PWRCONF_VOUTMED (1 << 1) |

Definition at line 104 of file emu_common.h.

◆ EMU_PWRCONF_VOUTSTRONG

| #define EMU_PWRCONF_VOUTSTRONG (1 << 2) |

Definition at line 103 of file emu_common.h.

◆ EMU_PWRCONF_VOUTWEAK

| #define EMU_PWRCONF_VOUTWEAK (1 << 0) |

Definition at line 105 of file emu_common.h.

◆ EMU_ROUTE

Definition at line 38 of file emu_common.h.

◆ EMU_ROUTE_BUVINPEN

| #define EMU_ROUTE_BUVINPEN (1 << 0) |

Definition at line 151 of file emu_common.h.

◆ EMU_STATUS

Definition at line 37 of file emu_common.h.

◆ EMU_STATUS_BURDY

| #define EMU_STATUS_BURDY (1 << 0) |

Definition at line 148 of file emu_common.h.