msc_common.h File Reference

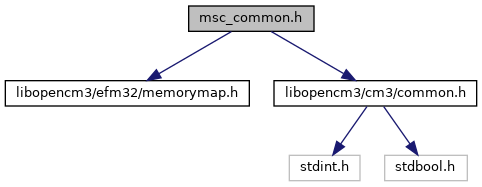

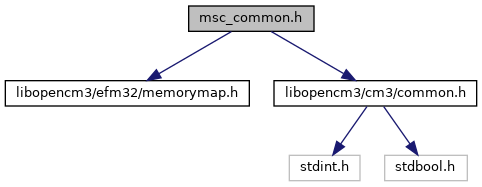

Include dependency graph for msc_common.h:

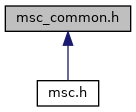

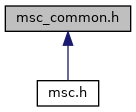

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

|

libopencm3

A free/libre/open-source firmware library for various ARM Cortex-M3 microcontrollers.

|

Go to the source code of this file.