Cortex-M System Control Block

The System Control Block is a section of the System Control Space. More...

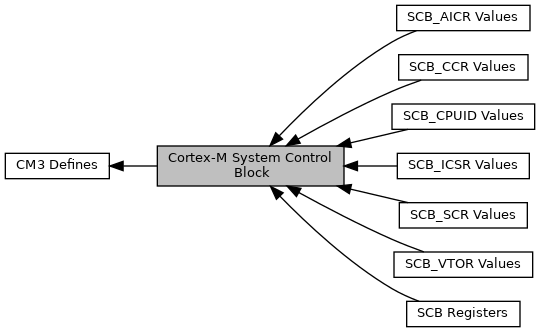

Collaboration diagram for Cortex-M System Control Block:

Data Structures | |

| struct | scb_exception_stack_frame |

Modules | |

| SCB Registers | |

| SCB_CPUID Values | |

| SCB_ICSR Values | |

| SCB_VTOR Values | |

| SCB_AICR Values | |

| SCB_SCR Values | |

| SCB_CCR Values | |

Functions | |

| void | scb_reset_system (void) |

| void | scb_reset_core (void) |

| void | scb_set_priority_grouping (uint32_t prigroup) |

Detailed Description

The System Control Block is a section of the System Control Space.

Other members of the SCS are, for instance, DWT, ITM, SYSTICKK. The exact details of the SCB are defined in the "Architecture Reference Manual" for either ARMv7-M or ARMV6-m.

Macro Definition Documentation

◆ SCB_CFSR_BFARVALID

◆ SCB_CFSR_DACCVIOL

◆ SCB_CFSR_DIVBYZERO

◆ SCB_CFSR_IACCVIOL

◆ SCB_CFSR_IBUSERR

◆ SCB_CFSR_IMPRECISERR

◆ SCB_CFSR_INVPC

◆ SCB_CFSR_INVSTATE

◆ SCB_CFSR_MMARVALID

◆ SCB_CFSR_MSTKERR

◆ SCB_CFSR_MUNSTKERR

◆ SCB_CFSR_NOCP

◆ SCB_CFSR_PRECISERR

◆ SCB_CFSR_STKERR

◆ SCB_CFSR_UNALIGNED

◆ SCB_CFSR_UNDEFINSTR

◆ SCB_CFSR_UNSTKERR

◆ SCB_CPACR_CP10

◆ SCB_CPACR_CP11

◆ SCB_CPACR_FULL

◆ SCB_CPACR_NONE

◆ SCB_CPACR_PRIV

◆ SCB_GET_EXCEPTION_STACK_FRAME

| #define SCB_GET_EXCEPTION_STACK_FRAME | ( | f | ) |

◆ SCB_HFSR_DEBUG_VT

◆ SCB_HFSR_FORCED

◆ SCB_HFSR_VECTTBL

◆ SCB_SHCSR_BUSFAULTACT

◆ SCB_SHCSR_BUSFAULTENA

◆ SCB_SHCSR_BUSFAULTPENDED

◆ SCB_SHCSR_MEMFAULTACT

◆ SCB_SHCSR_MEMFAULTENA

◆ SCB_SHCSR_MEMFAULTPENDED

◆ SCB_SHCSR_MONITORACT

◆ SCB_SHCSR_PENDSVACT

◆ SCB_SHCSR_SVCALLACT

◆ SCB_SHCSR_SVCALLPENDED

◆ SCB_SHCSR_SYSTICKACT

◆ SCB_SHCSR_USGFAULTACT

◆ SCB_SHCSR_USGFAULTENA

◆ SCB_SHCSR_USGFAULTPENDED

◆ SCB_SHPR_PRI_10_RESERVED

◆ SCB_SHPR_PRI_11_SVCALL

◆ SCB_SHPR_PRI_12_RESERVED

◆ SCB_SHPR_PRI_13_RESERVED

◆ SCB_SHPR_PRI_14_PENDSV

◆ SCB_SHPR_PRI_15_SYSTICK

◆ SCB_SHPR_PRI_4_MEMMANAGE

◆ SCB_SHPR_PRI_5_BUSFAULT

◆ SCB_SHPR_PRI_6_USAGEFAULT

◆ SCB_SHPR_PRI_7_RESERVED

◆ SCB_SHPR_PRI_8_RESERVED

◆ SCB_SHPR_PRI_9_RESERVED

Function Documentation

◆ scb_reset_core()

| void scb_reset_core | ( | void | ) |

Definition at line 46 of file scb.c.

References SCB_AIRCR, SCB_AIRCR_VECTKEY, and SCB_AIRCR_VECTRESET.

◆ scb_reset_system()

| void scb_reset_system | ( | void | ) |

Definition at line 54 of file scb.c.

References SCB_AIRCR, SCB_AIRCR_SYSRESETREQ, and SCB_AIRCR_VECTKEY.

◆ scb_set_priority_grouping()

| void scb_set_priority_grouping | ( | uint32_t | prigroup | ) |

Definition at line 63 of file scb.c.

References SCB_AIRCR, and SCB_AIRCR_VECTKEY.