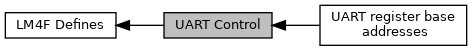

Defined Constants and Types for the LM4F UART Control More...

Modules | |

| UART register base addresses | |

Macros | |

| #define | UART_DR(uart_base) MMIO32((uart_base) + 0x00) |

| #define | UART_RSR(uart_base) MMIO32((uart_base) + 0x04) |

| #define | UART_ECR(uart_base) MMIO32((uart_base) + 0x04) |

| #define | UART_FR(uart_base) MMIO32((uart_base) + 0x18) |

| #define | UART_ILPR(uart_base) MMIO32((uart_base) + 0x20) |

| #define | UART_IBRD(uart_base) MMIO32((uart_base) + 0x24) |

| #define | UART_FBRD(uart_base) MMIO32((uart_base) + 0x28) |

| #define | UART_LCRH(uart_base) MMIO32((uart_base) + 0x2C) |

| #define | UART_CTL(uart_base) MMIO32((uart_base) + 0x30) |

| #define | UART_IFLS(uart_base) MMIO32((uart_base) + 0x34) |

| #define | UART_IM(uart_base) MMIO32((uart_base) + 0x38) |

| #define | UART_RIS(uart_base) MMIO32((uart_base) + 0x3C) |

| #define | UART_MIS(uart_base) MMIO32((uart_base) + 0x40) |

| #define | UART_ICR(uart_base) MMIO32((uart_base) + 0x44) |

| #define | UART_DMACTL(uart_base) MMIO32((uart_base) + 0x48) |

| #define | UART_LCTL(uart_base) MMIO32((uart_base) + 0x90) |

| #define | UART_LSS(uart_base) MMIO32((uart_base) + 0x94) |

| #define | UART_LTIM(uart_base) MMIO32((uart_base) + 0x98) |

| #define | UART_9BITADDR(uart_base) MMIO32((uart_base) + 0xA4) |

| #define | UART_9BITAMASK(uart_base) MMIO32((uart_base) + 0xA8) |

| #define | UART_PP(uart_base) MMIO32((uart_base) + 0xFC0) |

| #define | UART_CC(uart_base) MMIO32((uart_base) + 0xFC8) |

| #define | UART_PERIPH_ID4(uart_base) MMIO32((uart_base) + 0xFD0) |

| #define | UART_PERIPH_ID5(uart_base) MMIO32((uart_base) + 0xFD4) |

| #define | UART_PERIPH_ID6(uart_base) MMIO32((uart_base) + 0xFD8) |

| #define | UART_PERIPH_ID7(uart_base) MMIO32((uart_base) + 0xFDC) |

| #define | UART_PERIPH_ID0(uart_base) MMIO32((uart_base) + 0xFE0) |

| #define | UART_PERIPH_ID1(uart_base) MMIO32((uart_base) + 0xFE4) |

| #define | UART_PERIPH_ID2(uart_base) MMIO32((uart_base) + 0xFE8) |

| #define | UART_PERIPH_ID3(uart_base) MMIO32((uart_base) + 0xFEC) |

| #define | UART_PCELL_ID0(uart_base) MMIO32((uart_base) + 0xFF0) |

| #define | UART_PCELL_ID1(uart_base) MMIO32((uart_base) + 0xFF4) |

| #define | UART_PCELL_ID2(uart_base) MMIO32((uart_base) + 0xFF8) |

| #define | UART_PCELL_ID3(uart_base) MMIO32((uart_base) + 0xFFC) |

| #define | UART_DR_OE (1 << 11) |

| Overrun Error. More... | |

| #define | UART_DR_BE (1 << 10) |

| Break Error. More... | |

| #define | UART_DR_PE (1 << 9) |

| Parity Error. More... | |

| #define | UART_DR_FE (1 << 8) |

| Framing Error. More... | |

| #define | UART_DR_DATA_MASK (0xFF << 0) |

| Data transmitted or received. More... | |

| #define | UART_RSR_OE (1 << 3) |

| Overrun Error. More... | |

| #define | UART_RSR_BE (1 << 2) |

| Break Error. More... | |

| #define | UART_RSR_PE (1 << 1) |

| Parity Error. More... | |

| #define | UART_RSR_FE (1 << 0) |

| Framing Error. More... | |

| #define | UART_FR_TXFE (1 << 7) |

| Tx FIFO empty. More... | |

| #define | UART_FR_RXFF (1 << 6) |

| Rx FIFO full. More... | |

| #define | UART_FR_TXFF (1 << 5) |

| Tx FIFO full. More... | |

| #define | UART_FR_RXFE (1 << 4) |

| Rx FIFO empty. More... | |

| #define | UART_FR_BUSY (1 << 3) |

| UART Busy. More... | |

| #define | UART_FR_CTS (1 << 0) |

| Clear To Send. More... | |

| #define | UART_LCRH_SPS (1 << 7) |

| Stick parity select. More... | |

| #define | UART_LCRH_WLEN_MASK (3 << 5) |

| Word length. More... | |

| #define | UART_LCRH_WLEN_5 (0 << 5) |

| #define | UART_LCRH_WLEN_6 (1 << 5) |

| #define | UART_LCRH_WLEN_7 (2 << 5) |

| #define | UART_LCRH_WLEN_8 (3 << 5) |

| #define | UART_LCRH_FEN (1 << 4) |

| Enable FIFOs. More... | |

| #define | UART_LCRH_STP2 (1 << 3) |

| Two stop bits select. More... | |

| #define | UART_LCRH_EPS (1 << 2) |

| Even parity select. More... | |

| #define | UART_LCRH_PEN (1 << 1) |

| Parity enable. More... | |

| #define | UART_LCRH_BRK (1 << 0) |

| Send break. More... | |

| #define | UART_CTL_CTSEN (1 << 15) |

| Enable Clear To Send. More... | |

| #define | UART_CTL_RTSEN (1 << 14) |

| Enable Request To Send. More... | |

| #define | UART_CTL_RTS (1 << 11) |

| Request To Send. More... | |

| #define | UART_CTL_DTR (1 << 10) |

| Data terminal ready. More... | |

| #define | UART_CTL_RXE (1 << 9) |

| Rx Enable. More... | |

| #define | UART_CTL_TXE (1 << 8) |

| Tx Enable. More... | |

| #define | UART_CTL_LBE (1 << 7) |

| Loop back enable. More... | |

| #define | UART_CTL_LIN (1 << 6) |

| LIN mode enable. More... | |

| #define | UART_CTL_HSE (1 << 5) |

| High speed Enable. More... | |

| #define | UART_CTL_EOT (1 << 4) |

| End of transmission. More... | |

| #define | UART_CTL_SMART (1 << 3) |

| ISO 7816 Smart Card support. More... | |

| #define | UART_CTL_SIRLIP (1 << 2) |

| SIR low-power mode. More... | |

| #define | UART_CTL_SIREN (1 << 1) |

| SIR enable. More... | |

| #define | UART_CTL_UARTEN (1 << 0) |

| UART enable. More... | |

| #define | UART_IFLS_RXIFLSEL_MASK (7 << 3) |

| UART Rx interrupt FIFO level select. More... | |

| #define | UART_IFLS_RXIFLSEL_1_8 (0 << 3) |

| #define | UART_IFLS_RXIFLSEL_1_4 (1 << 3) |

| #define | UART_IFLS_RXIFLSEL_1_2 (2 << 3) |

| #define | UART_IFLS_RXIFLSEL_3_4 (3 << 3) |

| #define | UART_IFLS_RXIFLSEL_7_8 (4 << 3) |

| #define | UART_IFLS_TXIFLSEL_MASK (7 << 0) |

| UART Tx interrupt FIFO level select. More... | |

| #define | UART_IFLS_TXIFLSEL_7_8 (0 << 0) |

| #define | UART_IFLS_TXIFLSEL_3_4 (1 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_2 (2 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_4 (3 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_8 (4 << 0) |

| #define | UART_IM_LME5IM (1 << 15) |

| LIN mode edge 5 interrupt mask. More... | |

| #define | UART_IM_LME1IM (1 << 14) |

| LIN mode edge 1 interrupt mask. More... | |

| #define | UART_IM_LMSBIM (1 << 13) |

| LIN mode sync break interrupt mask. More... | |

| #define | UART_IM_9BITIM (1 << 12) |

| 9-bit mode interrupt mask More... | |

| #define | UART_IM_OEIM (1 << 10) |

| Overrun error interrupt mask. More... | |

| #define | UART_IM_BEIM (1 << 9) |

| Break error interrupt mask. More... | |

| #define | UART_IM_PEIM (1 << 8) |

| Parity error interrupt mask. More... | |

| #define | UART_IM_FEIM (1 << 7) |

| Framing error interrupt mask. More... | |

| #define | UART_IM_RTIM (1 << 6) |

| Receive time-out interrupt mask. More... | |

| #define | UART_IM_TXIM (1 << 5) |

| Transmit interrupt mask. More... | |

| #define | UART_IM_RXIM (1 << 4) |

| Receive interrupt mask. More... | |

| #define | UART_IM_DSRIM (1 << 3) |

| Data Set Ready modem interrupt mask. More... | |

| #define | UART_IM_DCDIM (1 << 2) |

| Data Carrier Detect modem interrupt mask. More... | |

| #define | UART_IM_CTSIM (1 << 1) |

| Clear To Send modem interrupt mask. More... | |

| #define | UART_IM_RIIM (1 << 0) |

| Ring Indicator modem interrupt mask. More... | |

| #define | UART_DMACTL_DMAERR (1 << 2) |

| DMA on error. More... | |

| #define | UART_DMACTL_TXDMAE (1 << 1) |

| Transmit DMA enable. More... | |

| #define | UART_DMACTL_RXDMAE (1 << 0) |

| Receive DMA enable. More... | |

| #define | UART_LCTL_BLEN_MASK (3 << 4) |

| Sync break length. More... | |

| #define | UART_LCTL_BLEN_16T (3 << 4) |

| #define | UART_LCTL_BLEN_15T (2 << 4) |

| #define | UART_LCTL_BLEN_14T (1 << 4) |

| #define | UART_LCTL_BLEN_13T (0 << 4) |

| #define | UART_LCTL_MASTER (1 << 0) |

| LIN master enable. More... | |

| #define | UART_UART_9BITADDR_9BITEN (1 << 15) |

| Enable 9-bit mode. More... | |

| #define | UART_UART_9BITADDR_ADDR_MASK (0xFF << 0) |

| Self-address for 9-bit mode. More... | |

| #define | UART_UART_PP_NB (1 << 1) |

| 9-bit support More... | |

| #define | UART_UART_PP_SC (1 << 0) |

| Smart Card support. More... | |

| #define | UART_CC_CS_MASK (0xF << 0) |

| UART baud clock source. More... | |

| #define | UART_CC_CS_SYSCLK (0x0 << 0) |

| #define | UART_CC_CS_PIOSC (0x5 << 0) |

Enumerations | |

| enum | uart_parity { UART_PARITY_NONE , UART_PARITY_ODD , UART_PARITY_EVEN , UART_PARITY_STICK_0 , UART_PARITY_STICK_1 } |

| enum | uart_flowctl { UART_FLOWCTL_NONE , UART_FLOWCTL_RTS , UART_FLOWCTL_CTS , UART_FLOWCTL_RTS_CTS } |

| enum | uart_interrupt_flag { UART_INT_LME5 = UART_IM_LME5IM , UART_INT_LME1 = UART_IM_LME1IM , UART_INT_LMSB = UART_IM_LMSBIM , UART_INT_9BIT = UART_IM_9BITIM , UART_INT_OE = UART_IM_OEIM , UART_INT_BE = UART_IM_BEIM , UART_INT_PE = UART_IM_PEIM , UART_INT_FE = UART_IM_FEIM , UART_INT_RT = UART_IM_RTIM , UART_INT_TX = UART_IM_TXIM , UART_INT_RX = UART_IM_RXIM , UART_INT_DSR = UART_IM_DSRIM , UART_INT_DCD = UART_IM_DCDIM , UART_INT_CTS = UART_IM_CTSIM , UART_INT_RI = UART_IM_RIIM } |

| UART interrupt masks. More... | |

| enum | uart_fifo_rx_trigger_level { UART_FIFO_RX_TRIG_1_8 = UART_IFLS_RXIFLSEL_1_8 , UART_FIFO_RX_TRIG_1_4 = UART_IFLS_RXIFLSEL_1_4 , UART_FIFO_RX_TRIG_1_2 = UART_IFLS_RXIFLSEL_1_2 , UART_FIFO_RX_TRIG_3_4 = UART_IFLS_RXIFLSEL_3_4 , UART_FIFO_RX_TRIG_7_8 = UART_IFLS_RXIFLSEL_7_8 } |

| UART RX FIFO interrupt trigger levels. More... | |

| enum | uart_fifo_tx_trigger_level { UART_FIFO_TX_TRIG_7_8 = UART_IFLS_TXIFLSEL_7_8 , UART_FIFO_TX_TRIG_3_4 = UART_IFLS_TXIFLSEL_3_4 , UART_FIFO_TX_TRIG_1_2 = UART_IFLS_TXIFLSEL_1_2 , UART_FIFO_TX_TRIG_1_4 = UART_IFLS_TXIFLSEL_1_4 , UART_FIFO_TX_TRIG_1_8 = UART_IFLS_TXIFLSEL_1_8 } |

| UART TX FIFO interrupt trigger levels. More... | |

Functions | |

| void | uart_set_baudrate (uint32_t uart, uint32_t baud) |

| Set UART baudrate. More... | |

| void | uart_set_databits (uint32_t uart, uint8_t databits) |

| Set UART databits. More... | |

| void | uart_set_stopbits (uint32_t uart, uint8_t stopbits) |

| Set UART stopbits. More... | |

| void | uart_set_parity (uint32_t uart, enum uart_parity parity) |

| Set UART parity. More... | |

| void | uart_set_mode (uint32_t uart, uint32_t mode) |

| void | uart_set_flow_control (uint32_t uart, enum uart_flowctl flow) |

| Set the flow control scheme. More... | |

| void | uart_enable (uint32_t uart) |

| Enable the UART. More... | |

| void | uart_disable (uint32_t uart) |

| Disable the UART. More... | |

| void | uart_clock_from_piosc (uint32_t uart) |

| Clock the UART module from the internal oscillator. More... | |

| void | uart_clock_from_sysclk (uint32_t uart) |

| Clock the UART module from the system clock. More... | |

| void | uart_send (uint32_t uart, uint16_t data) |

| UART Send a Data Word. More... | |

| uint16_t | uart_recv (uint32_t uart) |

| UART Read a Received Data Word. More... | |

| void | uart_wait_send_ready (uint32_t uart) |

| UART Wait for Transmit Data Buffer Not Full. More... | |

| void | uart_wait_recv_ready (uint32_t uart) |

| UART Wait for Received Data Available. More... | |

| void | uart_send_blocking (uint32_t uart, uint16_t data) |

| UART Send Data Word with Blocking. More... | |

| uint16_t | uart_recv_blocking (uint32_t uart) |

| UART Read a Received Data Word with Blocking. More... | |

| void | uart_enable_rx_dma (uint32_t uart) |

| Enable the UART Receive DMA. More... | |

| void | uart_disable_rx_dma (uint32_t uart) |

| Disable the UART Receive DMA. More... | |

| void | uart_enable_tx_dma (uint32_t uart) |

| Enable the UART Transmit DMA. More... | |

| void | uart_disable_tx_dma (uint32_t uart) |

| Disable the UART Transmit DMA. More... | |

| void | uart_enable_fifo (uint32_t uart) |

| Enable FIFO for the UART. More... | |

| void | uart_disable_fifo (uint32_t uart) |

| Disable FIFO for the UART. More... | |

| void | uart_set_fifo_trigger_levels (uint32_t uart, enum uart_fifo_rx_trigger_level rx_level, enum uart_fifo_tx_trigger_level tx_level) |

| Set the FIFO trigger levels. More... | |

| void | uart_enable_interrupts (uint32_t uart, enum uart_interrupt_flag ints) |

| Enable Specific UART Interrupts. More... | |

| void | uart_disable_interrupts (uint32_t uart, enum uart_interrupt_flag ints) |

| Enable Specific UART Interrupts. More... | |

| void | uart_enable_rx_interrupt (uint32_t uart) |

| Enable the UART Receive Interrupt. More... | |

| void | uart_disable_rx_interrupt (uint32_t uart) |

| Disable the UART Receive Interrupt. More... | |

| void | uart_enable_tx_interrupt (uint32_t uart) |

| Enable the UART Transmit Interrupt. More... | |

| void | uart_disable_tx_interrupt (uint32_t uart) |

| Disable the UART Transmit Interrupt. More... | |

| void | uart_clear_interrupt_flag (uint32_t uart, enum uart_interrupt_flag ints) |

| Mark interrupt as serviced. More... | |

| static bool | uart_is_tx_fifo_empty (uint32_t uart) |

| Determine if the TX fifo is empty. More... | |

| static bool | uart_is_rx_fifo_full (uint32_t uart) |

| Determine if the RX fifo is full. More... | |

| static bool | uart_is_rx_fifo_empty (uint32_t uart) |

| Determine if the RX fifo is empty. More... | |

Detailed Description

Defined Constants and Types for the LM4F UART Control

- Version

- 1.0.0

- Date

- 07 May 2013

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ UART_9BITADDR

| #define UART_9BITADDR | ( | uart_base | ) | MMIO32((uart_base) + 0xA4) |

◆ UART_9BITAMASK

| #define UART_9BITAMASK | ( | uart_base | ) | MMIO32((uart_base) + 0xA8) |

◆ UART_CC

◆ UART_CC_CS_MASK

◆ UART_CC_CS_PIOSC

◆ UART_CC_CS_SYSCLK

◆ UART_CTL

◆ UART_CTL_CTSEN

◆ UART_CTL_DTR

◆ UART_CTL_EOT

◆ UART_CTL_HSE

◆ UART_CTL_LBE

◆ UART_CTL_LIN

◆ UART_CTL_RTS

◆ UART_CTL_RTSEN

◆ UART_CTL_RXE

◆ UART_CTL_SIREN

◆ UART_CTL_SIRLIP

◆ UART_CTL_SMART

◆ UART_CTL_TXE

◆ UART_CTL_UARTEN

◆ UART_DMACTL

◆ UART_DMACTL_DMAERR

◆ UART_DMACTL_RXDMAE

◆ UART_DMACTL_TXDMAE

◆ UART_DR

◆ UART_DR_BE

◆ UART_DR_DATA_MASK

| #define UART_DR_DATA_MASK (0xFF << 0) |

◆ UART_DR_FE

◆ UART_DR_OE

◆ UART_DR_PE

◆ UART_ECR

◆ UART_FBRD

◆ UART_FR

◆ UART_FR_BUSY

◆ UART_FR_CTS

◆ UART_FR_RXFE

◆ UART_FR_RXFF

◆ UART_FR_TXFE

◆ UART_FR_TXFF

◆ UART_IBRD

◆ UART_ICR

◆ UART_IFLS

◆ UART_IFLS_RXIFLSEL_1_2

◆ UART_IFLS_RXIFLSEL_1_4

◆ UART_IFLS_RXIFLSEL_1_8

◆ UART_IFLS_RXIFLSEL_3_4

◆ UART_IFLS_RXIFLSEL_7_8

◆ UART_IFLS_RXIFLSEL_MASK

| #define UART_IFLS_RXIFLSEL_MASK (7 << 3) |

◆ UART_IFLS_TXIFLSEL_1_2

◆ UART_IFLS_TXIFLSEL_1_4

◆ UART_IFLS_TXIFLSEL_1_8

◆ UART_IFLS_TXIFLSEL_3_4

◆ UART_IFLS_TXIFLSEL_7_8

◆ UART_IFLS_TXIFLSEL_MASK

| #define UART_IFLS_TXIFLSEL_MASK (7 << 0) |

◆ UART_ILPR

◆ UART_IM

◆ UART_IM_9BITIM

◆ UART_IM_BEIM

◆ UART_IM_CTSIM

| #define UART_IM_CTSIM (1 << 1) |

◆ UART_IM_DCDIM

| #define UART_IM_DCDIM (1 << 2) |

◆ UART_IM_DSRIM

| #define UART_IM_DSRIM (1 << 3) |

◆ UART_IM_FEIM

◆ UART_IM_LME1IM

| #define UART_IM_LME1IM (1 << 14) |

◆ UART_IM_LME5IM

| #define UART_IM_LME5IM (1 << 15) |

◆ UART_IM_LMSBIM

| #define UART_IM_LMSBIM (1 << 13) |

◆ UART_IM_OEIM

◆ UART_IM_PEIM

◆ UART_IM_RIIM

| #define UART_IM_RIIM (1 << 0) |

◆ UART_IM_RTIM

| #define UART_IM_RTIM (1 << 6) |

◆ UART_IM_RXIM

◆ UART_IM_TXIM

◆ UART_LCRH

◆ UART_LCRH_BRK

◆ UART_LCRH_EPS

◆ UART_LCRH_FEN

◆ UART_LCRH_PEN

◆ UART_LCRH_SPS

◆ UART_LCRH_STP2

◆ UART_LCRH_WLEN_5

◆ UART_LCRH_WLEN_6

◆ UART_LCRH_WLEN_7

◆ UART_LCRH_WLEN_8

◆ UART_LCRH_WLEN_MASK

◆ UART_LCTL

◆ UART_LCTL_BLEN_13T

◆ UART_LCTL_BLEN_14T

◆ UART_LCTL_BLEN_15T

◆ UART_LCTL_BLEN_16T

◆ UART_LCTL_BLEN_MASK

◆ UART_LCTL_MASTER

◆ UART_LSS

◆ UART_LTIM

◆ UART_MIS

◆ UART_PCELL_ID0

| #define UART_PCELL_ID0 | ( | uart_base | ) | MMIO32((uart_base) + 0xFF0) |

◆ UART_PCELL_ID1

| #define UART_PCELL_ID1 | ( | uart_base | ) | MMIO32((uart_base) + 0xFF4) |

◆ UART_PCELL_ID2

| #define UART_PCELL_ID2 | ( | uart_base | ) | MMIO32((uart_base) + 0xFF8) |

◆ UART_PCELL_ID3

| #define UART_PCELL_ID3 | ( | uart_base | ) | MMIO32((uart_base) + 0xFFC) |

◆ UART_PERIPH_ID0

| #define UART_PERIPH_ID0 | ( | uart_base | ) | MMIO32((uart_base) + 0xFE0) |

◆ UART_PERIPH_ID1

| #define UART_PERIPH_ID1 | ( | uart_base | ) | MMIO32((uart_base) + 0xFE4) |

◆ UART_PERIPH_ID2

| #define UART_PERIPH_ID2 | ( | uart_base | ) | MMIO32((uart_base) + 0xFE8) |

◆ UART_PERIPH_ID3

| #define UART_PERIPH_ID3 | ( | uart_base | ) | MMIO32((uart_base) + 0xFEC) |

◆ UART_PERIPH_ID4

| #define UART_PERIPH_ID4 | ( | uart_base | ) | MMIO32((uart_base) + 0xFD0) |

◆ UART_PERIPH_ID5

| #define UART_PERIPH_ID5 | ( | uart_base | ) | MMIO32((uart_base) + 0xFD4) |

◆ UART_PERIPH_ID6

| #define UART_PERIPH_ID6 | ( | uart_base | ) | MMIO32((uart_base) + 0xFD8) |

◆ UART_PERIPH_ID7

| #define UART_PERIPH_ID7 | ( | uart_base | ) | MMIO32((uart_base) + 0xFDC) |

◆ UART_PP

◆ UART_RIS

◆ UART_RSR

◆ UART_RSR_BE

◆ UART_RSR_FE

◆ UART_RSR_OE

◆ UART_RSR_PE

◆ UART_UART_9BITADDR_9BITEN

| #define UART_UART_9BITADDR_9BITEN (1 << 15) |

◆ UART_UART_9BITADDR_ADDR_MASK

| #define UART_UART_9BITADDR_ADDR_MASK (0xFF << 0) |

◆ UART_UART_PP_NB

◆ UART_UART_PP_SC

Enumeration Type Documentation

◆ uart_fifo_rx_trigger_level

UART RX FIFO interrupt trigger levels.

The levels indicate how full the FIFO should be before an interrupt is generated. UART_FIFO_RX_TRIG_3_4 means that an interrupt is triggered when the FIFO is 3/4 full. As the FIFO is 8 elements deep, 1/8 is equal to being triggered by a single character.

| Enumerator | |

|---|---|

| UART_FIFO_RX_TRIG_1_8 | |

| UART_FIFO_RX_TRIG_1_4 | |

| UART_FIFO_RX_TRIG_1_2 | |

| UART_FIFO_RX_TRIG_3_4 | |

| UART_FIFO_RX_TRIG_7_8 | |

◆ uart_fifo_tx_trigger_level

UART TX FIFO interrupt trigger levels.

The levels indicate how empty the FIFO should be before an interrupt is generated. Note that this indicates the emptiness of the FIFO and not the fullness. This is somewhat confusing, but it follows the wording of the LM4F120H5QR datasheet.

UART_FIFO_TX_TRIG_3_4 means that an interrupt is triggered when the FIFO is 3/4 empty. As the FIFO is 8 elements deep, 7/8 is equal to being triggered by a single character.

| Enumerator | |

|---|---|

| UART_FIFO_TX_TRIG_7_8 | |

| UART_FIFO_TX_TRIG_3_4 | |

| UART_FIFO_TX_TRIG_1_2 | |

| UART_FIFO_TX_TRIG_1_4 | |

| UART_FIFO_TX_TRIG_1_8 | |

◆ uart_flowctl

| enum uart_flowctl |

◆ uart_interrupt_flag

| enum uart_interrupt_flag |

UART interrupt masks.

These masks can be OR'ed together to specify more than one interrupt. For example, (UART_INT_TXIM | UART_INT_TXIM) specifies both Rx and Tx Interrupt.

◆ uart_parity

| enum uart_parity |

Function Documentation

◆ uart_clear_interrupt_flag()

| void uart_clear_interrupt_flag | ( | uint32_t | uart, |

| enum uart_interrupt_flag | ints | ||

| ) |

Mark interrupt as serviced.

After an interrupt is services, its flag must be cleared. If the flag is not cleared, then execution will jump back to the start of the ISR after the ISR returns.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] ints Interrupts which to clear. Any combination of interrupts may be specified by OR'ing then together

Definition at line 508 of file uart.c.

References UART_ICR.

◆ uart_clock_from_piosc()

| void uart_clock_from_piosc | ( | uint32_t | uart | ) |

Clock the UART module from the internal oscillator.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 238 of file uart.c.

References UART_CC, and UART_CC_CS_PIOSC.

◆ uart_clock_from_sysclk()

| void uart_clock_from_sysclk | ( | uint32_t | uart | ) |

Clock the UART module from the system clock.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 248 of file uart.c.

References UART_CC, and UART_CC_CS_SYSCLK.

◆ uart_disable()

| void uart_disable | ( | uint32_t | uart | ) |

Disable the UART.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 103 of file uart.c.

References UART_CTL.

◆ uart_disable_fifo()

| void uart_disable_fifo | ( | uint32_t | uart | ) |

Disable FIFO for the UART.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 604 of file uart.c.

References UART_LCRH.

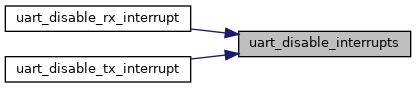

◆ uart_disable_interrupts()

| void uart_disable_interrupts | ( | uint32_t | uart, |

| enum uart_interrupt_flag | ints | ||

| ) |

Enable Specific UART Interrupts.

Disabe any combination of interrupts. Interrupts may be OR'ed together to disable them with one call. For example, to disable both the RX and CTS interrupts, pass (UART_INT_RX | UART_INT_CTS)

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] ints Interrupts which to disable. Any combination of interrupts may be specified by OR'ing then together

Definition at line 446 of file uart.c.

References UART_IM.

Referenced by uart_disable_rx_interrupt(), and uart_disable_tx_interrupt().

◆ uart_disable_rx_dma()

| void uart_disable_rx_dma | ( | uint32_t | uart | ) |

Disable the UART Receive DMA.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 537 of file uart.c.

References UART_DMACTL.

◆ uart_disable_rx_interrupt()

| void uart_disable_rx_interrupt | ( | uint32_t | uart | ) |

Disable the UART Receive Interrupt.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 469 of file uart.c.

References uart_disable_interrupts(), and UART_INT_RX.

◆ uart_disable_tx_dma()

| void uart_disable_tx_dma | ( | uint32_t | uart | ) |

Disable the UART Transmit DMA.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 557 of file uart.c.

References UART_DMACTL.

◆ uart_disable_tx_interrupt()

| void uart_disable_tx_interrupt | ( | uint32_t | uart | ) |

Disable the UART Transmit Interrupt.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 492 of file uart.c.

References uart_disable_interrupts(), and UART_INT_TX.

◆ uart_enable()

| void uart_enable | ( | uint32_t | uart | ) |

Enable the UART.

Enable the UART. The Rx and Tx lines are also enabled.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 93 of file uart.c.

References UART_CTL, UART_CTL_RXE, UART_CTL_TXE, and UART_CTL_UARTEN.

◆ uart_enable_fifo()

| void uart_enable_fifo | ( | uint32_t | uart | ) |

Enable FIFO for the UART.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 594 of file uart.c.

References UART_LCRH, and UART_LCRH_FEN.

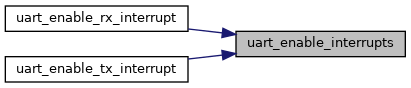

◆ uart_enable_interrupts()

| void uart_enable_interrupts | ( | uint32_t | uart, |

| enum uart_interrupt_flag | ints | ||

| ) |

Enable Specific UART Interrupts.

Enable any combination of interrupts. Interrupts may be OR'ed together to enable them with one call. For example, to enable both the RX and CTS interrupts, pass (UART_INT_RX | UART_INT_CTS)

Note that the NVIC must be enabled and properly configured for the interrupt to be routed to the CPU.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] ints Interrupts which to enable. Any combination of interrupts may be specified by OR'ing then together

Definition at line 430 of file uart.c.

References UART_IM.

Referenced by uart_enable_rx_interrupt(), and uart_enable_tx_interrupt().

◆ uart_enable_rx_dma()

| void uart_enable_rx_dma | ( | uint32_t | uart | ) |

Enable the UART Receive DMA.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 527 of file uart.c.

References UART_DMACTL, and UART_DMACTL_RXDMAE.

◆ uart_enable_rx_interrupt()

| void uart_enable_rx_interrupt | ( | uint32_t | uart | ) |

Enable the UART Receive Interrupt.

Note that the NVIC must be enabled and properly configured for the interrupt to be routed to the CPU.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 459 of file uart.c.

References uart_enable_interrupts(), and UART_INT_RX.

◆ uart_enable_tx_dma()

| void uart_enable_tx_dma | ( | uint32_t | uart | ) |

Enable the UART Transmit DMA.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 547 of file uart.c.

References UART_DMACTL, and UART_DMACTL_TXDMAE.

◆ uart_enable_tx_interrupt()

| void uart_enable_tx_interrupt | ( | uint32_t | uart | ) |

Enable the UART Transmit Interrupt.

Note that the NVIC must be enabled and properly configured for the interrupt to be routed to the CPU.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 482 of file uart.c.

References uart_enable_interrupts(), and UART_INT_TX.

◆ uart_is_rx_fifo_empty()

|

inlinestatic |

Determine if the RX fifo is empty.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 517 of file uart.h.

References UART_FR, and UART_FR_RXFE.

◆ uart_is_rx_fifo_full()

|

inlinestatic |

Determine if the RX fifo is full.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 506 of file uart.h.

References UART_FR, and UART_FR_RXFF.

◆ uart_is_tx_fifo_empty()

|

inlinestatic |

Determine if the TX fifo is empty.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 495 of file uart.h.

References UART_FR, and UART_FR_TXFE.

◆ uart_recv()

| uint16_t uart_recv | ( | uint32_t | uart | ) |

UART Read a Received Data Word.

- Parameters

-

[in] uart UART block register address base UART register base addresses

- Returns

- data from the Rx FIFO.

Definition at line 287 of file uart.c.

References UART_DR, and UART_DR_DATA_MASK.

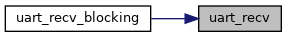

Referenced by uart_recv_blocking().

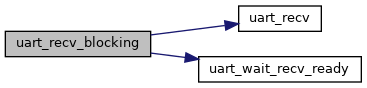

◆ uart_recv_blocking()

| uint16_t uart_recv_blocking | ( | uint32_t | uart | ) |

UART Read a Received Data Word with Blocking.

Wait until a data word has been received then return the word.

- Parameters

-

[in] uart UART block register address base UART register base addresses

- Returns

- data from the Rx FIFO.

Definition at line 344 of file uart.c.

References uart_recv(), and uart_wait_recv_ready().

◆ uart_send()

| void uart_send | ( | uint32_t | uart, |

| uint16_t | data | ||

| ) |

UART Send a Data Word.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] data data to send.

Definition at line 275 of file uart.c.

References UART_DR.

Referenced by uart_send_blocking().

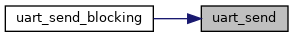

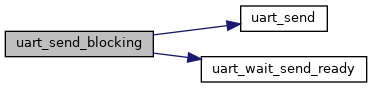

◆ uart_send_blocking()

| void uart_send_blocking | ( | uint32_t | uart, |

| uint16_t | data | ||

| ) |

UART Send Data Word with Blocking.

Blocks until the transmit data FIFO can accept the next data word for transmission.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 330 of file uart.c.

References uart_send(), and uart_wait_send_ready().

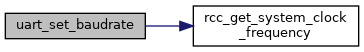

◆ uart_set_baudrate()

| void uart_set_baudrate | ( | uint32_t | uart, |

| uint32_t | baud | ||

| ) |

Set UART baudrate.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] baud Baud rate in bits per second (bps).*

Definition at line 114 of file uart.c.

References rcc_get_system_clock_frequency(), UART_CC, UART_CC_CS_PIOSC, UART_FBRD, and UART_IBRD.

◆ uart_set_databits()

| void uart_set_databits | ( | uint32_t | uart, |

| uint8_t | databits | ||

| ) |

Set UART databits.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] databits number of data bits per transmission.

Definition at line 139 of file uart.c.

References UART_LCRH.

◆ uart_set_fifo_trigger_levels()

| void uart_set_fifo_trigger_levels | ( | uint32_t | uart, |

| enum uart_fifo_rx_trigger_level | rx_level, | ||

| enum uart_fifo_tx_trigger_level | tx_level | ||

| ) |

Set the FIFO trigger levels.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] rx_level Trigger level for RX FIFO [in] tx_level Trigger level for TX FIFO

Definition at line 616 of file uart.c.

References UART_IFLS.

◆ uart_set_flow_control()

| void uart_set_flow_control | ( | uint32_t | uart, |

| enum uart_flowctl | flow | ||

| ) |

Set the flow control scheme.

Set the flow control scheme by enabling or disabling RTS and CTS lines. This will only have effect if the given UART supports the RTS and CTS lines.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] flow The flow control scheme to use (none, RTS, CTS or both)

UART_FLOWCTL_RTS – enable the RTS line

UART_FLOWCTL_CTS – enable the CTS line

UART_FLOWCTL_RTS_CTS – enable both RTS and CTS lines

Definition at line 216 of file uart.c.

References UART_CTL, UART_CTL_CTSEN, UART_CTL_RTSEN, UART_FLOWCTL_CTS, UART_FLOWCTL_RTS, and UART_FLOWCTL_RTS_CTS.

◆ uart_set_mode()

| void uart_set_mode | ( | uint32_t | uart, |

| uint32_t | mode | ||

| ) |

◆ uart_set_parity()

| void uart_set_parity | ( | uint32_t | uart, |

| enum uart_parity | parity | ||

| ) |

Set UART parity.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] bits the requested parity scheme.

Definition at line 175 of file uart.c.

References UART_LCRH, UART_LCRH_EPS, UART_LCRH_PEN, UART_LCRH_SPS, UART_PARITY_EVEN, UART_PARITY_NONE, UART_PARITY_ODD, UART_PARITY_STICK_0, and UART_PARITY_STICK_1.

◆ uart_set_stopbits()

| void uart_set_stopbits | ( | uint32_t | uart, |

| uint8_t | stopbits | ||

| ) |

Set UART stopbits.

- Parameters

-

[in] uart UART block register address base UART register base addresses [in] bits the requested number of stopbits, either 1 or 2.

Definition at line 160 of file uart.c.

References UART_LCRH, and UART_LCRH_STP2.

◆ uart_wait_recv_ready()

| void uart_wait_recv_ready | ( | uint32_t | uart | ) |

UART Wait for Received Data Available.

Blocks until the receive data FIFO holds a at least valid received data word.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 316 of file uart.c.

References UART_FR, and UART_FR_RXFE.

Referenced by uart_recv_blocking().

◆ uart_wait_send_ready()

| void uart_wait_send_ready | ( | uint32_t | uart | ) |

UART Wait for Transmit Data Buffer Not Full.

Blocks until the transmit data FIFO is not empty and can accept the next data word.

Even if the FIFO is not empty, this function will return as long as there is room for at least one more word.

- Parameters

-

[in] uart UART block register address base UART register base addresses

Definition at line 303 of file uart.c.

References UART_FR, and UART_FR_TXFF.

Referenced by uart_send_blocking().