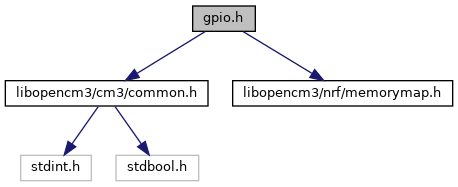

Include dependency graph for common/gpio.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | GPIO (GPIO_BASE) |

| GPIO port. More... | |

| #define | GPIO_OUT MMIO32(GPIO_BASE + 0x504) |

| #define | GPIO_OUTSET MMIO32(GPIO_BASE + 0x508) |

| #define | GPIO_OUTCLR MMIO32(GPIO_BASE + 0x50C) |

| #define | GPIO_IN MMIO32(GPIO_BASE + 0x510) |

| #define | GPIO_DIR MMIO32(GPIO_BASE + 0x514) |

| #define | GPIO_DIRSET MMIO32(GPIO_BASE + 0x518) |

| #define | GPIO_DIRCLR MMIO32(GPIO_BASE + 0x51C) |

| #define | GPIO_PIN_CNF(N) MMIO32(GPIO_BASE + 0x700 + 0x4 * (N)) |

| #define | GPIO_CNF_MODE_MASK 2 |

| #define | GPIO_CNF_MODE_SHIFT 0 |

| #define | GPIO_MODE_INPUT 0 |

| #define | GPIO_MODE_OUTPUT 1 |

| #define | GPIO_MODE_ANALOG 2 |

| #define | GPIO_CNF_PUPD_MASK 2 |

| #define | GPIO_CNF_PUPD_SHIFT 2 |

| #define | GPIO_PUPD_NONE 0x0 |

| #define | GPIO_PUPD_PULLDOWN 0x1 |

| #define | GPIO_PUPD_PULLUP 0x2 |

| #define | GPIO_CNF_DRIVE_SHIFT 8 |

| #define | GPIO_CNF_DRIVE_MASK 7 |

| #define | GPIO_CNF_DRIVE_S0S1 0 |

| Standard 0, standard 1. More... | |

| #define | GPIO_CNF_DRIVE_H0S1 1 |

| High drive 0, standard 1. More... | |

| #define | GPIO_CNF_DRIVE_S0H1 2 |

| Standard 0, high drive 1. More... | |

| #define | GPIO_CNF_DRIVE_H0H1 3 |

| High drive 0, high drive 1. More... | |

| #define | GPIO_CNF_DRIVE_D0S1 4 |

| Disconnect 0, standard 1 (wired-or connections) More... | |

| #define | GPIO_CNF_DRIVE_D0H1 5 |

| Disconnect 0, high drive 1 (wired-or connections) More... | |

| #define | GPIO_CNF_DRIVE_S0D1 6 |

| Standard 0, disconnect 1 (wired-and connections) More... | |

| #define | GPIO_CNF_DRIVE_H0D1 7 |

| High drive 0, disconnect 1 (wired-and connections) More... | |

| #define | GPIO_CNF_SENSE_SHIFT 16 |

| #define | GPIO_CNF_SENSE_MASK 3 |

| #define | GPIO_CNF_SENSE_DISABLE 0 |

| Pin sensing is disabled. More... | |

| #define | GPIO_CNF_SENSE_HIGH 2 |

| Pin sensing is active for high level. More... | |

| #define | GPIO_CNF_SENSE_LOW 3 |

| Pin sensing is active for low level. More... | |

| #define | GPIO_TASK_OUT(n) MMIO32(GPIOTE_BASE + 0x4 * (n)) |

| #define | GPIO_EVENT_IN(n) MMIO32(GPIOTE_BASE + 0x100 + 0x4 * (n)) |

| #define | GPIO_EVENT_PORT MMIO32(GPIOTE_BASE + 0x17C) |

| #define | GPIO_INTEN MMIO32(GPIOTE_BASE + 0x300) |

| #define | GPIO_INTENSET MMIO32(GPIOTE_BASE + 0x304) |

| #define | GPIO_INTENCLR MMIO32(GPIOTE_BASE + 0x308) |

| #define | GPIO_TE_CONFIG(n) MMIO32(GPIOTE_BASE + 0x510 + 0x4 * (n)) |

| #define | GPIO_INTEN_IN(n) (1 << (n)) |

| #define | GPIO_INTEN_PORT (1 << 31) |

| #define | GPIO_TE_CONFIG_MODE_SHIFT 0 |

| #define | GPIO_TE_CONFIG_MODE_MASK 3 |

| #define | GPIO_TE_CONFIG_PSEL_SHIFT 8 |

| #define | GPIO_TE_CONFIG_PSEL_MASK 0x1f |

| #define | GPIO_TE_CONFIG_POLARITY_SHIFT 16 |

| #define | GPIO_TE_CONFIG_POLARITY_MASK 3 |

| #define | GPIO_TE_CONFIG_OUTINIT (1 << 20) |

| #define | GPIO_TE_MODE_DISABLED 0 |

| #define | GPIO_TE_MODE_EVENT 1 |

| #define | GPIO_TE_MODE_TASK 3 |

| #define | GPIO_TE_POLARITY_NONE 0 |

| #define | GPIO_TE_POLARITY_LO_TO_HI 1 |

| #define | GPIO_TE_POLARITY_HI_TO_LO 2 |

| #define | GPIO_TE_POLARITY_TOGGLE 3 |

| #define | GPIO_TE_OUTINIT_LOW 0 |

| #define | GPIO_TE_OUTINIT_HIGH 1 |

| #define | GPIO0 (1 << 0) |

| #define | GPIO1 (1 << 1) |

| #define | GPIO2 (1 << 2) |

| #define | GPIO3 (1 << 3) |

| #define | GPIO4 (1 << 4) |

| #define | GPIO5 (1 << 5) |

| #define | GPIO6 (1 << 6) |

| #define | GPIO7 (1 << 7) |

| #define | GPIO8 (1 << 8) |

| #define | GPIO9 (1 << 9) |

| #define | GPIO10 (1 << 10) |

| #define | GPIO11 (1 << 11) |

| #define | GPIO12 (1 << 12) |

| #define | GPIO13 (1 << 13) |

| #define | GPIO14 (1 << 14) |

| #define | GPIO15 (1 << 15) |

| #define | GPIO16 (1 << 16) |

| #define | GPIO17 (1 << 17) |

| #define | GPIO18 (1 << 18) |

| #define | GPIO19 (1 << 19) |

| #define | GPIO20 (1 << 20) |

| #define | GPIO21 (1 << 21) |

| #define | GPIO22 (1 << 22) |

| #define | GPIO23 (1 << 23) |

| #define | GPIO24 (1 << 24) |

| #define | GPIO25 (1 << 25) |

| #define | GPIO26 (1 << 26) |

| #define | GPIO27 (1 << 27) |

| #define | GPIO28 (1 << 28) |

| #define | GPIO29 (1 << 29) |

| #define | GPIO30 (1 << 30) |

| #define | GPIO31 (1 << 31) |

| #define | GPIO_ALL 0xffffffff |

Functions | |

| void | gpio_set (uint32_t gpioport, uint32_t gpios) |

| Atomic set output. More... | |

| void | gpio_clear (uint32_t gpioport, uint32_t gpios) |

| Atomic clear output. More... | |

| uint32_t | gpio_get (uint32_t gpioport, uint32_t gpios) |

| Read GPIO values. More... | |

| void | gpio_toggle (uint32_t gpioport, uint32_t gpios) |

| Toggle output. More... | |

| void | gpio_mode_setup (uint32_t gpioport, uint32_t mode, uint32_t pull_up_down, uint32_t gpios) |

| Set GPIO Pin Mode. More... | |

| void | gpio_set_options (uint32_t gpioport, uint32_t drive, uint32_t sense, uint32_t gpios) |

| Configure GPIO pin input and output specifics. More... | |

| void | gpio_configure_task (uint8_t task_num, uint8_t pin_num, uint8_t polarity, uint32_t init) |

| Configure Task in GPIO TE Module. More... | |

| void | gpio_configure_event (uint8_t event_num, uint8_t pin_num, uint8_t polarity) |

| Configure Event in GPIO TE Module. More... | |

| void | gpio_enable_interrupts (uint32_t mask) |

| Enable GPIO interrupts. More... | |

| void | gpio_disable_interrupts (uint32_t mask) |

| Disable GPIO interrupts. More... | |

| void | gpio_clear_interrupts (void) |

| Disable all GPIO interrupts. More... | |