mpu.h File Reference

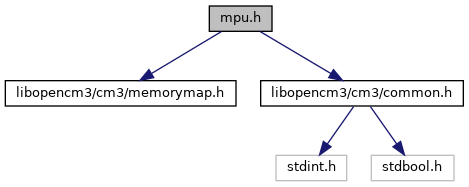

Include dependency graph for mpu.h:

Go to the source code of this file.

Macros | |

| #define | MPU_TYPE MMIO32(MPU_BASE + 0x00) |

| MPU_TYPE is always available, even if the MPU is not implemented. More... | |

| #define | MPU_CTRL MMIO32(MPU_BASE + 0x04) |

| See also MPU CTRL register fields. More... | |

| #define | MPU_RNR MMIO32(MPU_BASE + 0x08) |

| See also MPU RNR register fields. More... | |

| #define | MPU_RBAR MMIO32(MPU_BASE + 0x0C) |

| See also MPU RBAR register fields. More... | |

| #define | MPU_RASR MMIO32(MPU_BASE + 0x10) |

| See also MPU RASR register fields. More... | |

| #define | MPU_TYPE_IREGION_LSB 16 |

| #define | MPU_TYPE_IREGION (0xFF << MPU_TYPE_IREGION_LSB) |

| Number of protected instruction regions; always 0 on v6m/v7m. More... | |

| #define | MPU_TYPE_DREGION_LSB 8 |

| #define | MPU_TYPE_DREGION (0xFF << MPU_TYPE_DREGION_LSB) |

| Number of protected data regions. More... | |

| #define | MPU_TYPE_SEPARATE (1<<0) |

| Indicates if instruction regions are separate from data regions; always 0 on v6m/v7m. More... | |

| #define | MPU_CTRL_PRIVDEFENA (1<<2) |

| Enable default map in privileged mode. More... | |

| #define | MPU_CTRL_HFNMIENA (1<<1) |

| Enable MPU during hard fault, NMI, and FAULTMASK handlers. More... | |

| #define | MPU_CTRL_ENABLE (1<<0) |

| MPU enable. More... | |

| #define | MPU_RNR_REGION_LSB 0 |

| #define | MPU_RNR_REGION (0xFF << MPU_RNR_REGION_LSB) |

| Determines the region affected by RBAR and RASR. More... | |

| #define | MPU_RBAR_ADDR 0xFFFFFFE0 |

| minimum size supported is by writing all ones to ADDR, then reading back More... | |

| #define | MPU_RBAR_VALID (1<<4) |

| Use REGION to determine region to be accessed instead of MPU_RNR. More... | |

| #define | MPU_RBAR_REGION_LSB 0 |

| #define | MPU_RBAR_REGION (0xF << MPU_RBAR_REGION_LSB) |

| Region to change if MPU_RBAR_VALID is set. More... | |

| #define | MPU_RASR_ATTRS_LSB 16 |

| #define | MPU_RASR_ATTRS (0xFFFF << MPU_RASR_ATTRS_LSB) /** Region attributes */ |

| #define | MPU_RASR_SRD_LSB 8 |

| #define | MPU_RASR_SRD (0xFF << MPU_RASR_SRD_LSB) |

| Subregion disable bits. More... | |

| #define | MPU_RASR_SIZE_LSB 1 |

| #define | MPU_RASR_SIZE (0x1F << MPU_RASR_SIZE_LSB) |

| Region size. More... | |

| #define | MPU_RASR_ENABLE (1 << 0) |

| Region enable bit. More... | |

| #define | MPU_RASR_ATTR_XN (1 << 28) |

| Execute never. More... | |

| #define | MPU_RASR_ATTR_AP (7 << 24) |

| Access permissions mask. More... | |

| #define | MPU_RASR_ATTR_AP_PNO_UNO (0 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_AP_PRW_UNO (1 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_AP_PRW_URO (2 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_AP_PRW_URW (3 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_AP_PRO_UNO (5 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_AP_PRO_URO (6 << 24) |

| Priv. More... | |

| #define | MPU_RASR_ATTR_TEX (7 << 19) |

| Type extension (e.g., memory ordering) More... | |

| #define | MPU_RASR_ATTR_S (1 << 18) |

| Shareable. More... | |

| #define | MPU_RASR_ATTR_C (1 << 17) |

| Cacheable. More... | |

| #define | MPU_RASR_ATTR_B (1 << 16) |

| Bufferable. More... | |

| #define | MPU_RASR_ATTR_SCB (7 << 16) |

| SCB mask. More... | |