4l/gpio.h File Reference

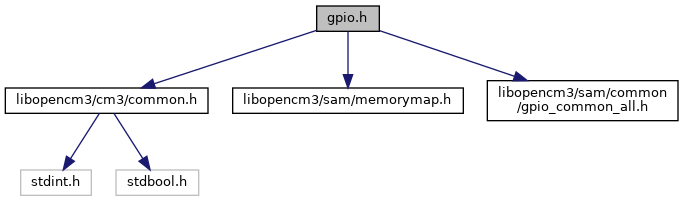

#include <libopencm3/cm3/common.h>#include <libopencm3/sam/memorymap.h>#include <libopencm3/sam/common/gpio_common_all.h>

Include dependency graph for 4l/gpio.h:

Go to the source code of this file.

Macros | |

| #define | GPIOA (GPIO_BASE) |

| #define | GPIOB (GPIO_BASE + 0x200) |

| #define | GPIOC (GPIO_BASE + 0x400) |

| #define | GPIO0 (1 << 0) |

| #define | GPIO1 (1 << 1) |

| #define | GPIO2 (1 << 2) |

| #define | GPIO3 (1 << 3) |

| #define | GPIO4 (1 << 4) |

| #define | GPIO5 (1 << 5) |

| #define | GPIO6 (1 << 6) |

| #define | GPIO7 (1 << 7) |

| #define | GPIO8 (1 << 8) |

| #define | GPIO9 (1 << 9) |

| #define | GPIO10 (1 << 10) |

| #define | GPIO11 (1 << 11) |

| #define | GPIO12 (1 << 12) |

| #define | GPIO13 (1 << 13) |

| #define | GPIO14 (1 << 14) |

| #define | GPIO15 (1 << 15) |

| #define | GPIO16 (1 << 16) |

| #define | GPIO17 (1 << 17) |

| #define | GPIO18 (1 << 18) |

| #define | GPIO19 (1 << 19) |

| #define | GPIO20 (1 << 20) |

| #define | GPIO21 (1 << 21) |

| #define | GPIO22 (1 << 22) |

| #define | GPIO23 (1 << 23) |

| #define | GPIO24 (1 << 24) |

| #define | GPIO25 (1 << 25) |

| #define | GPIO26 (1 << 26) |

| #define | GPIO27 (1 << 27) |

| #define | GPIO28 (1 << 28) |

| #define | GPIO29 (1 << 29) |

| #define | GPIO30 (1 << 30) |

| #define | GPIO31 (1 << 31) |

| #define | GPIO_GPER(X) MMIO32(X) |

| #define | GPIO_GPERS(X) MMIO32((X) + 0x004) |

| #define | GPIO_GPERC(X) MMIO32((X) + 0x008) |

| #define | GPIO_GPERT(X) MMIO32((X) + 0x00C) |

| #define | GPIO_PMR(P, I) MMIO32((P) + (0x10*(1 + (I)))) |

| #define | GPIO_PMR_SETVAL(P, I, S) MMIO32((P) + (0x10*(1 + (I)) + ((S) ? 0x04 : 0x08))) |

| #define | GPIO_PMR0(X) MMIO32((X) + 0x010) |

| #define | GPIO_PMR0S(X) MMIO32((X) + 0x014) |

| #define | GPIO_PMR0C(X) MMIO32((X) + 0x018) |

| #define | GPIO_PMR0T(X) MMIO32((X) + 0x01C) |

| #define | GPIO_PMR1(X) MMIO32((X) + 0x020) |

| #define | GPIO_PMR1S(X) MMIO32((X) + 0x024) |

| #define | GPIO_PMR1C(X) MMIO32((X) + 0x028) |

| #define | GPIO_PMR1T(X) MMIO32((X) + 0x02C) |

| #define | GPIO_PMR2(X) MMIO32((X) + 0x030) |

| #define | GPIO_PMR2S(X) MMIO32((X) + 0x034) |

| #define | GPIO_PMR2C(X) MMIO32((X) + 0x038) |

| #define | GPIO_PMR2T(X) MMIO32((X) + 0x03C) |

| #define | GPIO_ODER(X) MMIO32((X) + 0x040) |

| #define | GPIO_ODERS(X) MMIO32((X) + 0x044) |

| #define | GPIO_ODERC(X) MMIO32((X) + 0x048) |

| #define | GPIO_ODERT(X) MMIO32((X) + 0x04C) |

| #define | GPIO_OVR(X) MMIO32((X) + 0x050) |

| #define | GPIO_OVRS(X) MMIO32((X) + 0x054) |

| #define | GPIO_OVRC(X) MMIO32((X) + 0x058) |

| #define | GPIO_OVRT(X) MMIO32((X) + 0x05C) |

| #define | GPIO_PVR(X) MMIO32((X) + 0x060) |

| #define | GPIO_PUER(X) MMIO32((X) + 0x070) |

| #define | GPIO_PUERS(X) MMIO32((X) + 0x074) |

| #define | GPIO_PUERC(X) MMIO32((X) + 0x078) |

| #define | GPIO_PUERT(X) MMIO32((X) + 0x07C) |

| #define | GPIO_PDER(X) MMIO32((X) + 0x080) |

| #define | GPIO_PDERS(X) MMIO32((X) + 0x084) |

| #define | GPIO_PDERC(X) MMIO32((X) + 0x088) |

| #define | GPIO_PDERT(X) MMIO32((X) + 0x08C) |

| #define | GPIO_IER(X) MMIO32((X) + 0x090) |

| #define | GPIO_IERS(X) MMIO32((X) + 0x094) |

| #define | GPIO_IERC(X) MMIO32((X) + 0x098) |

| #define | GPIO_IERT(X) MMIO32((X) + 0x09C) |

| #define | GPIO_IMR0(X) MMIO32((X) + 0x0A0) |

| #define | GPIO_IMR0S(X) MMIO32((X) + 0x0A4) |

| #define | GPIO_IMR0C(X) MMIO32((X) + 0x0A8) |

| #define | GPIO_IMR0T(X) MMIO32((X) + 0x0AC) |

| #define | GPIO_IMR1(X) MMIO32((X) + 0x0B0) |

| #define | GPIO_IMR1S(X) MMIO32((X) + 0x0B4) |

| #define | GPIO_IMR1C(X) MMIO32((X) + 0x0B8) |

| #define | GPIO_IMR1T(X) MMIO32((X) + 0x0BC) |

| #define | GPIO_GFER(X) MMIO32((X) + 0x0C0) |

| #define | GPIO_GFERS(X) MMIO32((X) + 0x0C4) |

| #define | GPIO_GFERC(X) MMIO32((X) + 0x0C8) |

| #define | GPIO_GFERT(X) MMIO32((X) + 0x0CC) |

| #define | GPIO_IFR(X) MMIO32((X) + 0x0D0) |

| #define | GPIO_IFRC(X) MMIO32((X) + 0x0D8) |

| #define | GPIO_ODCR0(X) MMIO32((X) + 0x100) |

| #define | GPIO_ODCR0S(X) MMIO32((X) + 0x104) |

| #define | GPIO_ODCR0C(X) MMIO32((X) + 0x108) |

| #define | GPIO_ODCR0T(X) MMIO32((X) + 0x10C) |

| #define | GPIO_ODCR1(X) MMIO32((X) + 0x110) |

| #define | GPIO_ODCR1S(X) MMIO32((X) + 0x114) |

| #define | GPIO_ODCR1C(X) MMIO32((X) + 0x118) |

| #define | GPIO_ODCR1T(X) MMIO32((X) + 0x11C) |

| #define | GPIO_OSRR0(X) MMIO32((X) + 0x130) |

| #define | GPIO_OSRR0S(X) MMIO32((X) + 0x134) |

| #define | GPIO_OSRR0C(X) MMIO32((X) + 0x138) |

| #define | GPIO_OSRR0T(X) MMIO32((X) + 0x13C) |

| #define | GPIO_STER(X) MMIO32((X) + 0x160) |

| #define | GPIO_STERS(X) MMIO32((X) + 0x164) |

| #define | GPIO_STERC(X) MMIO32((X) + 0x168) |

| #define | GPIO_STERT(X) MMIO32((X) + 0x16C) |

| #define | GPIO_EVER(X) MMIO32((X) + 0x180) |

| #define | GPIO_EVERS(X) MMIO32((X) + 0x184) |

| #define | GPIO_EVERC(X) MMIO32((X) + 0x188) |

| #define | GPIO_EVERT(X) MMIO32((X) + 0x18C) |

| #define | GPIO_PARAMETER(X) MMIO32((X) + 0x1f8) |

| #define | GPIO_VERSION(X) MMIO32((X) + 0x1fc) |

Enumerations | |

| enum | gpio_mode { GPIO_MODE_A = 0 , GPIO_MODE_B , GPIO_MODE_C , GPIO_MODE_D , GPIO_MODE_E , GPIO_MODE_F , GPIO_MODE_G , GPIO_MODE_H , GPIO_MODE_IN , GPIO_MODE_OUT } |

Functions | |

| void | gpio_enable (uint32_t gpioport, uint32_t gpios, enum gpio_mode mode) |

| Enable output pins. More... | |

| void | gpio_disable (uint32_t gpioport, uint32_t gpios) |

| Disable output pins. More... | |

Macro Definition Documentation

◆ GPIO0

◆ GPIO1

◆ GPIO10

◆ GPIO11

◆ GPIO12

◆ GPIO13

◆ GPIO14

◆ GPIO15

◆ GPIO16

◆ GPIO17

◆ GPIO18

◆ GPIO19

◆ GPIO2

◆ GPIO20

◆ GPIO21

◆ GPIO22

◆ GPIO23

◆ GPIO24

◆ GPIO25

◆ GPIO26

◆ GPIO27

◆ GPIO28

◆ GPIO29

◆ GPIO3

◆ GPIO30

◆ GPIO31

◆ GPIO4

◆ GPIO5

◆ GPIO6

◆ GPIO7

◆ GPIO8

◆ GPIO9

◆ GPIO_EVER

◆ GPIO_EVERC

◆ GPIO_EVERS

◆ GPIO_EVERT

◆ GPIO_GFER

◆ GPIO_GFERC

◆ GPIO_GFERS

◆ GPIO_GFERT

◆ GPIO_GPER

◆ GPIO_GPERC

◆ GPIO_GPERS

◆ GPIO_GPERT

◆ GPIO_IER

◆ GPIO_IERC

◆ GPIO_IERS

◆ GPIO_IERT

◆ GPIO_IFR

◆ GPIO_IFRC

◆ GPIO_IMR0

◆ GPIO_IMR0C

◆ GPIO_IMR0S

◆ GPIO_IMR0T

◆ GPIO_IMR1

◆ GPIO_IMR1C

◆ GPIO_IMR1S

◆ GPIO_IMR1T

◆ GPIO_ODCR0

◆ GPIO_ODCR0C

◆ GPIO_ODCR0S

◆ GPIO_ODCR0T

◆ GPIO_ODCR1

◆ GPIO_ODCR1C

◆ GPIO_ODCR1S

◆ GPIO_ODCR1T

◆ GPIO_ODER

◆ GPIO_ODERC

◆ GPIO_ODERS

◆ GPIO_ODERT

◆ GPIO_OSRR0

◆ GPIO_OSRR0C

◆ GPIO_OSRR0S

◆ GPIO_OSRR0T

◆ GPIO_OVR

◆ GPIO_OVRC

◆ GPIO_OVRS

◆ GPIO_OVRT

◆ GPIO_PARAMETER

◆ GPIO_PDER

◆ GPIO_PDERC

◆ GPIO_PDERS

◆ GPIO_PDERT

◆ GPIO_PMR

◆ GPIO_PMR0

◆ GPIO_PMR0C

◆ GPIO_PMR0S

◆ GPIO_PMR0T

◆ GPIO_PMR1

◆ GPIO_PMR1C

◆ GPIO_PMR1S

◆ GPIO_PMR1T

◆ GPIO_PMR2

◆ GPIO_PMR2C

◆ GPIO_PMR2S

◆ GPIO_PMR2T

◆ GPIO_PMR_SETVAL

| #define GPIO_PMR_SETVAL | ( | P, | |

| I, | |||

| S | |||

| ) | MMIO32((P) + (0x10*(1 + (I)) + ((S) ? 0x04 : 0x08))) |

◆ GPIO_PUER

◆ GPIO_PUERC

◆ GPIO_PUERS

◆ GPIO_PUERT

◆ GPIO_PVR

◆ GPIO_STER

◆ GPIO_STERC

◆ GPIO_STERS

◆ GPIO_STERT

◆ GPIO_VERSION

◆ GPIOA

◆ GPIOB

◆ GPIOC

Enumeration Type Documentation

◆ gpio_mode

| enum gpio_mode |

Function Documentation

◆ gpio_disable()

| void gpio_disable | ( | uint32_t | gpioport, |

| uint32_t | gpios | ||

| ) |

Disable output pins.

Onlyc the ones where bits are set to "1" are touched, everything else remains in the old state.

- Parameters

-

[in] gpioport uint32_t: GPIO Port base address [in] gpios uint32_t

Definition at line 97 of file gpio.c.

References GPIO_GPERC.

◆ gpio_enable()

| void gpio_enable | ( | uint32_t | gpioport, |

| uint32_t | gpios, | ||

| enum gpio_mode | mode | ||

| ) |

Enable output pins.

Onlyc the ones where bits are set to "1" are touched, everything else remains in the old state.

- Parameters

-

[in] gpioport uint32_t: GPIO Port base address [in] gpios uint32_t [in] mode enum gpio_mode GPIO mode. IN, OUT or peripheral function.

Definition at line 72 of file gpio.c.

References GPIO_GPERC, GPIO_GPERS, GPIO_MODE_IN, GPIO_MODE_OUT, GPIO_ODERC, GPIO_ODERS, and GPIO_PMR_SETVAL.