fmc_common_f47.h File Reference

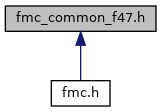

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | sdram_timing |

Enumerations | |

| enum | fmc_sdram_bank { SDRAM_BANK1 , SDRAM_BANK2 , SDRAM_BOTH_BANKS } |

| enum | fmc_sdram_command { SDRAM_CLK_CONF , SDRAM_NORMAL , SDRAM_PALL , SDRAM_AUTO_REFRESH , SDRAM_LOAD_MODE , SDRAM_SELF_REFRESH , SDRAM_POWER_DOWN } |

Functions | |

| uint32_t | sdram_timing (struct sdram_timing *t) |

| void | sdram_command (enum fmc_sdram_bank bank, enum fmc_sdram_command cmd, int autorefresh, int modereg) |