fsmc.h File Reference

Include dependency graph for fsmc.h:

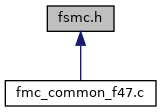

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | FSMC_BANK1_BASE 0x60000000U /* NOR / PSRAM */ |

| #define | FSMC_BANK2_BASE 0x70000000U /* NAND flash (reserved in F7) */ |

| #define | FSMC_BANK3_BASE 0x80000000U /* NAND flash */ |

| #define | FSMC_BANK4_BASE 0x90000000U /* PC card (reserved in F7) */ |

| #define | FSMC_BCR(x) MMIO32(FSMC_BASE + 0x00 + 8 * (x)) |

| #define | FSMC_BCR1 FSMC_BCR(0) |

| #define | FSMC_BCR2 FSMC_BCR(1) |

| #define | FSMC_BCR3 FSMC_BCR(2) |

| #define | FSMC_BCR4 FSMC_BCR(3) |

| #define | FSMC_BTR(x) MMIO32(FSMC_BASE + 0x04 + 8 * (x)) |

| #define | FSMC_BTR1 FSMC_BTR(0) |

| #define | FSMC_BTR2 FSMC_BTR(1) |

| #define | FSMC_BTR3 FSMC_BTR(2) |

| #define | FSMC_BTR4 FSMC_BTR(3) |

| #define | FSMC_BWTR(x) MMIO32(FSMC_BASE + 0x104 + 8 * (x)) |

| #define | FSMC_BWTR1 FSMC_BWTR(0) |

| #define | FSMC_BWTR2 FSMC_BWTR(1) |

| #define | FSMC_BWTR3 FSMC_BWTR(2) |

| #define | FSMC_BWTR4 FSMC_BWTR(3) |

| #define | FSMC_PCR(x) MMIO32(FSMC_BASE + 0x40 + 0x20 * (x)) |

| #define | FSMC_PCR2 FSMC_PCR(1) |

| #define | FSMC_PCR3 FSMC_PCR(2) |

| #define | FSMC_PCR4 FSMC_PCR(3) |

| #define | FSMC_SR(x) MMIO32(FSMC_BASE + 0x44 + 0x20 * (x)) |

| #define | FSMC_SR2 FSMC_SR(1) |

| #define | FSMC_SR3 FSMC_SR(2) |

| #define | FSMC_SR4 FSMC_SR(3) |

| #define | FSMC_PMEM(x) MMIO32(FSMC_BASE + 0x48 + 0x20 * (x)) |

| #define | FSMC_PMEM2 FSMC_PMEM(1) |

| #define | FSMC_PMEM3 FSMC_PMEM(2) |

| #define | FSMC_PMEM4 FSMC_PMEM(3) |

| #define | FSMC_PATT(x) MMIO32(FSMC_BASE + 0x4c + 0x20 * (x)) |

| #define | FSMC_PATT2 FSMC_PATT(1) |

| #define | FSMC_PATT3 FSMC_PATT(2) |

| #define | FSMC_PATT4 FSMC_PATT(3) |

| #define | FSMC_PIO4 MMIO32(FSMC_BASE + 0xb0) |

| #define | FSMC_ECCR(x) MMIO32(FSMC_BASE + 0x54 + 0x20 * (x)) |

| #define | FSMC_ECCR2 FSMC_ECCR(1) |

| #define | FSMC_ECCR3 FSMC_ECCR(2) |

| #define | FSMC_BCR_CBURSTRW (1 << 19) |

| #define | FSMC_BCR_ASYNCWAIT (1 << 15) |

| #define | FSMC_BCR_EXTMOD (1 << 14) |

| #define | FSMC_BCR_WAITEN (1 << 13) |

| #define | FSMC_BCR_WREN (1 << 12) |

| #define | FSMC_BCR_WAITCFG (1 << 11) |

| #define | FSMC_BCR_WRAPMOD (1 << 10) |

| #define | FSMC_BCR_WAITPOL (1 << 9) |

| #define | FSMC_BCR_BURSTEN (1 << 8) |

| #define | FSMC_BCR_FACCEN (1 << 6) |

| #define | FSMC_BCR_MWID (1 << 4) |

| #define | FSMC_BCR_MTYP (1 << 2) |

| #define | FSMC_BCR_MUXEN (1 << 1) |

| #define | FSMC_BCR_MBKEN (1 << 0) |

| #define | FSMC_BTx_ACCMOD_A (0) |

| #define | FSMC_BTx_ACCMOD_B (1) |

| #define | FSMC_BTx_ACCMOD_C (2) |

| #define | FSMC_BTx_ACCMOD_D (3) |

| #define | FSMC_BTR_ACCMOD (1 << 28) |

| #define | FSMC_BTR_ACCMODx(x) (((x) & 0x03) << 28) |

| #define | FSMC_BTR_DATLAT (1 << 24) |

| #define | FSMC_BTR_DATLATx(x) (((x) & 0x0f) << 24) |

| #define | FSMC_BTR_CLKDIV (1 << 20) |

| #define | FSMC_BTR_CLKDIVx(x) (((x) & 0x0f) << 20) |

| #define | FSMC_BTR_BUSTURN (1 << 16) |

| #define | FSMC_BTR_BUSTURNx(x) (((x) & 0x0f) << 16) |

| #define | FSMC_BTR_DATAST (1 << 8) |

| #define | FSMC_BTR_DATASTx(x) (((x) & 0xff) << 8) |

| #define | FSMC_BTR_ADDHLD (1 << 4) |

| #define | FSMC_BTR_ADDHLDx(x) (((x) & 0x0f) << 4) |

| #define | FSMC_BTR_ADDSET (1 << 0) |

| #define | FSMC_BTR_ADDSETx(x) (((x) & 0x0f) << 0) |

| #define | FSMC_BWTR_ACCMOD (1 << 28) |

| #define | FSMC_BWTR_DATLAT (1 << 24) |

| #define | FSMC_BWTR_CLKDIV (1 << 20) |

| #define | FSMC_BWTR_DATAST (1 << 8) |

| #define | FSMC_BWTR_ADDHLD (1 << 4) |

| #define | FSMC_BWTR_ADDSET (1 << 0) |

| #define | FSMC_PCR_ECCPS (1 << 17) |

| #define | FSMC_PCR_TAR (1 << 13) |

| #define | FSMC_PCR_TCLR (1 << 9) |

| #define | FSMC_PCR_ECCEN (1 << 6) |

| #define | FSMC_PCR_PWID (1 << 4) |

| #define | FSMC_PCR_PTYP (1 << 3) |

| #define | FSMC_PCR_PBKEN (1 << 2) |

| #define | FSMC_PCR_PWAITEN (1 << 1) |

| #define | FSMC_SR_FEMPT (1 << 6) |

| #define | FSMC_SR_IFEN (1 << 5) |

| #define | FSMC_SR_ILEN (1 << 4) |

| #define | FSMC_SR_IREN (1 << 3) |

| #define | FSMC_SR_IFS (1 << 2) |

| #define | FSMC_SR_ILS (1 << 1) |

| #define | FSMC_SR_IRS (1 << 0) |

| #define | FSMC_PMEM_MEMHIZX (1 << 24) |

| #define | FSMC_PMEM_MEMHOLDX (1 << 16) |

| #define | FSMC_PMEM_MEMWAITX (1 << 8) |

| #define | FSMC_PMEM_MEMSETX (1 << 0) |

| #define | FSMC_PATT_ATTHIZX (1 << 24) |

| #define | FSMC_PATT_ATTHOLDX (1 << 16) |

| #define | FSMC_PATT_ATTWAITX (1 << 8) |

| #define | FSMC_PATT_ATTSETX (1 << 0) |

| #define | FSMC_PIO4_IOHIZX (1 << 24) |

| #define | FSMC_PIO4_IOHOLDX (1 << 16) |

| #define | FSMC_PIO4_IOWAITX (1 << 8) |

| #define | FSMC_PIO4_IOSETX (1 << 0) |

| #define | FSMC_ECCR_ECCX (1 << 0) |

Macro Definition Documentation

◆ FSMC_BANK1_BASE

◆ FSMC_BANK2_BASE

| #define FSMC_BANK2_BASE 0x70000000U /* NAND flash (reserved in F7) */ |

◆ FSMC_BANK3_BASE

◆ FSMC_BANK4_BASE

| #define FSMC_BANK4_BASE 0x90000000U /* PC card (reserved in F7) */ |