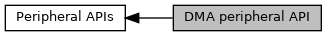

DMA library for the multi stream controller found in f2/f4/f7 parts. More...

Functions | |

| void | dma_stream_reset (uint32_t dma, uint8_t stream) |

| DMA Stream Reset. More... | |

| void | dma_clear_interrupt_flags (uint32_t dma, uint8_t stream, uint32_t interrupts) |

| DMA Stream Clear Interrupt Flag. More... | |

| bool | dma_get_interrupt_flag (uint32_t dma, uint8_t stream, uint32_t interrupt) |

| DMA Stream Read Interrupt Flag. More... | |

| void | dma_set_transfer_mode (uint32_t dma, uint8_t stream, uint32_t direction) |

| DMA Stream Enable Transfer Direction. More... | |

| void | dma_set_priority (uint32_t dma, uint8_t stream, uint32_t prio) |

| DMA Stream Set Priority. More... | |

| void | dma_set_memory_size (uint32_t dma, uint8_t stream, uint32_t mem_size) |

| DMA Stream Set Memory Word Width. More... | |

| void | dma_set_peripheral_size (uint32_t dma, uint8_t stream, uint32_t peripheral_size) |

| DMA Stream Set Peripheral Word Width. More... | |

| void | dma_enable_memory_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Memory Increment after Transfer. More... | |

| void | dma_disable_memory_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Disable Memory Increment after Transfer. More... | |

| void | dma_enable_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Enable Variable Sized Peripheral Increment after Transfer. More... | |

| void | dma_disable_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Disable Peripheral Increment after Transfer. More... | |

| void | dma_enable_fixed_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Enable Fixed Sized Peripheral Increment after Transfer. More... | |

| void | dma_enable_circular_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Memory Circular Mode. More... | |

| void | dma_channel_select (uint32_t dma, uint8_t stream, uint32_t channel) |

| DMA Stream Channel Select. More... | |

| void | dma_set_memory_burst (uint32_t dma, uint8_t stream, uint32_t burst) |

| DMA Stream Set Memory Burst Configuration. More... | |

| void | dma_set_peripheral_burst (uint32_t dma, uint8_t stream, uint32_t burst) |

| DMA Stream Set Peripheral Burst Configuration. More... | |

| void | dma_set_initial_target (uint32_t dma, uint8_t stream, uint8_t memory) |

| DMA Stream Set Initial Target Memory. More... | |

| uint8_t | dma_get_target (uint32_t dma, uint8_t stream) |

| DMA Stream Read Current Memory Target. More... | |

| void | dma_enable_double_buffer_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Double Buffer Mode. More... | |

| void | dma_disable_double_buffer_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Double Buffer Mode. More... | |

| void | dma_set_peripheral_flow_control (uint32_t dma, uint8_t stream) |

| DMA Stream Set Peripheral Flow Control. More... | |

| void | dma_set_dma_flow_control (uint32_t dma, uint8_t stream) |

| DMA Stream Set DMA Flow Control. More... | |

| void | dma_enable_transfer_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Error. More... | |

| void | dma_disable_transfer_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Error. More... | |

| void | dma_enable_half_transfer_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Half Complete. More... | |

| void | dma_disable_half_transfer_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Half Complete. More... | |

| void | dma_enable_transfer_complete_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Complete. More... | |

| void | dma_disable_transfer_complete_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Complete. More... | |

| void | dma_enable_direct_mode_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Direct Mode Error. More... | |

| void | dma_disable_direct_mode_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Direct Mode Error. More... | |

| void | dma_enable_fifo_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Enable Interrupt on FIFO Error. More... | |

| void | dma_disable_fifo_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Disable Interrupt on FIFO Error. More... | |

| uint32_t | dma_fifo_status (uint32_t dma, uint8_t stream) |

| DMA Get FIFO Status. More... | |

| void | dma_enable_direct_mode (uint32_t dma, uint8_t stream) |

| DMA Enable Direct Mode. More... | |

| void | dma_enable_fifo_mode (uint32_t dma, uint8_t stream) |

| DMA Enable FIFO Mode. More... | |

| void | dma_set_fifo_threshold (uint32_t dma, uint8_t stream, uint32_t threshold) |

| DMA Set FIFO Threshold. More... | |

| void | dma_enable_stream (uint32_t dma, uint8_t stream) |

| DMA Stream Enable. More... | |

| void | dma_disable_stream (uint32_t dma, uint8_t stream) |

| DMA Stream Disable. More... | |

| void | dma_set_peripheral_address (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Peripheral Address. More... | |

| void | dma_set_memory_address (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Base Memory Address 0. More... | |

| void | dma_set_memory_address_1 (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Base Memory Address 1. More... | |

| uint16_t | dma_get_number_of_data (uint32_t dma, uint8_t stream) |

| DMA Stream Get the Transfer Block Size. More... | |

| void | dma_set_number_of_data (uint32_t dma, uint8_t stream, uint16_t number) |

| DMA Stream Set the Transfer Block Size. More... | |

Detailed Description

DMA library for the multi stream controller found in f2/f4/f7 parts.

This library supports the DMA Control System in the STM32F2 and STM32F4 series of ARM Cortex Microcontrollers by ST Microelectronics.

Up to two DMA controllers are supported each with 8 streams, and each stream having up to 8 channels hardware dedicated to various peripheral DMA signals.

DMA transfers can be configured to occur between peripheral and memory in either direction, and memory to memory. Peripheral to peripheral transfer is not supported. Circular mode transfers are also supported in transfers involving a peripheral. An arbiter is provided to resolve priority DMA requests. Transfers can be made with 8, 16 or 32 bit words.

Each stream has access to a 4 word deep FIFO and can use double buffering by means of two memory pointers. When using the FIFO it is possible to configure transfers to occur in indivisible bursts.

It is also possible to select a peripheral instead of the DMA controller to control the flow of data. This limits the functionality but is useful when the number of transfers is unknown.

LGPL License Terms libopencm3 License

Function Documentation

◆ dma_channel_select()

| void dma_channel_select | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | channel | ||

| ) |

DMA Stream Channel Select.

Associate an input channel to the stream. Not every channel is allocated to a hardware DMA request signal. The allocations for each stream are given in the STM32F4 Reference Manual.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] channel unsigned int8. Channel selection DMA Channel Select

Definition at line 345 of file dma_common_f24.c.

References DMA_SCR.

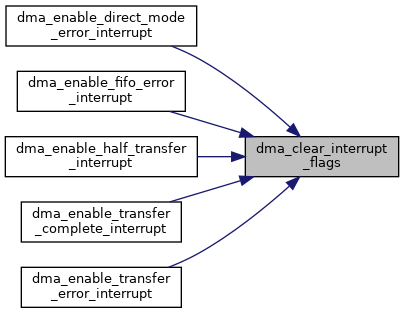

◆ dma_clear_interrupt_flags()

| void dma_clear_interrupt_flags | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | interrupts | ||

| ) |

DMA Stream Clear Interrupt Flag.

The interrupt flag for the stream is cleared. More than one interrupt for the same stream may be cleared by using the bitwise OR of the interrupt flags.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] interrupts unsigned int32. Bitwise OR of interrupt numbers: DMA Interrupt Flag Offsets within stream flag group.

Definition at line 97 of file dma_common_f24.c.

References DMA_HIFCR, DMA_ISR_OFFSET, and DMA_LIFCR.

Referenced by dma_enable_direct_mode_error_interrupt(), dma_enable_fifo_error_interrupt(), dma_enable_half_transfer_interrupt(), dma_enable_transfer_complete_interrupt(), and dma_enable_transfer_error_interrupt().

◆ dma_disable_direct_mode_error_interrupt()

| void dma_disable_direct_mode_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Direct Mode Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 593 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_double_buffer_mode()

| void dma_disable_double_buffer_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Double Buffer Mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 460 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_fifo_error_interrupt()

| void dma_disable_fifo_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Disable Interrupt on FIFO Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 618 of file dma_common_f24.c.

References DMA_SFCR.

◆ dma_disable_half_transfer_interrupt()

| void dma_disable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 543 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_memory_increment_mode()

| void dma_disable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Disable Memory Increment after Transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 253 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_peripheral_increment_mode()

| void dma_disable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Disable Peripheral Increment after Transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 286 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_stream()

| void dma_disable_stream | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable.

- Note

- The DMA stream registers retain their values when the stream is disabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 707 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_transfer_complete_interrupt()

| void dma_disable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 568 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_transfer_error_interrupt()

| void dma_disable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 518 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_enable_circular_mode()

| void dma_enable_circular_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Memory Circular Mode.

After the number of bytes/words to be transferred has been completed, the original transfer block size, memory and peripheral base addresses are reloaded and the process repeats.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Note

- This cannot be used with memory to memory mode. It is disabled automatically if the peripheral is selected as the flow controller. It is enabled automatically if double buffered mode is selected.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 326 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CIRC.

◆ dma_enable_direct_mode()

| void dma_enable_direct_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable Direct Mode.

Direct mode is the default. Data is transferred as soon as a DMA request is received. The FIFO is not used. This must not be set when memory to memory mode is selected.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 650 of file dma_common_f24.c.

References DMA_SFCR.

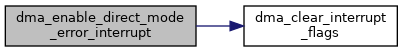

◆ dma_enable_direct_mode_error_interrupt()

| void dma_enable_direct_mode_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Direct Mode Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 580 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_DMEIF, DMA_SCR, and DMA_SxCR_DMEIE.

◆ dma_enable_double_buffer_mode()

| void dma_enable_double_buffer_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Double Buffer Mode.

Double buffer mode is used for memory to/from peripheral transfers only, and in circular mode which is automatically enabled. Two memory buffers must be established with pointers stored in the memory pointer registers.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Note

- This cannot be used with memory to memory mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 448 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_DBM.

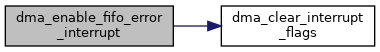

◆ dma_enable_fifo_error_interrupt()

| void dma_enable_fifo_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable Interrupt on FIFO Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 605 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_FEIF, DMA_SFCR, and DMA_SxFCR_FEIE.

◆ dma_enable_fifo_mode()

| void dma_enable_fifo_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable FIFO Mode.

Data is transferred via a FIFO.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 664 of file dma_common_f24.c.

References DMA_SFCR, and DMA_SxFCR_DMDIS.

◆ dma_enable_fixed_peripheral_increment_mode()

| void dma_enable_fixed_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Enable Fixed Sized Peripheral Increment after Transfer.

Following each transfer the current peripheral address is incremented by 4 regardless of the data size. The value held by the base peripheral address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 304 of file dma_common_f24.c.

References DMA_SCR, DMA_SxCR_PINC, and DMA_SxCR_PINCOS.

◆ dma_enable_half_transfer_interrupt()

| void dma_enable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 530 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_HTIF, DMA_SCR, and DMA_SxCR_HTIE.

◆ dma_enable_memory_increment_mode()

| void dma_enable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Memory Increment after Transfer.

Following each transfer the current memory address is incremented by 1, 2 or 4 depending on the data size set in dma_set_memory_size. The value held by the base memory address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 239 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_MINC.

◆ dma_enable_peripheral_increment_mode()

| void dma_enable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Enable Variable Sized Peripheral Increment after Transfer.

Following each transfer the current peripheral address is incremented by 1, 2 or 4 depending on the data size set in dma_set_peripheral_size. The value held by the base peripheral address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 271 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PINC.

◆ dma_enable_stream()

| void dma_enable_stream | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 693 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_EN.

◆ dma_enable_transfer_complete_interrupt()

| void dma_enable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 555 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_SCR, DMA_SxCR_TCIE, and DMA_TCIF.

◆ dma_enable_transfer_error_interrupt()

| void dma_enable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 505 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_SCR, DMA_SxCR_TEIE, and DMA_TEIF.

◆ dma_fifo_status()

| uint32_t dma_fifo_status | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Get FIFO Status.

Status of FIFO (empty. full or partial filled states) is returned. This has no meaning if direct mode is enabled (as the FIFO is not used).

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- uint32_t FIFO Status FIFO Status

Definition at line 634 of file dma_common_f24.c.

References DMA_SFCR, and DMA_SxFCR_FS_MASK.

◆ dma_get_interrupt_flag()

| bool dma_get_interrupt_flag | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | interrupt | ||

| ) |

DMA Stream Read Interrupt Flag.

The interrupt flag for the stream is returned.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] interrupt unsigned int32. Interrupt number: DMA Interrupt Flag Offsets within stream flag group.

- Returns

- bool interrupt flag is set.

Definition at line 123 of file dma_common_f24.c.

References DMA_HISR, DMA_ISR_OFFSET, and DMA_LISR.

◆ dma_get_number_of_data()

| uint16_t dma_get_number_of_data | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Get the Transfer Block Size.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- unsigned int16. Number of remaining data words to transfer (65535 maximum).

Definition at line 788 of file dma_common_f24.c.

References DMA_SNDTR.

◆ dma_get_target()

| uint8_t dma_get_target | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Read Current Memory Target.

In double buffer mode, return the current memory target (M0 or M1). It is possible to update the memory pointer in the register that is not currently in use. An attempt to change the register currently in use will cause the stream to be disabled and the transfer error flag to be set.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- unsigned int8. Memory buffer in use: 0 or 1

Definition at line 424 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CT.

◆ dma_set_dma_flow_control()

| void dma_set_dma_flow_control | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Set DMA Flow Control.

Set the DMA controller to control DMA flow. This is the default.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 493 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_fifo_threshold()

| void dma_set_fifo_threshold | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | threshold | ||

| ) |

DMA Set FIFO Threshold.

This is the filled level at which data is transferred out of the FIFO to the destination.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] threshold unsigned int8. Threshold setting FIFO Threshold selection

Definition at line 680 of file dma_common_f24.c.

References DMA_SFCR.

◆ dma_set_initial_target()

| void dma_set_initial_target | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint8_t | memory | ||

| ) |

DMA Stream Set Initial Target Memory.

In double buffered mode, set the target memory (M0 or M1) to be used for the first transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] memory unsigned int8. Initial memory pointer to use: 0 or 1

Definition at line 401 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CT.

◆ dma_set_memory_address()

| void dma_set_memory_address | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Base Memory Address 0.

Set the address pointer to the memory location for DMA transfers. The DMA stream must normally be disabled before setting this address, however it is possible to change this in double buffer mode when the current target is memory area 1 (see dma_get_target).

This is the default base memory address used in direct mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Memory Initial Address.

Definition at line 748 of file dma_common_f24.c.

References DMA_SCR, DMA_SM0AR, DMA_SxCR_CT, DMA_SxCR_DBM, and DMA_SxCR_EN.

◆ dma_set_memory_address_1()

| void dma_set_memory_address_1 | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Base Memory Address 1.

Set the address pointer to the memory location for DMA transfers. The DMA stream must normally be disabled before setting this address, however it is possible to change this in double buffer mode when the current target is memory area 0 (see dma_get_target).

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Memory Initial Address.

Definition at line 770 of file dma_common_f24.c.

References DMA_SCR, DMA_SM1AR, DMA_SxCR_CT, DMA_SxCR_DBM, and DMA_SxCR_EN.

◆ dma_set_memory_burst()

| void dma_set_memory_burst | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | burst | ||

| ) |

DMA Stream Set Memory Burst Configuration.

Set the memory burst type to none, 4 8 or 16 word length. This is forced to none if direct mode is used.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] burst unsigned int8. Memory Burst selection DMA Memory Burst Length

Definition at line 363 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_memory_size()

| void dma_set_memory_size | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | mem_size | ||

| ) |

DMA Stream Set Memory Word Width.

Set the memory word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] mem_size unsigned int32. Memory word width DMA Stream Memory Word Width.

Definition at line 198 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_MSIZE_MASK.

◆ dma_set_number_of_data()

| void dma_set_number_of_data | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint16_t | number | ||

| ) |

DMA Stream Set the Transfer Block Size.

- Note

- The DMA stream must be disabled before setting this count value. The count is not changed if the stream is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] number unsigned int16. Number of data words to transfer (65535 maximum).

Definition at line 805 of file dma_common_f24.c.

References DMA_SNDTR.

◆ dma_set_peripheral_address()

| void dma_set_peripheral_address | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Peripheral Address.

Set the address of the peripheral register to or from which data is to be transferred. Refer to the documentation for the specific peripheral.

- Note

- The DMA stream must be disabled before setting this address. This function has no effect if the stream is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Peripheral Address.

Definition at line 726 of file dma_common_f24.c.

References DMA_SCR, DMA_SPAR, and DMA_SxCR_EN.

◆ dma_set_peripheral_burst()

| void dma_set_peripheral_burst | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | burst | ||

| ) |

DMA Stream Set Peripheral Burst Configuration.

Set the memory burst type to none, 4 8 or 16 word length. This is forced to none if direct mode is used.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] burst unsigned int8. Peripheral Burst selection DMA Peripheral Burst Length

Definition at line 382 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_peripheral_flow_control()

| void dma_set_peripheral_flow_control | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Set Peripheral Flow Control.

Set the peripheral to control DMA flow. Useful when the number of transfers is unknown. This is forced off when memory to memory mode is selected.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 477 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PFCTRL.

◆ dma_set_peripheral_size()

| void dma_set_peripheral_size | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | peripheral_size | ||

| ) |

DMA Stream Set Peripheral Word Width.

Set the peripheral word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match, or if the peripheral does not support byte or half-word writes.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] peripheral_size unsigned int32. Peripheral word width DMA Stream Peripheral Word Width.

Definition at line 219 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PSIZE_MASK.

◆ dma_set_priority()

| void dma_set_priority | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | prio | ||

| ) |

DMA Stream Set Priority.

Stream Priority has four levels: low to very high. This has precedence over the hardware priority. In the event of equal software priority the lower numbered stream has priority.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] prio unsigned int32. Priority level DMA Stream Priority Levels.

Definition at line 179 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PL_MASK.

◆ dma_set_transfer_mode()

| void dma_set_transfer_mode | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | direction | ||

| ) |

DMA Stream Enable Transfer Direction.

Set peripheral to memory, memory to peripheral or memory to memory. If memory to memory mode is selected, circular mode and double buffer modes are disabled. Ensure that these modes are not enabled at a later time.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] direction unsigned int32. Data transfer direction DMA Stream Data transfer direction

Definition at line 151 of file dma_common_f24.c.

References DMA_SCR, DMA_SxCR_CIRC, DMA_SxCR_DBM, and DMA_SxCR_DIR_MEM_TO_MEM.

◆ dma_stream_reset()

| void dma_stream_reset | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Reset.

The specified stream is disabled and configuration registers are cleared.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 62 of file dma_common_f24.c.

References DMA_HIFCR, DMA_ISR_MASK, DMA_LIFCR, DMA_SCR, DMA_SFCR, DMA_SM0AR, DMA_SM1AR, DMA_SNDTR, and DMA_SPAR.