l1/adc.h File Reference

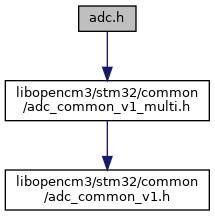

Include dependency graph for l1/adc.h:

Go to the source code of this file.

Macros | |

| #define | ADC_MAX_REGULAR_SEQUENCE 28 |

| #define | ADC_MAX_CHANNELS 32 |

| #define | ADC_SMPR3(block) MMIO32((block) + 0x14) |

| #define | ADC1_SMPR3 ADC_SMPR3(ADC1) |

| #define | ADC_JOFR1(block) MMIO32((block) + 0x18) |

| #define | ADC_JOFR2(block) MMIO32((block) + 0x1c) |

| #define | ADC_JOFR3(block) MMIO32((block) + 0x20) |

| #define | ADC_JOFR4(block) MMIO32((block) + 0x24) |

| #define | ADC_HTR(block) MMIO32((block) + 0x28) |

| #define | ADC_LTR(block) MMIO32((block) + 0x2c) |

| #define | ADC_SQR1(block) MMIO32((block) + 0x30) |

| #define | ADC_SQR2(block) MMIO32((block) + 0x34) |

| #define | ADC_SQR3(block) MMIO32((block) + 0x38) |

| #define | ADC_SQR4(block) MMIO32((block) + 0x3c) |

| #define | ADC1_SQR4 ADC_SQR4(ADC1) |

| #define | ADC_SQR5(block) MMIO32((block) + 0x40) |

| #define | ADC1_SQR5 ADC_SQR5(ADC1) |

| #define | ADC_JSQR(block) MMIO32((block) + 0x44) |

| #define | ADC_JDR1(block) MMIO32((block) + 0x48) |

| #define | ADC_JDR2(block) MMIO32((block) + 0x4c) |

| #define | ADC_JDR3(block) MMIO32((block) + 0x50) |

| #define | ADC_JDR4(block) MMIO32((block) + 0x54) |

| #define | ADC_DR(block) MMIO32((block) + 0x58) |

| #define | ADC_SMPR0(block) MMIO32((block) + 0x5c) |

| #define | ADC1_SMPR0 ADC_SMPR0(ADC1) |

| #define | ADC_CHANNEL_TEMP ADC_CHANNEL16 |

| #define | ADC_CHANNEL_VREF ADC_CHANNEL17 |

| #define | ADC_SR_JCNR (1 << 9) |

| Injected channel not ready. More... | |

| #define | ADC_SR_RCNR (1 << 8) |

| Regular channel not ready. More... | |

| #define | ADC_SR_ADONS (1 << 6) |

| ADC ON status. More... | |

| #define | ADC_CR1_PDI (1 << 17) |

| #define | ADC_CR1_PDD (1 << 16) |

| #define | ADC_CR1_AWDCH_MAX 26 |

| #define | ADC_CR2_EXTSEL_TIM9_CC2 (0 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM9_TRGO (1 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM2_CC3 (2 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM2_CC2 (3 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM3_TRGO (4 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM4_CC4 (5 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM2_TRGO (6 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM3_CC1 (7 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM3_CC3 (8 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM4_TRGO (9 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_TIM6_TRGO (10 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_EXTSEL_EXTI11 (15 << ADC_CR2_EXTSEL_SHIFT) |

| #define | ADC_CR2_DELS_SHIFT 4 |

| #define | ADC_CR2_DELS_MASK 0x7 |

| #define | ADC_CR2_ADC_CFG (1 << 2) |

| #define | ADC_SMPR_SMP_4CYC 0x0 |

| #define | ADC_SMPR_SMP_9CYC 0x1 |

| #define | ADC_SMPR_SMP_16CYC 0x2 |

| #define | ADC_SMPR_SMP_24CYC 0x3 |

| #define | ADC_SMPR_SMP_48CYC 0x4 |

| #define | ADC_SMPR_SMP_96CYC 0x5 |

| #define | ADC_SMPR_SMP_192CYC 0x6 |

| #define | ADC_SMPR_SMP_384CYC 0x7 |

| #define | ADC_SQR_MASK 0x1f |

| #define | ADC_SQR_MAX_CHANNELS_REGULAR 28 /* m+/h only, otherwise 27 */ |

| #define | ADC_CCR_ADCPRE_BY1 (0x0 << 16) |

| #define | ADC_CCR_ADCPRE_BY2 (0x1 << 16) |

| #define | ADC_CCR_ADCPRE_BY4 (0x2 << 16) |

| #define | ADC_CCR_ADCPRE_MASK (0x3 << 16) |

| #define | ADC_CCR_ADCPRE_SHIFT 16 |