dac_common_all.h File Reference

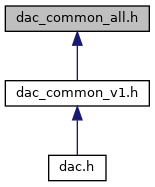

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | DAC_CR(dac) MMIO32((dac) + 0x00) |

| DAC control register (DAC_CR) More... | |

| #define | DAC_SWTRIGR(dac) MMIO32((dac) + 0x04) |

| DAC software trigger register (DAC_SWTRIGR) More... | |

| #define | DAC_DHR12R1(dac) MMIO32((dac) + 0x08) |

| DAC channel1 12-bit right-aligned data holding register (DAC_DHR12R1) More... | |

| #define | DAC_DHR12L1(dac) MMIO32((dac) + 0x0C) |

| DAC channel1 12-bit left aligned data holding register (DAC_DHR12L1) More... | |

| #define | DAC_DHR8R1(dac) MMIO32((dac) + 0x10) |

| DAC channel1 8-bit right aligned data holding register (DAC_DHR8R1) More... | |

| #define | DAC_DHR12R2(dac) MMIO32((dac) + 0x14) |

| DAC channel2 12-bit right aligned data holding register (DAC_DHR12R2) More... | |

| #define | DAC_DHR12L2(dac) MMIO32((dac) + 0x18) |

| DAC channel2 12-bit left aligned data holding register (DAC_DHR12L2) More... | |

| #define | DAC_DHR8R2(dac) MMIO32((dac) + 0x1C) |

| DAC channel2 8-bit right-aligned data holding register (DAC_DHR8R2) More... | |

| #define | DAC_DHR12RD(dac) MMIO32((dac) + 0x20) |

| Dual DAC 12-bit right-aligned data holding register (DAC_DHR12RD) More... | |

| #define | DAC_DHR12LD(dac) MMIO32((dac) + 0x24) |

| DUAL DAC 12-bit left aligned data holding register (DAC_DHR12LD) More... | |

| #define | DAC_DHR8RD(dac) MMIO32((dac) + 0x28) |

| DUAL DAC 8-bit right aligned data holding register (DAC_DHR8RD) More... | |

| #define | DAC_DOR1(dac) MMIO32((dac) + 0x2C) |

| DAC channel1 data output register (DAC_DOR1) More... | |

| #define | DAC_DOR2(dac) MMIO32((dac) + 0x30) |

| DAC channel2 data output register (DAC_DOR2) More... | |

| #define | DAC_SR(dac) MMIO32((dac) + 0x34) |

| DAC status register. More... | |

| #define | DAC_CR_DMAUDRIE2 (1 << 29) |

| DMAUDRIE2: DAC channel2 DMA underrun interrupt enable. More... | |

| #define | DAC_CR_DMAEN2 (1 << 28) |

| DMAEN2: DAC channel2 DMA enable. More... | |

| #define | DAC_CR_MAMP2_SHIFT 24 |

| MAMP2[3:0]: DAC channel2 mask/amplitude selector field position. More... | |

| #define | DAC_CR_WAVEx_MASK 0x3 |

| Wave generation mode mask size. More... | |

| #define | DAC_CR_WAVE2_SHIFT 22 |

| WAVE2[1:0]: DAC channel2 wave generation mode. More... | |

| #define | DAC_CR_EN2 (1 << 16) |

| EN2: DAC channel2 enable. More... | |

| #define | DAC_CR_DMAUDRIE1 (1 << 13) |

| DMAUDRIE1: DAC channel1 DMA underrun interrupt enable. More... | |

| #define | DAC_CR_DMAEN1 (1 << 12) |

| DMAEN1: DAC channel1 DMA enable. More... | |

| #define | DAC_CR_MAMP1_SHIFT 8 |

| MAMP1[3:0]: DAC channel1 mask/amplitude selector field position. More... | |

| #define | DAC_CR_MAMPx_MASK 0xf |

| MAMP Mask/Amplitude selector field size. More... | |

| #define | DAC_CR_WAVE1_SHIFT 6 |

| WAVE1[1:0]: DAC channel1 wave generation mode. More... | |

| #define | DAC_CR_EN1 (1 << 0) |

| EN1: DAC channel1 enable. More... | |

| #define | DAC_SWTRIGR_SWTRIG2 (1 << 1) |

| SWTRIG2: DAC channel2 software trigger. More... | |

| #define | DAC_SWTRIGR_SWTRIG1 (1 << 0) |

| SWTRIG1: DAC channel1 software trigger. More... | |

| #define | DAC_DHR12R1_DACC1DHR_SHIFT 0 |

| #define | DAC_DHR12R1_DACC1DHR_MASK 0xFFF |

| #define | DAC_DHR12L1_DACC1DHR_SHIFT 4 |

| #define | DAC_DHR12L1_DACC1DHR_MASK 0xFFF |

| #define | DAC_DHR8R1_DACC1DHR_SHIFT 0 |

| #define | DAC_DHR8R1_DACC1DHR_MASK 0xFF |

| #define | DAC_DHR12R2_DACC2DHR_SHIFT 0 |

| #define | DAC_DHR12R2_DACC2DHR_MASK 0xFFF |

| #define | DAC_DHR12L2_DACC2DHR_SHIFT 4 |

| #define | DAC_DHR12L2_DACC2DHR_MASK 0xFFF |

| #define | DAC_DHR8R2_DACC2DHR_SHIFT 0 |

| #define | DAC_DHR8R2_DACC2DHR_MASK 0xFF |

| #define | DAC_DHR12RD_DACC2DHR_SHIFT 16 |

| #define | DAC_DHR12RD_DACC2DHR_MASK 0xFFF |

| #define | DAC_DHR12RD_DACC1DHR_SHIFT 0 |

| #define | DAC_DHR12RD_DACC1DHR_MSK 0xFFF |

| #define | DAC_DHR12LD_DACC2DHR_SHIFT 16 |

| #define | DAC_DHR12LD_DACC2DHR_MSK 0xFFF |

| #define | DAC_DHR12LD_DACC1DHR_SHIFT 0 |

| #define | DAC_DHR12LD_DACC1DHR_MSK 0xFFF |

| #define | DAC_DHR8RD_DACC2DHR_SHIFT 8 |

| #define | DAC_DHR8RD_DACC2DHR_MSK 0xFF |

| #define | DAC_DHR8RD_DACC1DHR_SHIFT 0 |

| #define | DAC_DHR8RD_DACC1DHR_MSK 0xFF |

| #define | DAC_DOR1_DACC1DOR_SHIFT 0 |

| #define | DAC_DOR1_DACC1DOR_MSK 0xFFF |

| #define | DAC_DOR2_DACC2DOR_SHIFT 0 |

| #define | DAC_DOR2_DACC2DOR_MSK 0xFFF |

| #define | DAC_SR_DMAUDR1 (1 << 13) |

| DAC channel 1 DMA underrun flag. More... | |

| #define | DAC_SR_DMAUDR2 (1 << 29) |

| DAC channel 2 DMA underrun flag. More... | |

| #define | DAC_CHANNEL1 (1 << 0) |

| #define | DAC_CHANNEL2 (1 << 1) |

| #define | DAC_CHANNEL_BOTH (DAC_CHANNEL1 | DAC_CHANNEL2) |

Enumerations | |

| enum | dac_align { DAC_ALIGN_RIGHT8 , DAC_ALIGN_RIGHT12 , DAC_ALIGN_LEFT12 } |

| DAC data size (8/12 bits), alignment (right/left) More... | |

| enum | dac_wave { DAC_WAVE_DISABLE = 0 , DAC_WAVE_NOISE = 1 , DAC_WAVE_TRIANGLE = 2 , DAC_WAVE_SAWTOOTH = 3 } |

| DAC waveform generation options. More... | |

Functions | |

| void | dac_enable (uint32_t dac, int channel) |

| DAC Channel Enable. More... | |

| void | dac_disable (uint32_t dac, int channel) |

| DAC Channel Disable. More... | |

| void | dac_buffer_enable (uint32_t dac, int channel) |

| DAC Channel Output Buffer Enable. More... | |

| void | dac_buffer_disable (uint32_t dac, int channel) |

| DAC Channel Output Buffer Disable. More... | |

| void | dac_dma_enable (uint32_t dac, int channel) |

| DAC Channel DMA Enable. More... | |

| void | dac_dma_disable (uint32_t dac, int channel) |

| DAC Channel DMA Disable. More... | |

| void | dac_trigger_enable (uint32_t dac, int channel) |

| DAC Channel Trigger Enable. More... | |

| void | dac_trigger_disable (uint32_t dac, int channel) |

| DAC Channel Trigger Disable. More... | |

| void | dac_set_trigger_source (uint32_t dac, uint32_t source) |

| Set DAC Channel Trigger Source. More... | |

| void | dac_set_waveform_generation (uint32_t dac, int channel, enum dac_wave wave) |

| Set DAC Channel Waveform Generation mode for one or both channels. More... | |

| void | dac_disable_waveform_generation (uint32_t dac, int channel) |

| Disable DAC Channel Waveform Generation. More... | |

| void | dac_set_waveform_characteristics (uint32_t dac, int channel, int mamp) |

| Set DAC Channel LFSR Mask or Triangle Wave Amplitude. More... | |

| void | dac_load_data_buffer_single (uint32_t dac, uint16_t data, enum dac_align align, int channel) |

| Load DAC Data Register. More... | |

| void | dac_load_data_buffer_dual (uint32_t dac, uint16_t data1, uint16_t data2, enum dac_align align) |

| Load DAC Dual Data Register. More... | |

| void | dac_software_trigger (uint32_t dac, int channel) |

| Trigger the DAC by a Software Trigger. More... | |