mac_stm32fxx7.h File Reference

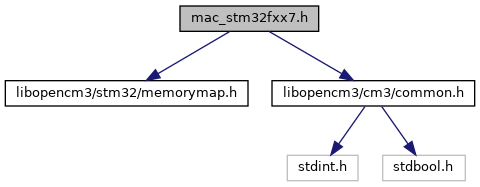

Include dependency graph for mac_stm32fxx7.h:

Go to the source code of this file.

Enumerations | |

| enum | eth_clk { ETH_CLK_025_035MHZ = ETH_MACMIIAR_CR_HCLK_DIV_16 , ETH_CLK_035_060MHZ = ETH_MACMIIAR_CR_HCLK_DIV_26 , ETH_CLK_060_100MHZ = ETH_MACMIIAR_CR_HCLK_DIV_42 , ETH_CLK_100_150MHZ = ETH_MACMIIAR_CR_HCLK_DIV_62 , ETH_CLK_150_168MHZ = ETH_MACMIIAR_CR_HCLK_DIV_102 } |

Functions | |

| void | eth_smi_write (uint8_t phy, uint8_t reg, uint16_t data) |

| Write 16-bit register to the PHY. More... | |

| uint16_t | eth_smi_read (uint8_t phy, uint8_t reg) |

| Read the 16-bit register from the PHY. More... | |

| void | eth_smi_bit_op (uint8_t phy, uint8_t reg, uint16_t bits, uint16_t mask) |

| Process the bit-operation on PHY register. More... | |

| void | eth_smi_bit_clear (uint8_t phy, uint8_t reg, uint16_t clearbits) |

| Clear bits in the register. More... | |

| void | eth_smi_bit_set (uint8_t phy, uint8_t reg, uint16_t setbits) |

| Set bits in the register. More... | |

| void | eth_set_mac (const uint8_t *mac) |

| Set MAC to the PHY. More... | |

| void | eth_desc_init (uint8_t *buf, uint32_t nTx, uint32_t nRx, uint32_t cTx, uint32_t cRx, bool isext) |

| Initialize buffers and descriptors. More... | |

| bool | eth_tx (uint8_t *ppkt, uint32_t n) |

| Transmit packet. More... | |

| bool | eth_rx (uint8_t *ppkt, uint32_t *len, uint32_t maxlen) |

| Receive packet. More... | |

| void | eth_init (uint8_t phy, enum eth_clk clock) |

| Initialize ethernet. More... | |

| void | eth_start (void) |

| Start the Ethernet DMA processing. More... | |

| void | eth_enable_checksum_offload (void) |

| Enable checksum offload feature. More... | |

| void | eth_irq_enable (uint32_t reason) |

| Enable the Ethernet IRQ. More... | |

| void | eth_irq_disable (uint32_t reason) |

| Disable the Ethernet IRQ. More... | |

| bool | eth_irq_is_pending (uint32_t reason) |

| Check if IRQ is pending. More... | |

| bool | eth_irq_ack_pending (uint32_t reason) |

| Check if IRQ is pending, and acknowledge it. More... | |