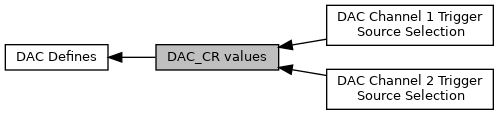

Modules | |

| DAC Channel 2 Trigger Source Selection | |

| DAC Channel 1 Trigger Source Selection | |

Macros | |

| #define | DAC_CR_DMAUDRIE2 (1 << 29) |

| DMAUDRIE2: DAC channel2 DMA underrun interrupt enable. More... | |

| #define | DAC_CR_DMAEN2 (1 << 28) |

| DMAEN2: DAC channel2 DMA enable. More... | |

| #define | DAC_CR_MAMP2_SHIFT 24 |

| MAMP2[3:0]: DAC channel2 mask/amplitude selector field position. More... | |

| #define | DAC_CR_WAVEx_MASK 0x3 |

| Wave generation mode mask size. More... | |

| #define | DAC_CR_WAVE2_SHIFT 22 |

| WAVE2[1:0]: DAC channel2 wave generation mode. More... | |

| #define | DAC_CR_EN2 (1 << 16) |

| EN2: DAC channel2 enable. More... | |

| #define | DAC_CR_DMAUDRIE1 (1 << 13) |

| DMAUDRIE1: DAC channel1 DMA underrun interrupt enable. More... | |

| #define | DAC_CR_DMAEN1 (1 << 12) |

| DMAEN1: DAC channel1 DMA enable. More... | |

| #define | DAC_CR_MAMP1_SHIFT 8 |

| MAMP1[3:0]: DAC channel1 mask/amplitude selector field position. More... | |

| #define | DAC_CR_MAMPx_MASK 0xf |

| MAMP Mask/Amplitude selector field size. More... | |

| #define | DAC_CR_WAVE1_SHIFT 6 |

| WAVE1[1:0]: DAC channel1 wave generation mode. More... | |

| #define | DAC_CR_EN1 (1 << 0) |

| EN1: DAC channel1 enable. More... | |

| #define | DAC_CR_TSEL2_SHIFT 19 |

| TSEL2[2:0]: DAC channel2 trigger selection. More... | |

| #define | DAC_CR_TEN2 (1 << 18) |

| #define | DAC_CR_BOFF2 (1 << 17) |

| #define | DAC_CR_TSEL1_SHIFT 3 |

| #define | DAC_CR_TEN1 (1 << 2) |

| #define | DAC_CR_BOFF1 (1 << 1) |

Detailed Description

Macro Definition Documentation

◆ DAC_CR_BOFF1

| #define DAC_CR_BOFF1 (1 << 1) |

Definition at line 121 of file dac_common_v1.h.

◆ DAC_CR_BOFF2

| #define DAC_CR_BOFF2 (1 << 17) |

Definition at line 82 of file dac_common_v1.h.

◆ DAC_CR_DMAEN1

| #define DAC_CR_DMAEN1 (1 << 12) |

DMAEN1: DAC channel1 DMA enable.

Definition at line 121 of file dac_common_all.h.

◆ DAC_CR_DMAEN2

| #define DAC_CR_DMAEN2 (1 << 28) |

DMAEN2: DAC channel2 DMA enable.

Definition at line 101 of file dac_common_all.h.

◆ DAC_CR_DMAUDRIE1

| #define DAC_CR_DMAUDRIE1 (1 << 13) |

DMAUDRIE1: DAC channel1 DMA underrun interrupt enable.

- Note

- doesn't exist in most members of the STM32F1 family

Definition at line 118 of file dac_common_all.h.

◆ DAC_CR_DMAUDRIE2

| #define DAC_CR_DMAUDRIE2 (1 << 29) |

DMAUDRIE2: DAC channel2 DMA underrun interrupt enable.

- Note

- doesn't exist in most members of the STM32F1 family

Definition at line 98 of file dac_common_all.h.

◆ DAC_CR_EN1

| #define DAC_CR_EN1 (1 << 0) |

EN1: DAC channel1 enable.

Definition at line 132 of file dac_common_all.h.

◆ DAC_CR_EN2

| #define DAC_CR_EN2 (1 << 16) |

EN2: DAC channel2 enable.

Definition at line 113 of file dac_common_all.h.

◆ DAC_CR_MAMP1_SHIFT

| #define DAC_CR_MAMP1_SHIFT 8 |

MAMP1[3:0]: DAC channel1 mask/amplitude selector field position.

Definition at line 124 of file dac_common_all.h.

◆ DAC_CR_MAMP2_SHIFT

| #define DAC_CR_MAMP2_SHIFT 24 |

MAMP2[3:0]: DAC channel2 mask/amplitude selector field position.

Definition at line 104 of file dac_common_all.h.

◆ DAC_CR_MAMPx_MASK

| #define DAC_CR_MAMPx_MASK 0xf |

MAMP Mask/Amplitude selector field size.

Definition at line 126 of file dac_common_all.h.

◆ DAC_CR_TEN1

| #define DAC_CR_TEN1 (1 << 2) |

Definition at line 118 of file dac_common_v1.h.

◆ DAC_CR_TEN2

| #define DAC_CR_TEN2 (1 << 18) |

Definition at line 79 of file dac_common_v1.h.

◆ DAC_CR_TSEL1_SHIFT

| #define DAC_CR_TSEL1_SHIFT 3 |

Definition at line 85 of file dac_common_v1.h.

◆ DAC_CR_TSEL2_SHIFT

| #define DAC_CR_TSEL2_SHIFT 19 |

TSEL2[2:0]: DAC channel2 trigger selection.

Definition at line 46 of file dac_common_v1.h.

◆ DAC_CR_WAVE1_SHIFT

| #define DAC_CR_WAVE1_SHIFT 6 |

WAVE1[1:0]: DAC channel1 wave generation mode.

Definition at line 129 of file dac_common_all.h.

◆ DAC_CR_WAVE2_SHIFT

| #define DAC_CR_WAVE2_SHIFT 22 |

WAVE2[1:0]: DAC channel2 wave generation mode.

Definition at line 110 of file dac_common_all.h.

◆ DAC_CR_WAVEx_MASK

| #define DAC_CR_WAVEx_MASK 0x3 |

Wave generation mode mask size.

Definition at line 107 of file dac_common_all.h.