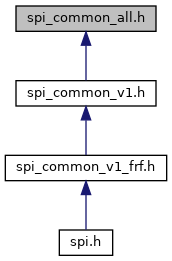

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | spi_enable (uint32_t spi) |

| SPI Enable. More... | |

| void | spi_disable (uint32_t spi) |

| SPI Disable. More... | |

| uint16_t | spi_clean_disable (uint32_t spi) |

| SPI Clean Disable. More... | |

| void | spi_write (uint32_t spi, uint16_t data) |

| SPI Data Write. More... | |

| void | spi_send (uint32_t spi, uint16_t data) |

| SPI Data Write with Blocking. More... | |

| uint16_t | spi_read (uint32_t spi) |

| SPI Data Read. More... | |

| uint16_t | spi_xfer (uint32_t spi, uint16_t data) |

| SPI Data Write and Read Exchange. More... | |

| void | spi_set_bidirectional_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Mode. More... | |

| void | spi_set_unidirectional_mode (uint32_t spi) |

| SPI Set Unidirectional Mode. More... | |

| void | spi_set_bidirectional_receive_only_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Receive Only Mode. More... | |

| void | spi_set_bidirectional_transmit_only_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Receive Only Mode. More... | |

| void | spi_enable_crc (uint32_t spi) |

| SPI Enable the CRC. More... | |

| void | spi_disable_crc (uint32_t spi) |

| SPI Disable the CRC. More... | |

| void | spi_set_next_tx_from_buffer (uint32_t spi) |

| SPI Next Transmit is a Data Word. More... | |

| void | spi_set_next_tx_from_crc (uint32_t spi) |

| SPI Next Transmit is a CRC Word. More... | |

| void | spi_set_full_duplex_mode (uint32_t spi) |

| SPI Set Full Duplex (3-wire) Mode. More... | |

| void | spi_set_receive_only_mode (uint32_t spi) |

| SPI Set Receive Only Mode for Simplex (2-wire) Unidirectional Transfers. More... | |

| void | spi_disable_software_slave_management (uint32_t spi) |

| SPI Disable Slave Management by Hardware. More... | |

| void | spi_enable_software_slave_management (uint32_t spi) |

| SPI Enable Slave Management by Software. More... | |

| void | spi_set_nss_high (uint32_t spi) |

| SPI Set the Software NSS Signal High. More... | |

| void | spi_set_nss_low (uint32_t spi) |

| SPI Set the Software NSS Signal Low. More... | |

| void | spi_send_lsb_first (uint32_t spi) |

| SPI Set to Send LSB First. More... | |

| void | spi_send_msb_first (uint32_t spi) |

| SPI Set to Send MSB First. More... | |

| void | spi_set_baudrate_prescaler (uint32_t spi, uint8_t baudrate) |

| SPI Set the Baudrate Prescaler. More... | |

| void | spi_set_master_mode (uint32_t spi) |

| SPI Set to Master Mode. More... | |

| void | spi_set_slave_mode (uint32_t spi) |

| SPI Set to Slave Mode. More... | |

| void | spi_set_clock_polarity_1 (uint32_t spi) |

| SPI Set the Clock Polarity to High when Idle. More... | |

| void | spi_set_clock_polarity_0 (uint32_t spi) |

| SPI Set the Clock Polarity to Low when Idle. More... | |

| void | spi_set_clock_phase_1 (uint32_t spi) |

| SPI Set the Clock Phase to Capture on Trailing Edge. More... | |

| void | spi_set_clock_phase_0 (uint32_t spi) |

| SPI Set the Clock Phase to Capture on Leading Edge. More... | |

| void | spi_enable_tx_buffer_empty_interrupt (uint32_t spi) |

| SPI Enable the Transmit Buffer Empty Interrupt. More... | |

| void | spi_disable_tx_buffer_empty_interrupt (uint32_t spi) |

| SPI Disable the Transmit Buffer Empty Interrupt. More... | |

| void | spi_enable_rx_buffer_not_empty_interrupt (uint32_t spi) |

| SPI Enable the Receive Buffer Ready Interrupt. More... | |

| void | spi_disable_rx_buffer_not_empty_interrupt (uint32_t spi) |

| SPI Disable the Receive Buffer Ready Interrupt. More... | |

| void | spi_enable_error_interrupt (uint32_t spi) |

| SPI Enable the Error Interrupt. More... | |

| void | spi_disable_error_interrupt (uint32_t spi) |

| SPI Disable the Error Interrupt. More... | |

| void | spi_enable_ss_output (uint32_t spi) |

| SPI Set the NSS Pin as an Output. More... | |

| void | spi_disable_ss_output (uint32_t spi) |

| SPI Set the NSS Pin as an Input. More... | |

| void | spi_enable_tx_dma (uint32_t spi) |

| SPI Enable Transmit Transfers via DMA. More... | |

| void | spi_disable_tx_dma (uint32_t spi) |

| SPI Disable Transmit Transfers via DMA. More... | |

| void | spi_enable_rx_dma (uint32_t spi) |

| SPI Enable Receive Transfers via DMA. More... | |

| void | spi_disable_rx_dma (uint32_t spi) |

| SPI Disable Receive Transfers via DMA. More... | |

| void | spi_set_standard_mode (uint32_t spi, uint8_t mode) |

| SPI Standard Mode selection. More... | |