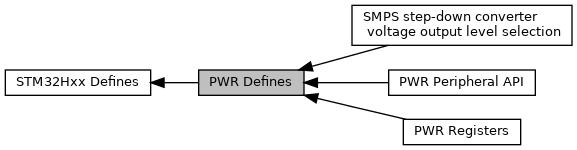

Defined Constants and Types for the STM32H7xx Power Control More...

Modules | |

| PWR Registers | |

| SMPS step-down converter voltage output level selection | |

| This setting is used when both the LDO and SMPS step-down converter are enabled with SMPSEN and LDOEN enabled or when SMPSEXTHP is enabled. | |

| PWR Peripheral API | |

Macros | |

| #define | PWR_CR1_SVOS_SHIFT 14 |

| VOS[15:14]: Regulator voltage scaling output selection. More... | |

| #define | PWR_CR1_SVOS_MASK (0x3) |

| #define | PWR_CR1_SVOS_SCALE_3 (0x3) |

| #define | PWR_CR1_SVOS_SCALE_4 (0x2) |

| #define | PWR_CR1_SVOS_SCALE_5 (0x1) |

| #define | PWR_CR1_SRDRAMSO BIT27 |

| SmartRun domain AHB memory shut-off in DStop/DStop2 low-power mode. More... | |

| #define | PWR_CR1_HSITFSO BIT26 |

| high-speed interfaces USB and FDCAN memory shut-off in DStop/DStop2 mode More... | |

| #define | PWR_CR1_GFXSO BIT25 |

| GFXMMU and JPEG memory shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_ITCMSO BIT24 |

| instruction TCM and ETM memory shut-off in DStop/DStop2 mode More... | |

| #define | PWR_CR1_AHBRAM2SO BIT23 |

| AHB SRAM2 shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_AHBRAM1SO BIT22 |

| AHB SRAM1 shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_AXIRAM3SO BIT21 |

| AXI SRAM3 shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_AXIRAM2SO BIT20 |

| AXI SRAM2 shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_AXIRAM1SO BIT19 |

| AXI SRAM1 shut-off in DStop/DStop2 mode. More... | |

| #define | PWR_CR1_ALS_SHIFT 17 |

| voltage threshold detected by the AVD. More... | |

| #define | PWR_CR1_ALS_MASK 0x3 |

| #define | PWR_CR1_ALS_1P7V 0x0 |

| #define | PWR_CR1_ALS_2P1V 0x1 |

| #define | PWR_CR1_ALS_2P5V 0x2 |

| #define | PWR_CR1_ALS_2P8V 0x3 |

| #define | PWR_CR1_AVDEN BIT16 |

| peripheral voltage monitor on V DDA enable More... | |

| #define | PWR_CR1_AVD_READY BIT13 |

| analog voltage ready This bit is only used when the analog switch boost needs to be enabled (see BOOSTE bit). More... | |

| #define | PWR_CR1_BOOSTE BIT12 |

| analog switch VBoost control This bit enables the booster to guarantee the analog switch AC performance when the V DD supply voltage is below 2.7 V (reduction of the total harmonic distortion to have the same switch performance over the full supply voltage range) The V DD supply voltage can be monitored through the PVD and the PLS bits. More... | |

| #define | PWR_CR1_DBP BIT8 |

| DBP[8]: Disable backup domain write protection. More... | |

| #define | PWR_CSR1_MMCVDO BIT17 |

| CSR1 Register Bits. More... | |

| #define | PWR_CSR1_AVDO BIT16 |

| #define | PWR_CSR1_ACTVOS_SHIFT 14 |

| #define | PWR_CSR1_ACTVOSRDY BIT13 |

| #define | PWR_CSR1_PVDO BIT4 |

| #define | PWR_CR2_TEMPH BIT23 |

| CR2 Register Bits. More... | |

| #define | PWR_CR2_TEMPL BIT22 |

| temperature level monitoring versus low threshold More... | |

| #define | PWR_CR2_BRRDY BIT16 |

| backup regulator ready More... | |

| #define | PWR_CR2_MONEN BIT4 |

| V BAT and temperature monitoring enable. More... | |

| #define | PWR_CR2_BREN BIT0 |

| backup regulator enable More... | |

| #define | PWR_CR3_USB33RDY BIT26 |

| CR3 Register Bits. More... | |

| #define | PWR_CR3_USBREGEN BIT25 |

| #define | PWR_CR3_USB33DEN BIT24 |

| #define | PWR_CR3_SMPSEXTRDY BIT16 |

| SMPS step-down converter external supply ready. More... | |

| #define | PWR_CR3_VBRS BIT9 |

| V BAT charging resistor selection More... | |

| #define | PWR_CR3_VBE BIT8 |

| V BAT charging enable. More... | |

| #define | PWR_CR3_SMPSLEVEL_SHIFT 4 |

| #define | PWR_CR3_SMPSLEVEL_MASK 0x3 |

| #define | PWR_CR3_SMPSEXTHP BIT3 |

| SMPS step-down converter external power delivery selection. More... | |

| #define | PWR_CR3_SCUEN BIT2 |

| #define | PWR_CR3_SMPSEN BIT2 |

| #define | PWR_CR3_LDOEN BIT1 |

| #define | PWR_CR3_BYPASS BIT0 |

| #define | PWR_D3CR_VOSRDY BIT13 |

| D3CR Register Bits. More... | |

| #define | PWR_D3CR_VOS_SHIFT 14 |

| #define | PWR_D3CR_VOS_MASK (0x03) |

| #define | PWR_D3CR_VOS_SCALE_0 (0x0) |

| VOS0 is implemented on STM32H72x/3x with simple VOS setting. More... | |

| #define | PWR_D3CR_VOS_SCALE_3 (0x1) |

| #define | PWR_D3CR_VOS_SCALE_2 (0x2) |

| #define | PWR_D3CR_VOS_SCALE_1 (0x3) |

| #define | PWR_SRDCR_VOSRDY BIT13 |

| SRDCR Register Bits. More... | |

| #define | PWR_SRDCR_VOS_SHIFT 14 |

| #define | PWR_SRDCR_VOS_MASK (0x03) |

| #define | PWR_SRDCR_VOS_SCALE_3 (0x0) |

| #define | PWR_SRDCR_VOS_SCALE_2 (0x1) |

| #define | PWR_SRDCR_VOS_SCALE_1 (0x2) |

| #define | PWR_SRDCR_VOS_SCALE_0 (0x3) |

Enumerations | |

| enum | pwr_sys_mode { PWR_SYS_SCU_LDO = 0 , PWR_SYS_SCU_BYPASS , PWR_SYS_LDO , PWR_SYS_SMPS_DIRECT , PWR_SYS_SMPS_LDO , PWR_SYS_EXT_SMPS_LDO , PWR_SYS_EXT_SMPS_LDO_BYP , PWR_SYS_BYPASS } |

| enum | pwr_svos_scale { PWR_SVOS_SCALE3 = PWR_CR1_SVOS_SCALE_3 << PWR_CR1_SVOS_SHIFT , PWR_SVOS_SCALE4 = PWR_CR1_SVOS_SCALE_4 << PWR_CR1_SVOS_SHIFT , PWR_SVOS_SCALE5 = PWR_CR1_SVOS_SCALE_5 << PWR_CR1_SVOS_SHIFT } |

| enum | pwr_vos_scale { PWR_VOS_SCALE_UNDEFINED = 0 , PWR_VOS_SCALE_0 , PWR_VOS_SCALE_1 , PWR_VOS_SCALE_2 , PWR_VOS_SCALE_3 } |

Detailed Description

Defined Constants and Types for the STM32H7xx Power Control

- Version

- 1.0.0

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ PWR_CR1_AHBRAM1SO

| #define PWR_CR1_AHBRAM1SO BIT22 |

◆ PWR_CR1_AHBRAM2SO

| #define PWR_CR1_AHBRAM2SO BIT23 |

◆ PWR_CR1_ALS_1P7V

◆ PWR_CR1_ALS_2P1V

◆ PWR_CR1_ALS_2P5V

◆ PWR_CR1_ALS_2P8V

◆ PWR_CR1_ALS_MASK

◆ PWR_CR1_ALS_SHIFT

| #define PWR_CR1_ALS_SHIFT 17 |

◆ PWR_CR1_AVD_READY

| #define PWR_CR1_AVD_READY BIT13 |

analog voltage ready This bit is only used when the analog switch boost needs to be enabled (see BOOSTE bit).

It must be set by software when the expected V DDA analog supply level is available. The correct analog supply level is indicated by the AVDO bit (PWR_CSR1 register) after setting the AVDEN bit and selecting the supply level to be monitored (ALS bits).

◆ PWR_CR1_AVDEN

| #define PWR_CR1_AVDEN BIT16 |

◆ PWR_CR1_AXIRAM1SO

| #define PWR_CR1_AXIRAM1SO BIT19 |

◆ PWR_CR1_AXIRAM2SO

| #define PWR_CR1_AXIRAM2SO BIT20 |

◆ PWR_CR1_AXIRAM3SO

| #define PWR_CR1_AXIRAM3SO BIT21 |

◆ PWR_CR1_BOOSTE

| #define PWR_CR1_BOOSTE BIT12 |

analog switch VBoost control This bit enables the booster to guarantee the analog switch AC performance when the V DD supply voltage is below 2.7 V (reduction of the total harmonic distortion to have the same switch performance over the full supply voltage range) The V DD supply voltage can be monitored through the PVD and the PLS bits.

◆ PWR_CR1_DBP

| #define PWR_CR1_DBP BIT8 |

◆ PWR_CR1_GFXSO

| #define PWR_CR1_GFXSO BIT25 |

◆ PWR_CR1_HSITFSO

| #define PWR_CR1_HSITFSO BIT26 |

◆ PWR_CR1_ITCMSO

| #define PWR_CR1_ITCMSO BIT24 |

◆ PWR_CR1_SRDRAMSO

| #define PWR_CR1_SRDRAMSO BIT27 |

◆ PWR_CR1_SVOS_MASK

◆ PWR_CR1_SVOS_SCALE_3

◆ PWR_CR1_SVOS_SCALE_4

◆ PWR_CR1_SVOS_SCALE_5

◆ PWR_CR1_SVOS_SHIFT

| #define PWR_CR1_SVOS_SHIFT 14 |

◆ PWR_CR2_BREN

◆ PWR_CR2_BRRDY

◆ PWR_CR2_MONEN

| #define PWR_CR2_MONEN BIT4 |

◆ PWR_CR2_TEMPH

| #define PWR_CR2_TEMPH BIT23 |

◆ PWR_CR2_TEMPL

| #define PWR_CR2_TEMPL BIT22 |

◆ PWR_CR3_BYPASS

◆ PWR_CR3_LDOEN

◆ PWR_CR3_SCUEN

◆ PWR_CR3_SMPSEN

◆ PWR_CR3_SMPSEXTHP

| #define PWR_CR3_SMPSEXTHP BIT3 |

◆ PWR_CR3_SMPSEXTRDY

| #define PWR_CR3_SMPSEXTRDY BIT16 |

◆ PWR_CR3_SMPSLEVEL_MASK

◆ PWR_CR3_SMPSLEVEL_SHIFT

◆ PWR_CR3_USB33DEN

◆ PWR_CR3_USB33RDY

◆ PWR_CR3_USBREGEN

◆ PWR_CR3_VBE

◆ PWR_CR3_VBRS

| #define PWR_CR3_VBRS BIT9 |

◆ PWR_CSR1_ACTVOS_SHIFT

◆ PWR_CSR1_ACTVOSRDY

◆ PWR_CSR1_AVDO

◆ PWR_CSR1_MMCVDO

◆ PWR_CSR1_PVDO

◆ PWR_D3CR_VOS_MASK

◆ PWR_D3CR_VOS_SCALE_0

| #define PWR_D3CR_VOS_SCALE_0 (0x0) |

◆ PWR_D3CR_VOS_SCALE_1

◆ PWR_D3CR_VOS_SCALE_2

◆ PWR_D3CR_VOS_SCALE_3

◆ PWR_D3CR_VOS_SHIFT

◆ PWR_D3CR_VOSRDY

◆ PWR_SRDCR_VOS_MASK

◆ PWR_SRDCR_VOS_SCALE_0

◆ PWR_SRDCR_VOS_SCALE_1

◆ PWR_SRDCR_VOS_SCALE_2

◆ PWR_SRDCR_VOS_SCALE_3

◆ PWR_SRDCR_VOS_SHIFT

◆ PWR_SRDCR_VOSRDY

Enumeration Type Documentation

◆ pwr_svos_scale

| enum pwr_svos_scale |

◆ pwr_sys_mode

| enum pwr_sys_mode |

◆ pwr_vos_scale

| enum pwr_vos_scale |