scb.h File Reference

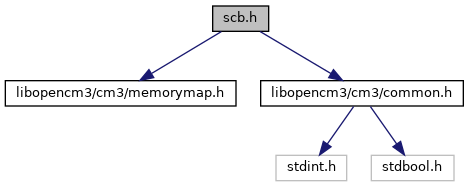

Include dependency graph for scb.h:

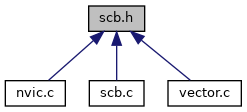

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | scb_exception_stack_frame |

Macros | |

| #define | SCB_CPUID MMIO32(SCB_BASE + 0x00) |

| CPUID: CPUID base register. More... | |

| #define | SCB_ICSR MMIO32(SCB_BASE + 0x04) |

| ICSR: Interrupt Control State Register. More... | |

| #define | SCB_VTOR MMIO32(SCB_BASE + 0x08) |

| VTOR: Vector Table Offset Register. More... | |

| #define | SCB_AIRCR MMIO32(SCB_BASE + 0x0C) |

| AIRCR: Application Interrupt and Reset Control Register. More... | |

| #define | SCB_SCR MMIO32(SCB_BASE + 0x10) |

| SCR: System Control Register. More... | |

| #define | SCB_CCR MMIO32(SCB_BASE + 0x14) |

| CCR: Configuration Control Register. More... | |

| #define | SCB_SHPR(ipr_id) MMIO8(SCS_BASE + 0xD18 + (ipr_id)) |

| System Handler Priority 8 bits Registers, SHPR1/2/3. More... | |

| #define | SCB_SHCSR MMIO32(SCB_BASE + 0x24) |

| SHCSR: System Handler Control and State Register. More... | |

| #define | SCB_DFSR MMIO32(SCB_BASE + 0x30) |

| DFSR: Debug Fault Status Register. More... | |

| #define | SCB_CFSR MMIO32(SCB_BASE + 0x28) |

| CFSR: Configurable Fault Status Registers. More... | |

| #define | SCB_HFSR MMIO32(SCB_BASE + 0x2C) |

| HFSR: Hard Fault Status Register. More... | |

| #define | SCB_MMFAR MMIO32(SCB_BASE + 0x34) |

| MMFAR: Memory Manage Fault Address Register. More... | |

| #define | SCB_BFAR MMIO32(SCB_BASE + 0x38) |

| BFAR: Bus Fault Address Register. More... | |

| #define | SCB_AFSR MMIO32(SCB_BASE + 0x3C) |

| AFSR: Auxiliary Fault Status Register. More... | |

| #define | SCB_ID_PFR0 MMIO32(SCB_BASE + 0x40) |

| ID_PFR0: Processor Feature Register 0. More... | |

| #define | SCB_ID_PFR1 MMIO32(SCB_BASE + 0x44) |

| ID_PFR1: Processor Feature Register 1. More... | |

| #define | SCB_ID_DFR0 MMIO32(SCB_BASE + 0x48) |

| ID_DFR0: Debug Features Register 0. More... | |

| #define | SCB_ID_AFR0 MMIO32(SCB_BASE + 0x4C) |

| ID_AFR0: Auxiliary Features Register 0. More... | |

| #define | SCB_ID_MMFR0 MMIO32(SCB_BASE + 0x50) |

| ID_MMFR0: Memory Model Feature Register 0. More... | |

| #define | SCB_ID_MMFR1 MMIO32(SCB_BASE + 0x54) |

| ID_MMFR1: Memory Model Feature Register 1. More... | |

| #define | SCB_ID_MMFR2 MMIO32(SCB_BASE + 0x58) |

| ID_MMFR2: Memory Model Feature Register 2. More... | |

| #define | SCB_ID_MMFR3 MMIO32(SCB_BASE + 0x5C) |

| ID_MMFR3: Memory Model Feature Register 3. More... | |

| #define | SCB_ID_ISAR0 MMIO32(SCB_BASE + 0x60) |

| ID_ISAR0: Instruction Set Attributes Register 0. More... | |

| #define | SCB_ID_ISAR1 MMIO32(SCB_BASE + 0x64) |

| ID_ISAR1: Instruction Set Attributes Register 1. More... | |

| #define | SCB_ID_ISAR2 MMIO32(SCB_BASE + 0x68) |

| ID_ISAR2: Instruction Set Attributes Register 2. More... | |

| #define | SCB_ID_ISAR3 MMIO32(SCB_BASE + 0x6C) |

| ID_ISAR3: Instruction Set Attributes Register 3. More... | |

| #define | SCB_ID_ISAR4 MMIO32(SCB_BASE + 0x70) |

| ID_ISAR4: Instruction Set Attributes Register 4. More... | |

| #define | SCB_CPACR MMIO32(SCB_BASE + 0x88) |

| CPACR: Coprocessor Access Control Register. More... | |

| #define | SCB_FPCCR MMIO32(SCB_BASE + 0x234) |

| FPCCR: Floating-Point Context Control Register. More... | |

| #define | SCB_FPCAR MMIO32(SCB_BASE + 0x238) |

| FPCAR: Floating-Point Context Address Register. More... | |

| #define | SCB_FPDSCR MMIO32(SCB_BASE + 0x23C) |

| FPDSCR: Floating-Point Default Status Control Register. More... | |

| #define | SCB_MVFR0 MMIO32(SCB_BASE + 0x240) |

| MVFR0: Media and Floating-Point Feature Register 0. More... | |

| #define | SCB_MVFR1 MMIO32(SCB_BASE + 0x244) |

| MVFR1: Media and Floating-Point Feature Register 1. More... | |

| #define | SCB_CPUID_IMPLEMENTER_LSB 24 |

| Implementer[31:24]: Implementer code. More... | |

| #define | SCB_CPUID_IMPLEMENTER (0xFF << SCB_CPUID_IMPLEMENTER_LSB) |

| #define | SCB_CPUID_VARIANT_LSB 20 |

| Variant[23:20]: Variant number. More... | |

| #define | SCB_CPUID_VARIANT (0xF << SCB_CPUID_VARIANT_LSB) |

| #define | SCB_CPUID_CONSTANT_LSB 16 |

| Constant[19:16] Reads as 0xF (ARMv7-M) M3, M4 Reads as 0xC (ARMv6-M) M0, M0+. More... | |

| #define | SCB_CPUID_CONSTANT (0xF << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_CONSTANT_ARMV6 (0xC << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_CONSTANT_ARMV7 (0xF << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_PARTNO_LSB 4 |

| PartNo[15:4]: Part number of the processor. More... | |

| #define | SCB_CPUID_PARTNO (0xFFF << SCB_CPUID_PARTNO_LSB) |

| #define | SCB_CPUID_REVISION_LSB 0 |

| Revision[3:0]: Revision number. More... | |

| #define | SCB_CPUID_REVISION (0xF << SCB_CPUID_REVISION_LSB) |

| #define | SCB_ICSR_NMIPENDSET (1 << 31) |

| NMIPENDSET: NMI set-pending bit. More... | |

| #define | SCB_ICSR_PENDSVSET (1 << 28) |

| PENDSVSET: PendSV set-pending bit. More... | |

| #define | SCB_ICSR_PENDSVCLR (1 << 27) |

| PENDSVCLR: PendSV clear-pending bit. More... | |

| #define | SCB_ICSR_PENDSTSET (1 << 26) |

| PENDSTSET: SysTick exception set-pending bit. More... | |

| #define | SCB_ICSR_PENDSTCLR (1 << 25) |

| PENDSTCLR: SysTick exception clear-pending bit. More... | |

| #define | SCB_ICSR_ISRPREEMPT (1 << 23) |

| Bit 23: reserved for debug - reads as 0 when not in debug mode. More... | |

| #define | SCB_ICSR_ISRPENDING (1 << 22) |

| ISRPENDING: Interrupt pending flag, excluding NMI and Faults. More... | |

| #define | SCB_ICSR_VECTPENDING_LSB 12 |

| VECTPENDING[21:12] Pending vector. More... | |

| #define | SCB_ICSR_VECTPENDING (0x1FF << SCB_ICSR_VECTPENDING_LSB) |

| #define | SCB_ICSR_RETOBASE (1 << 11) |

| RETOBASE: Return to base level. More... | |

| #define | SCB_ICSR_VECTACTIVE_LSB 0 |

| VECTACTIVE[8:0] Active vector. More... | |

| #define | SCB_ICSR_VECTACTIVE (0x1FF << SCB_ICSR_VECTACTIVE_LSB) |

| #define | SCB_VTOR_TBLOFF_LSB 9 |

| #define | SCB_VTOR_TBLOFF (0x7FFFFF << SCB_VTOR_TBLOFF_LSB) |

| #define | SCB_AIRCR_VECTKEYSTAT_LSB 16 |

| VECTKEYSTAT[31:16]/ VECTKEY[31:16] Register key. More... | |

| #define | SCB_AIRCR_VECTKEYSTAT (0xFFFF << SCB_AIRCR_VECTKEYSTAT_LSB) |

| #define | SCB_AIRCR_VECTKEY (0x05FA << SCB_AIRCR_VECTKEYSTAT_LSB) |

| #define | SCB_AIRCR_ENDIANESS (1 << 15) |

| ENDIANNESS Data endianness bit. More... | |

| #define | SCB_AIRCR_PRIGROUP_GROUP16_NOSUB (0x3 << 8) |

| PRIGROUP[10:8]: Interrupt priority grouping field. More... | |

| #define | SCB_AIRCR_PRIGROUP_GROUP8_SUB2 (0x4 << 8) |

| #define | SCB_AIRCR_PRIGROUP_GROUP4_SUB4 (0x5 << 8) |

| #define | SCB_AIRCR_PRIGROUP_GROUP2_SUB8 (0x6 << 8) |

| #define | SCB_AIRCR_PRIGROUP_NOGROUP_SUB16 (0x7 << 8) |

| #define | SCB_AIRCR_PRIGROUP_MASK (0x7 << 8) |

| #define | SCB_AIRCR_PRIGROUP_SHIFT 8 |

| #define | SCB_AIRCR_SYSRESETREQ (1 << 2) |

| SYSRESETREQ System reset request. More... | |

| #define | SCB_AIRCR_VECTCLRACTIVE (1 << 1) |

| VECTCLRACTIVE clears state information for exceptions. More... | |

| #define | SCB_AIRCR_VECTRESET (1 << 0) |

| VECTRESET cause local system reset. More... | |

| #define | SCB_SCR_SEVONPEND (1 << 4) |

| SEVONPEND Send Event on Pending bit. More... | |

| #define | SCB_SCR_SLEEPDEEP (1 << 2) |

| SLEEPDEEP implementation defined. More... | |

| #define | SCB_SCR_SLEEPONEXIT (1 << 1) |

| SLEEPONEXIT sleep when exiting ISR. More... | |

| #define | SCB_CCR_STKALIGN (1 << 9) |

| STKALIGN set to zero to break things :) More... | |

| #define | SCB_CCR_BFHFNMIGN (1 << 8) |

| BFHFNMIGN set to attempt ignoring faults in handlers. More... | |

| #define | SCB_CCR_DIV_0_TRP (1 << 4) |

| DIV_0_TRP set to trap on divide by zero. More... | |

| #define | SCB_CCR_UNALIGN_TRP (1 << 3) |

| UNALIGN_TRP set to trap on unaligned. More... | |

| #define | SCB_CCR_USERSETMPEND (1 << 1) |

| USERSETMPEND set to allow unprivileged access to STIR. More... | |

| #define | SCB_CCR_NONBASETHRDENA (1 << 0) |

| NONBASETHRDENA set to allow non base priority threads. More... | |

| #define | SCB_SHPR_PRI_4_MEMMANAGE 0 |

| #define | SCB_SHPR_PRI_5_BUSFAULT 1 |

| #define | SCB_SHPR_PRI_6_USAGEFAULT 2 |

| #define | SCB_SHPR_PRI_7_RESERVED 3 |

| #define | SCB_SHPR_PRI_8_RESERVED 4 |

| #define | SCB_SHPR_PRI_9_RESERVED 5 |

| #define | SCB_SHPR_PRI_10_RESERVED 6 |

| #define | SCB_SHPR_PRI_11_SVCALL 7 |

| #define | SCB_SHPR_PRI_12_RESERVED 8 |

| #define | SCB_SHPR_PRI_13_RESERVED 9 |

| #define | SCB_SHPR_PRI_14_PENDSV 10 |

| #define | SCB_SHPR_PRI_15_SYSTICK 11 |

| #define | SCB_SHCSR_USGFAULTENA (1 << 18) |

| #define | SCB_SHCSR_BUSFAULTENA (1 << 17) |

| #define | SCB_SHCSR_MEMFAULTENA (1 << 16) |

| #define | SCB_SHCSR_SVCALLPENDED (1 << 15) |

| #define | SCB_SHCSR_BUSFAULTPENDED (1 << 14) |

| #define | SCB_SHCSR_MEMFAULTPENDED (1 << 13) |

| #define | SCB_SHCSR_USGFAULTPENDED (1 << 12) |

| #define | SCB_SHCSR_SYSTICKACT (1 << 11) |

| #define | SCB_SHCSR_PENDSVACT (1 << 10) |

| #define | SCB_SHCSR_MONITORACT (1 << 8) |

| #define | SCB_SHCSR_SVCALLACT (1 << 7) |

| #define | SCB_SHCSR_USGFAULTACT (1 << 3) |

| #define | SCB_SHCSR_BUSFAULTACT (1 << 1) |

| #define | SCB_SHCSR_MEMFAULTACT (1 << 0) |

| #define | SCB_CFSR_DIVBYZERO (1 << 25) |

| #define | SCB_CFSR_UNALIGNED (1 << 24) |

| #define | SCB_CFSR_NOCP (1 << 19) |

| #define | SCB_CFSR_INVPC (1 << 18) |

| #define | SCB_CFSR_INVSTATE (1 << 17) |

| #define | SCB_CFSR_UNDEFINSTR (1 << 16) |

| #define | SCB_CFSR_BFARVALID (1 << 15) |

| #define | SCB_CFSR_STKERR (1 << 12) |

| #define | SCB_CFSR_UNSTKERR (1 << 11) |

| #define | SCB_CFSR_IMPRECISERR (1 << 10) |

| #define | SCB_CFSR_PRECISERR (1 << 9) |

| #define | SCB_CFSR_IBUSERR (1 << 8) |

| #define | SCB_CFSR_MMARVALID (1 << 7) |

| #define | SCB_CFSR_MSTKERR (1 << 4) |

| #define | SCB_CFSR_MUNSTKERR (1 << 3) |

| #define | SCB_CFSR_DACCVIOL (1 << 1) |

| #define | SCB_CFSR_IACCVIOL (1 << 0) |

| #define | SCB_HFSR_DEBUG_VT (1 << 31) |

| #define | SCB_HFSR_FORCED (1 << 30) |

| #define | SCB_HFSR_VECTTBL (1 << 1) |

| #define | SCB_CPACR_NONE 0 /* Access denied */ |

| #define | SCB_CPACR_PRIV 1 /* Privileged access only */ |

| #define | SCB_CPACR_FULL 3 /* Full access */ |

| #define | SCB_CPACR_CP10 (1 << 20) |

| #define | SCB_CPACR_CP11 (1 << 22) |

| #define | SCB_GET_EXCEPTION_STACK_FRAME(f) |

Functions | |

| void | scb_reset_system (void) |

| void | scb_reset_core (void) |

| void | scb_set_priority_grouping (uint32_t prigroup) |