usb.h File Reference

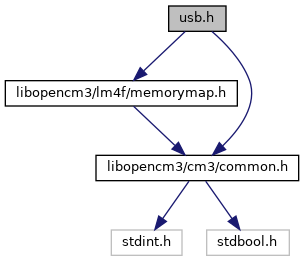

Include dependency graph for usb.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | USB_FADDR MMIO8(USB_BASE + 0x00) |

| #define | USB_POWER MMIO8(USB_BASE + 0x01) |

| #define | USB_TXIS MMIO16(USB_BASE + 0x02) |

| #define | USB_RXIS MMIO16(USB_BASE + 0x04) |

| #define | USB_TXIE MMIO16(USB_BASE + 0x06) |

| #define | USB_RXIE MMIO16(USB_BASE + 0x08) |

| #define | USB_IS MMIO8(USB_BASE + 0x0A) |

| #define | USB_IE MMIO8(USB_BASE + 0x0B) |

| #define | USB_FRAME MMIO16(USB_BASE + 0x0C) |

| #define | USB_EPIDX MMIO8(USB_BASE + 0x0E) |

| #define | USB_TEST MMIO8(USB_BASE + 0x0F) |

| #define | USB_FIFO8(n) MMIO8(USB_BASE + 0x20 + (n)*0x04) |

| #define | USB_FIFO16(n) MMIO16(USB_BASE + 0x20 + (n)*0x04) |

| #define | USB_FIFO32(n) MMIO32(USB_BASE + 0x20 + (n)*0x04) |

| #define | USB_TXFIFOSZ MMIO8(USB_BASE + 0x62) |

| #define | USB_RXFIFOSZ MMIO8(USB_BASE + 0x63) |

| #define | USB_TXFIFOADD MMIO16(USB_BASE + 0x64) |

| #define | USB_RXFIFOADD MMIO16(USB_BASE + 0x66) |

| #define | USB_CONTIM MMIO8(USB_BASE + 0x7A) |

| #define | USB_FSEOF MMIO8(USB_BASE + 0x7D) |

| #define | USB_LSEOF MMIO8(USB_BASE + 0x7E) |

| #define | USB_CSRL0 MMIO8(USB_BASE + 0x102) |

| #define | USB_CSRH0 MMIO8(USB_BASE + 0x103) |

| #define | USB_COUNT0 MMIO8(USB_BASE + 0x108) |

| #define | USB_TXMAXP(n) MMIO16(USB_BASE + 0x100 + (n)*0x10) |

| #define | USB_TXCSRL(n) MMIO8(USB_BASE + 0x102 + (n)*0x10) |

| #define | USB_TXCSRH(n) MMIO8(USB_BASE + 0x103 + (n)*0x10) |

| #define | USB_RXMAXP(n) MMIO16(USB_BASE + 0x104 + (n)*0x10) |

| #define | USB_RXCSRL(n) MMIO8(USB_BASE + 0x106 + (n)*0x10) |

| #define | USB_RXCSRH(n) MMIO8(USB_BASE + 0x107 + (n)*0x10) |

| #define | USB_RXCOUNT(n) MMIO16(USB_BASE + 0x108 + (n)*0x10) |

| #define | USB_RXDPKTBUFDIS MMIO16(USB_BASE + 0x340) |

| #define | USB_TXDPKTBUFDIS MMIO16(USB_BASE + 0x342) |

| #define | USB_DRRIS MMIO32(USB_BASE + 0x410) |

| #define | USB_DRIM MMIO32(USB_BASE + 0x414) |

| #define | USB_DRISC MMIO32(USB_BASE + 0x418) |

| #define | USB_DMASEL MMIO32(USB_BASE + 0x450) |

| #define | USB_PP MMIO32(USB_BASE + 0xFC0) |

| #define | USB_FADDR_FUNCADDR_MASK (0x3f << 0) |

| Function Address. More... | |

| #define | USB_POWER_ISOUP (1 << 7) |

| Isochronous Update. More... | |

| #define | USB_POWER_SOFTCONN (1 << 6) |

| Soft Connect/Disconnect. More... | |

| #define | USB_POWER_RESET (1 << 3) |

| RESET signaling. More... | |

| #define | USB_POWER_RESUME (1 << 2) |

| RESUME signaling. More... | |

| #define | USB_POWER_SUSPEND (1 << 1) |

| SUSPEND mode. More... | |

| #define | USB_POWER_PWRDNPHY (1 << 0) |

| Power down PHY. More... | |

| #define | USB_EP7 (1 << 7) |

| #define | USB_EP6 (1 << 6) |

| #define | USB_EP5 (1 << 5) |

| #define | USB_EP4 (1 << 4) |

| #define | USB_EP3 (1 << 3) |

| #define | USB_EP2 (1 << 2) |

| #define | USB_EP1 (1 << 1) |

| #define | USB_EP0 (1 << 0) |

| #define | USB_IM_DISCON (1 << 5) |

| USB disconnect interrupt. More... | |

| #define | USB_IM_SOF (1 << 3) |

| Start of frame. More... | |

| #define | USB_IM_RESET (1 << 2) |

| RESET signaling detected. More... | |

| #define | USB_IM_RESUME (1 << 1) |

| RESUME signaling detected. More... | |

| #define | USB_IM_SUSPEND (1 << 0) |

| SUSPEND signaling detected. More... | |

| #define | USB_FRAME_MASK (0x03FF) |

| Frame number. More... | |

| #define | USB_EPIDX_MASK (0x0F) |

| Endpoint Index. More... | |

| #define | USB_TEST_FIFOACC (1 << 6) |

| FIFO access. More... | |

| #define | USB_TEST_FORCEFS (1 << 5) |

| Force full-speed mode. More... | |

| #define | USB_FIFOSZ_DPB (1 << 4) |

| Double packet buffer support. More... | |

| #define | USB_FIFOSZ_SIZE_MASK (0x0F << 0) |

| #define | USB_FIFOSZ_SIZE_8 (0x00 << 0) |

| #define | USB_FIFOSZ_SIZE_16 (0x01 << 0) |

| #define | USB_FIFOSZ_SIZE_32 (0x02 << 0) |

| #define | USB_FIFOSZ_SIZE_64 (0x03 << 0) |

| #define | USB_FIFOSZ_SIZE_128 (0x04 << 0) |

| #define | USB_FIFOSZ_SIZE_256 (0x05 << 0) |

| #define | USB_FIFOSZ_SIZE_512 (0x06 << 0) |

| #define | USB_FIFOSZ_SIZE_1024 (0x07 << 0) |

| #define | USB_FIFOSZ_SIZE_2048 (0x08 << 0) |

| #define | USB_CONTIM_WTCON_MASK (0x0F << 4) |

| Connect wait. More... | |

| #define | USB_CONTIM_WTID_MASK (0x0F << 0) |

| Wait ID. More... | |

| #define | USB_CSRL0_SETENDC (1 << 7) |

| Setup End Clear. More... | |

| #define | USB_CSRL0_RXRDYC (1 << 6) |

| RXRDY Clear. More... | |

| #define | USB_CSRL0_STALL (1 << 5) |

| Send Stall. More... | |

| #define | USB_CSRL0_SETEND (1 << 4) |

| Setup End. More... | |

| #define | USB_CSRL0_DATAEND (1 << 3) |

| Data End. More... | |

| #define | USB_CSRL0_STALLED (1 << 2) |

| Endpoint Stalled. More... | |

| #define | USB_CSRL0_TXRDY (1 << 1) |

| Transmit Packet Ready. More... | |

| #define | USB_CSRL0_RXRDY (1 << 0) |

| Receive Packet Ready. More... | |

| #define | USB_CSRH0_FLUSH (1 << 0) |

| Flush FIFO. More... | |

| #define | USB_TXCSRL_CLRDT (1 << 6) |

| Clear data toggle. More... | |

| #define | USB_TXCSRL_STALLED (1 << 5) |

| Endpoint Stalled. More... | |

| #define | USB_TXCSRL_STALL (1 << 4) |

| Send Stall. More... | |

| #define | USB_TXCSRL_FLUSH (1 << 3) |

| Flush FIFO. More... | |

| #define | USB_TXCSRL_UNDRN (1 << 2) |

| Underrun. More... | |

| #define | USB_TXCSRL_FIFONE (1 << 1) |

| FIFO not empty. More... | |

| #define | USB_TXCSRL_TXRDY (1 << 0) |

| Transmit Packet Ready. More... | |

| #define | USB_TXCSRH_AUTOSET (1 << 7) |

| Auto set. More... | |

| #define | USB_TXCSRH_ISO (1 << 6) |

| Isochronous transfers. More... | |

| #define | USB_TXCSRH_MODE (1 << 5) |

| Mode. More... | |

| #define | USB_TXCSRH_DMAEN (1 << 4) |

| DMA request enable. More... | |

| #define | USB_TXCSRH_FDT (1 << 3) |

| Force data toggle. More... | |

| #define | USB_TXCSRH_DMAMOD (1 << 2) |

| DMA request mode. More... | |

| #define | USB_RXCSRL_CLRDT (1 << 7) |

| Clear data toggle. More... | |

| #define | USB_RXCSRL_STALLED (1 << 6) |

| Endpoint Stalled. More... | |

| #define | USB_RXCSRL_STALL (1 << 5) |

| Send Stall. More... | |

| #define | USB_RXCSRL_FLUSH (1 << 4) |

| Flush FIFO. More... | |

| #define | USB_RXCSRL_DATAERR (1 << 2) |

| Data error. More... | |

| #define | USB_RXCSRL_OVER (1 << 2) |

| Overrun. More... | |

| #define | USB_RXCSRL_FULL (1 << 1) |

| FIFO full. More... | |

| #define | USB_RXCSRL_RXRDY (1 << 0) |

| Receive Packet Ready. More... | |

| #define | USB_RXCSRH_AUTOCL (1 << 7) |

| Auto clear. More... | |

| #define | USB_RXCSRH_ISO (1 << 6) |

| Isochronous transfers. More... | |

| #define | USB_RXCSRH_DMAEN (1 << 5) |

| DMA request enable. More... | |

| #define | USB_RXCSRH_PIDERR (1 << 4) |

| Disable NYET / PID error. More... | |

| #define | USB_RXCSRH_DMAMOD (1 << 3) |

| DMA request mode. More... | |

| #define | USB_DRRIS_RESUME (1 << 0) |

| RESUME interrupt status. More... | |

| #define | USB_DRIM_RESUME (1 << 0) |

| RESUME interrupt mask. More... | |

| #define | USB_DRISC_RESUME (1 << 0) |

| RESUME interrupt status and clear. More... | |

| #define | USB_PP_ECNT_MASK (0xFF << 8) |

| Endpoint count. More... | |

| #define | USB_PP_USB_MASK (0x03 << 6) |

| USB capability. More... | |

| #define | USB_PP_USB_NA (0x00 << 6) |

| #define | USB_PP_USB_DEVICE (0x01 << 6) |

| #define | USB_PP_USB_HOST (0x02 << 6) |

| #define | USB_PP_USB_OTG (0x03 << 6) |

| #define | USB_PP_PHY (1 << 4) |

| PHY present. More... | |

| #define | USB_PP_TYPE_MASK (0x0F << 0) |

| Controller type. More... | |

Enumerations | |

| enum | usb_interrupt { USB_INT_DISCON = USB_IM_DISCON , USB_INT_SOF = USB_IM_SOF , USB_INT_RESET = USB_IM_RESET , USB_INT_RESUME = USB_IM_RESUME , USB_INT_SUSPEND = USB_IM_SUSPEND } |

| enum | usb_ep_interrupt { USB_EP0_INT = USB_EP0 , USB_EP1_INT = USB_EP1 , USB_EP2_INT = USB_EP2 , USB_EP3_INT = USB_EP3 , USB_EP4_INT = USB_EP4 , USB_EP5_INT = USB_EP5 , USB_EP6_INT = USB_EP6 , USB_EP7_INT = USB_EP7 } |

Functions | |

| void | usb_enable_interrupts (enum usb_interrupt ints, enum usb_ep_interrupt rx_ints, enum usb_ep_interrupt tx_ints) |

| Enable Specific USB Interrupts. More... | |

| void | usb_disable_interrupts (enum usb_interrupt ints, enum usb_ep_interrupt rx_ints, enum usb_ep_interrupt tx_ints) |

| Disable Specific USB Interrupts. More... | |