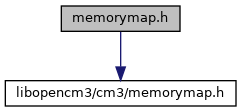

#include <libopencm3/cm3/memorymap.h>

Go to the source code of this file.

Macro Definition Documentation

◆ ADC_BASE

| #define ADC_BASE (PERIPH_BASE_APB0 + 0x34000) |

Definition at line 57 of file lpc17xx/memorymap.h.

◆ CAN1_BASE

| #define CAN1_BASE (PERIPH_BASE_APB0 + 0x44000) |

Definition at line 61 of file lpc17xx/memorymap.h.

◆ CAN2_BASE

| #define CAN2_BASE (PERIPH_BASE_APB0 + 0x48000) |

Definition at line 62 of file lpc17xx/memorymap.h.

◆ CANAFRAM_BASE

| #define CANAFRAM_BASE (PERIPH_BASE_APB0 + 0x38000) |

Definition at line 58 of file lpc17xx/memorymap.h.

◆ CANAFREG_BASE

| #define CANAFREG_BASE (PERIPH_BASE_APB0 + 0x3C000) |

Definition at line 59 of file lpc17xx/memorymap.h.

◆ CANCOMMONREG_BASE

| #define CANCOMMONREG_BASE (PERIPH_BASE_APB0 + 0x40000) |

Definition at line 60 of file lpc17xx/memorymap.h.

◆ DAC_BASE

| #define DAC_BASE (PERIPH_BASE_APB1 + 0x0c000) |

Definition at line 70 of file lpc17xx/memorymap.h.

◆ ETHERNET_BASE

| #define ETHERNET_BASE (PERIPH_BASE_AHB + 0x00000) |

Definition at line 87 of file lpc17xx/memorymap.h.

◆ GPDMA_BASE

| #define GPDMA_BASE (PERIPH_BASE_AHB + 0x04000) |

Definition at line 88 of file lpc17xx/memorymap.h.

◆ GPIO_PIO0_BASE

| #define GPIO_PIO0_BASE (PERIPH_BASE_GPIO + 0x00) |

Definition at line 37 of file lpc17xx/memorymap.h.

◆ GPIO_PIO1_BASE

| #define GPIO_PIO1_BASE (PERIPH_BASE_GPIO + 0x20) |

Definition at line 38 of file lpc17xx/memorymap.h.

◆ GPIO_PIO2_BASE

| #define GPIO_PIO2_BASE (PERIPH_BASE_GPIO + 0x40) |

Definition at line 39 of file lpc17xx/memorymap.h.

◆ GPIO_PIO3_BASE

| #define GPIO_PIO3_BASE (PERIPH_BASE_GPIO + 0x60) |

Definition at line 40 of file lpc17xx/memorymap.h.

◆ GPIO_PIO4_BASE

| #define GPIO_PIO4_BASE (PERIPH_BASE_GPIO + 0x80) |

Definition at line 41 of file lpc17xx/memorymap.h.

◆ GPIOINTERRUPT_BASE

| #define GPIOINTERRUPT_BASE (PERIPH_BASE_APB0 + 0x28000) |

Definition at line 54 of file lpc17xx/memorymap.h.

◆ I2C0_BASE

| #define I2C0_BASE (PERIPH_BASE_APB0 + 0x1c000) |

Definition at line 51 of file lpc17xx/memorymap.h.

◆ I2C1_BASE

| #define I2C1_BASE (PERIPH_BASE_APB0 + 0x5C000) |

Definition at line 64 of file lpc17xx/memorymap.h.

◆ I2C2_BASE

| #define I2C2_BASE (PERIPH_BASE_APB1 + 0x20000) |

Definition at line 75 of file lpc17xx/memorymap.h.

◆ I2S_BASE

| #define I2S_BASE (PERIPH_BASE_APB1 + 0x28000) |

Definition at line 77 of file lpc17xx/memorymap.h.

◆ MCPWM_BASE

| #define MCPWM_BASE (PERIPH_BASE_APB1 + 0x38000) |

Definition at line 81 of file lpc17xx/memorymap.h.

◆ PERIPH_BASE_AHB

| #define PERIPH_BASE_AHB (0x50000000U) |

Definition at line 32 of file lpc17xx/memorymap.h.

◆ PERIPH_BASE_APB0

| #define PERIPH_BASE_APB0 (0x40000000U) |

Definition at line 30 of file lpc17xx/memorymap.h.

◆ PERIPH_BASE_APB1

| #define PERIPH_BASE_APB1 (0x40080000U) |

Definition at line 31 of file lpc17xx/memorymap.h.

◆ PERIPH_BASE_GPIO

| #define PERIPH_BASE_GPIO (0x2009C000U) |

Definition at line 29 of file lpc17xx/memorymap.h.

◆ PINCONNECT_BASE

| #define PINCONNECT_BASE (PERIPH_BASE_APB0 + 0x2c000) |

Definition at line 55 of file lpc17xx/memorymap.h.

◆ PWM1_BASE

| #define PWM1_BASE (PERIPH_BASE_APB0 + 0x18000) |

Definition at line 50 of file lpc17xx/memorymap.h.

◆ QEI_BASE

| #define QEI_BASE (PERIPH_BASE_APB1 + 0x3c000) |

Definition at line 82 of file lpc17xx/memorymap.h.

◆ RIT_BASE

| #define RIT_BASE (PERIPH_BASE_APB1 + 0x30000) |

Definition at line 79 of file lpc17xx/memorymap.h.

◆ RTC_BASE

| #define RTC_BASE (PERIPH_BASE_APB0 + 0x24000) |

Definition at line 53 of file lpc17xx/memorymap.h.

◆ SPI_BASE

| #define SPI_BASE (PERIPH_BASE_APB0 + 0x20000) |

Definition at line 52 of file lpc17xx/memorymap.h.

◆ SSP0_BASE

| #define SSP0_BASE (PERIPH_BASE_APB1 + 0x08000) |

Definition at line 69 of file lpc17xx/memorymap.h.

◆ SSP1_BASE

| #define SSP1_BASE (PERIPH_BASE_APB0 + 0x30000) |

Definition at line 56 of file lpc17xx/memorymap.h.

◆ SYSCON_BASE

| #define SYSCON_BASE (PERIPH_BASE_APB1 + 0x7c000) |

Definition at line 84 of file lpc17xx/memorymap.h.

◆ TIMER0_BASE

| #define TIMER0_BASE (PERIPH_BASE_APB0 + 0x04000) |

Definition at line 45 of file lpc17xx/memorymap.h.

◆ TIMER1_BASE

| #define TIMER1_BASE (PERIPH_BASE_APB0 + 0x08000) |

Definition at line 46 of file lpc17xx/memorymap.h.

◆ TIMER2_BASE

| #define TIMER2_BASE (PERIPH_BASE_APB1 + 0x10000) |

Definition at line 71 of file lpc17xx/memorymap.h.

◆ TIMER3_BASE

| #define TIMER3_BASE (PERIPH_BASE_APB1 + 0x14000) |

Definition at line 72 of file lpc17xx/memorymap.h.

◆ UART0_BASE

| #define UART0_BASE (PERIPH_BASE_APB0 + 0x0c000) |

Definition at line 47 of file lpc17xx/memorymap.h.

◆ UART1_BASE

| #define UART1_BASE (PERIPH_BASE_APB0 + 0x10000) |

Definition at line 48 of file lpc17xx/memorymap.h.

◆ UART2_BASE

| #define UART2_BASE (PERIPH_BASE_APB1 + 0x18000) |

Definition at line 73 of file lpc17xx/memorymap.h.

◆ UART3_BASE

| #define UART3_BASE (PERIPH_BASE_APB1 + 0x1c000) |

Definition at line 74 of file lpc17xx/memorymap.h.

◆ USB_BASE

| #define USB_BASE (PERIPH_BASE_AHB + 0x0c000) |

Definition at line 90 of file lpc17xx/memorymap.h.

◆ WDT_BASE

| #define WDT_BASE (PERIPH_BASE_APB0 + 0x00000) |

Definition at line 44 of file lpc17xx/memorymap.h.