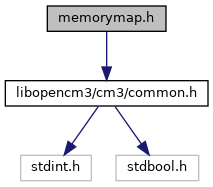

#include <libopencm3/cm3/common.h>

Go to the source code of this file.

Macros | |

| #define | PERIPH_BASE_AHB (0x40000000U) |

| #define | PERIPH_BASE_APB0 (0x40080000U) |

| #define | PERIPH_BASE_APB1 (0x400A0000U) |

| #define | PERIPH_BASE_APB2 (0x400C0000U) |

| #define | PERIPH_BASE_APB3 (0x400E0000U) |

| #define | SCT_BASE (PERIPH_BASE_AHB + 0x00000) |

| #define | GPDMA_BASE (PERIPH_BASE_AHB + 0x02000) |

| #define | SPIFI_BASE (PERIPH_BASE_AHB + 0x03000) |

| #define | SDIO_BASE (PERIPH_BASE_AHB + 0x04000) |

| #define | EMC_BASE (PERIPH_BASE_AHB + 0x05000) |

| #define | USB0_BASE (PERIPH_BASE_AHB + 0x06000) |

| #define | USB1_BASE (PERIPH_BASE_AHB + 0x07000) |

| #define | LCD_BASE (PERIPH_BASE_AHB + 0x08000) |

| #define | ETHERNET_BASE (PERIPH_BASE_AHB + 0x10000) |

| #define | ATIMER_BASE (0x40040000U) |

| #define | BACKUP_REG_BASE (0x40041000U) |

| #define | PMC_BASE (0x40042000U) |

| #define | CREG_BASE (0x40043000U) |

| #define | EVENTROUTER_BASE (0x40044000U) |

| #define | OTP_BASE (0x40045000U) |

| #define | RTC_BASE (0x40046000U) |

| #define | CGU_BASE (0x40050000U) |

| #define | CCU1_BASE (0x40051000U) |

| #define | CCU2_BASE (0x40052000U) |

| #define | RGU_BASE (0x40053000U) |

| #define | WWDT_BASE (PERIPH_BASE_APB0 + 0x00000) |

| #define | USART0_BASE (PERIPH_BASE_APB0 + 0x01000) |

| #define | UART1_BASE (PERIPH_BASE_APB0 + 0x02000) |

| #define | SSP0_BASE (PERIPH_BASE_APB0 + 0x03000) |

| #define | TIMER0_BASE (PERIPH_BASE_APB0 + 0x04000) |

| #define | TIMER1_BASE (PERIPH_BASE_APB0 + 0x05000) |

| #define | SCU_BASE (PERIPH_BASE_APB0 + 0x06000) |

| #define | GPIO_PIN_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x07000) |

| #define | GPIO_GROUP0_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x08000) |

| #define | GPIO_GROUP1_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x09000) |

| #define | MCPWM_BASE (PERIPH_BASE_APB1 + 0x00000) |

| #define | I2C0_BASE (PERIPH_BASE_APB1 + 0x01000) |

| #define | I2S0_BASE (PERIPH_BASE_APB1 + 0x02000) |

| #define | I2S1_BASE (PERIPH_BASE_APB1 + 0x03000) |

| #define | C_CCAN1_BASE (PERIPH_BASE_APB1 + 0x04000) |

| #define | RITIMER_BASE (PERIPH_BASE_APB2 + 0x00000) |

| #define | USART2_BASE (PERIPH_BASE_APB2 + 0x01000) |

| #define | USART3_BASE (PERIPH_BASE_APB2 + 0x02000) |

| #define | TIMER2_BASE (PERIPH_BASE_APB2 + 0x03000) |

| #define | TIMER3_BASE (PERIPH_BASE_APB2 + 0x04000) |

| #define | SSP1_BASE (PERIPH_BASE_APB2 + 0x05000) |

| #define | QEI_BASE (PERIPH_BASE_APB2 + 0x06000) |

| #define | GIMA_BASE (PERIPH_BASE_APB2 + 0x07000) |

| #define | I2C1_BASE (PERIPH_BASE_APB3 + 0x00000) |

| #define | DAC_BASE (PERIPH_BASE_APB3 + 0x01000) |

| #define | C_CAN0_BASE (PERIPH_BASE_APB3 + 0x02000) |

| #define | ADC0_BASE (PERIPH_BASE_APB3 + 0x03000) |

| #define | ADC1_BASE (PERIPH_BASE_APB3 + 0x04000) |

| #define | AES_BASE (0x400F1000U) |

| #define | GPIO_PORT_BASE (0x400F4000U) |

| #define | SPI_PORT_BASE (0x40100000U) |

| #define | SGPIO_PORT_BASE (0x40101000U) |

Macro Definition Documentation

◆ ADC0_BASE

| #define ADC0_BASE (PERIPH_BASE_APB3 + 0x03000) |

Definition at line 113 of file lpc43xx/memorymap.h.

◆ ADC1_BASE

| #define ADC1_BASE (PERIPH_BASE_APB3 + 0x04000) |

Definition at line 114 of file lpc43xx/memorymap.h.

◆ AES_BASE

| #define AES_BASE (0x400F1000U) |

Definition at line 119 of file lpc43xx/memorymap.h.

◆ ATIMER_BASE

| #define ATIMER_BASE (0x40040000U) |

Definition at line 53 of file lpc43xx/memorymap.h.

◆ BACKUP_REG_BASE

| #define BACKUP_REG_BASE (0x40041000U) |

Definition at line 54 of file lpc43xx/memorymap.h.

◆ C_CAN0_BASE

| #define C_CAN0_BASE (PERIPH_BASE_APB3 + 0x02000) |

Definition at line 112 of file lpc43xx/memorymap.h.

◆ C_CCAN1_BASE

| #define C_CCAN1_BASE (PERIPH_BASE_APB1 + 0x04000) |

Definition at line 91 of file lpc43xx/memorymap.h.

◆ CCU1_BASE

| #define CCU1_BASE (0x40051000U) |

Definition at line 64 of file lpc43xx/memorymap.h.

◆ CCU2_BASE

| #define CCU2_BASE (0x40052000U) |

Definition at line 65 of file lpc43xx/memorymap.h.

◆ CGU_BASE

| #define CGU_BASE (0x40050000U) |

Definition at line 63 of file lpc43xx/memorymap.h.

◆ CREG_BASE

| #define CREG_BASE (0x40043000U) |

Definition at line 56 of file lpc43xx/memorymap.h.

◆ DAC_BASE

| #define DAC_BASE (PERIPH_BASE_APB3 + 0x01000) |

Definition at line 111 of file lpc43xx/memorymap.h.

◆ EMC_BASE

| #define EMC_BASE (PERIPH_BASE_AHB + 0x05000) |

Definition at line 43 of file lpc43xx/memorymap.h.

◆ ETHERNET_BASE

| #define ETHERNET_BASE (PERIPH_BASE_AHB + 0x10000) |

Definition at line 48 of file lpc43xx/memorymap.h.

◆ EVENTROUTER_BASE

| #define EVENTROUTER_BASE (0x40044000U) |

Definition at line 57 of file lpc43xx/memorymap.h.

◆ GIMA_BASE

| #define GIMA_BASE (PERIPH_BASE_APB2 + 0x07000) |

Definition at line 104 of file lpc43xx/memorymap.h.

◆ GPDMA_BASE

| #define GPDMA_BASE (PERIPH_BASE_AHB + 0x02000) |

Definition at line 40 of file lpc43xx/memorymap.h.

◆ GPIO_GROUP0_INTERRUPT_BASE

| #define GPIO_GROUP0_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x08000) |

Definition at line 80 of file lpc43xx/memorymap.h.

◆ GPIO_GROUP1_INTERRUPT_BASE

| #define GPIO_GROUP1_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x09000) |

Definition at line 81 of file lpc43xx/memorymap.h.

◆ GPIO_PIN_INTERRUPT_BASE

| #define GPIO_PIN_INTERRUPT_BASE (PERIPH_BASE_APB0 + 0x07000) |

Definition at line 79 of file lpc43xx/memorymap.h.

◆ GPIO_PORT_BASE

| #define GPIO_PORT_BASE (0x400F4000U) |

Definition at line 123 of file lpc43xx/memorymap.h.

◆ I2C0_BASE

| #define I2C0_BASE (PERIPH_BASE_APB1 + 0x01000) |

Definition at line 88 of file lpc43xx/memorymap.h.

◆ I2C1_BASE

| #define I2C1_BASE (PERIPH_BASE_APB3 + 0x00000) |

Definition at line 110 of file lpc43xx/memorymap.h.

◆ I2S0_BASE

| #define I2S0_BASE (PERIPH_BASE_APB1 + 0x02000) |

Definition at line 89 of file lpc43xx/memorymap.h.

◆ I2S1_BASE

| #define I2S1_BASE (PERIPH_BASE_APB1 + 0x03000) |

Definition at line 90 of file lpc43xx/memorymap.h.

◆ LCD_BASE

| #define LCD_BASE (PERIPH_BASE_AHB + 0x08000) |

Definition at line 46 of file lpc43xx/memorymap.h.

◆ MCPWM_BASE

| #define MCPWM_BASE (PERIPH_BASE_APB1 + 0x00000) |

Definition at line 87 of file lpc43xx/memorymap.h.

◆ OTP_BASE

| #define OTP_BASE (0x40045000U) |

Definition at line 58 of file lpc43xx/memorymap.h.

◆ PERIPH_BASE_AHB

| #define PERIPH_BASE_AHB (0x40000000U) |

Definition at line 29 of file lpc43xx/memorymap.h.

◆ PERIPH_BASE_APB0

| #define PERIPH_BASE_APB0 (0x40080000U) |

Definition at line 30 of file lpc43xx/memorymap.h.

◆ PERIPH_BASE_APB1

| #define PERIPH_BASE_APB1 (0x400A0000U) |

Definition at line 31 of file lpc43xx/memorymap.h.

◆ PERIPH_BASE_APB2

| #define PERIPH_BASE_APB2 (0x400C0000U) |

Definition at line 32 of file lpc43xx/memorymap.h.

◆ PERIPH_BASE_APB3

| #define PERIPH_BASE_APB3 (0x400E0000U) |

Definition at line 33 of file lpc43xx/memorymap.h.

◆ PMC_BASE

| #define PMC_BASE (0x40042000U) |

Definition at line 55 of file lpc43xx/memorymap.h.

◆ QEI_BASE

| #define QEI_BASE (PERIPH_BASE_APB2 + 0x06000) |

Definition at line 103 of file lpc43xx/memorymap.h.

◆ RGU_BASE

| #define RGU_BASE (0x40053000U) |

Definition at line 66 of file lpc43xx/memorymap.h.

◆ RITIMER_BASE

| #define RITIMER_BASE (PERIPH_BASE_APB2 + 0x00000) |

Definition at line 97 of file lpc43xx/memorymap.h.

◆ RTC_BASE

| #define RTC_BASE (0x40046000U) |

Definition at line 59 of file lpc43xx/memorymap.h.

◆ SCT_BASE

| #define SCT_BASE (PERIPH_BASE_AHB + 0x00000) |

Definition at line 38 of file lpc43xx/memorymap.h.

◆ SCU_BASE

| #define SCU_BASE (PERIPH_BASE_APB0 + 0x06000) |

Definition at line 78 of file lpc43xx/memorymap.h.

◆ SDIO_BASE

| #define SDIO_BASE (PERIPH_BASE_AHB + 0x04000) |

Definition at line 42 of file lpc43xx/memorymap.h.

◆ SGPIO_PORT_BASE

| #define SGPIO_PORT_BASE (0x40101000U) |

Definition at line 128 of file lpc43xx/memorymap.h.

◆ SPI_PORT_BASE

| #define SPI_PORT_BASE (0x40100000U) |

Definition at line 127 of file lpc43xx/memorymap.h.

◆ SPIFI_BASE

| #define SPIFI_BASE (PERIPH_BASE_AHB + 0x03000) |

Definition at line 41 of file lpc43xx/memorymap.h.

◆ SSP0_BASE

| #define SSP0_BASE (PERIPH_BASE_APB0 + 0x03000) |

Definition at line 75 of file lpc43xx/memorymap.h.

◆ SSP1_BASE

| #define SSP1_BASE (PERIPH_BASE_APB2 + 0x05000) |

Definition at line 102 of file lpc43xx/memorymap.h.

◆ TIMER0_BASE

| #define TIMER0_BASE (PERIPH_BASE_APB0 + 0x04000) |

Definition at line 76 of file lpc43xx/memorymap.h.

◆ TIMER1_BASE

| #define TIMER1_BASE (PERIPH_BASE_APB0 + 0x05000) |

Definition at line 77 of file lpc43xx/memorymap.h.

◆ TIMER2_BASE

| #define TIMER2_BASE (PERIPH_BASE_APB2 + 0x03000) |

Definition at line 100 of file lpc43xx/memorymap.h.

◆ TIMER3_BASE

| #define TIMER3_BASE (PERIPH_BASE_APB2 + 0x04000) |

Definition at line 101 of file lpc43xx/memorymap.h.

◆ UART1_BASE

| #define UART1_BASE (PERIPH_BASE_APB0 + 0x02000) |

Definition at line 74 of file lpc43xx/memorymap.h.

◆ USART0_BASE

| #define USART0_BASE (PERIPH_BASE_APB0 + 0x01000) |

Definition at line 73 of file lpc43xx/memorymap.h.

◆ USART2_BASE

| #define USART2_BASE (PERIPH_BASE_APB2 + 0x01000) |

Definition at line 98 of file lpc43xx/memorymap.h.

◆ USART3_BASE

| #define USART3_BASE (PERIPH_BASE_APB2 + 0x02000) |

Definition at line 99 of file lpc43xx/memorymap.h.

◆ USB0_BASE

| #define USB0_BASE (PERIPH_BASE_AHB + 0x06000) |

Definition at line 44 of file lpc43xx/memorymap.h.

◆ USB1_BASE

| #define USB1_BASE (PERIPH_BASE_AHB + 0x07000) |

Definition at line 45 of file lpc43xx/memorymap.h.

◆ WWDT_BASE

| #define WWDT_BASE (PERIPH_BASE_APB0 + 0x00000) |

Definition at line 72 of file lpc43xx/memorymap.h.