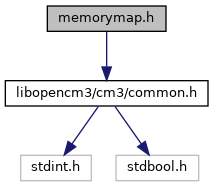

#include <libopencm3/cm3/common.h>

Go to the source code of this file.

Macros | |

| #define | HSMCI_BASE (0x40000000U) |

| #define | SSC_BASE (0x40004000U) |

| #define | SPI0_BASE (0x40008000U) |

| #define | SPI1_BASE (0x4000C000U) |

| #define | TC0_BASE (0x40080000U) |

| #define | TC1_BASE (0x40080040U) |

| #define | TC2_BASE (0x40080080U) |

| #define | TC3_BASE (0x40084000U) |

| #define | TC4_BASE (0x40084040U) |

| #define | TC5_BASE (0x40084080U) |

| #define | TC6_BASE (0x40088000U) |

| #define | TC7_BASE (0x40088040U) |

| #define | TC8_BASE (0x40088080U) |

| #define | TWI0_BASE (0x4008C000U) |

| #define | TWI1_BASE (0x40090000U) |

| #define | PWM_BASE (0x40094000U) |

| #define | USART0_BASE (0x40098000U) |

| #define | USART1_BASE (0x4009C000U) |

| #define | USART2_BASE (0x400A0000U) |

| #define | USART3_BASE (0x400A4000U) |

| #define | UOTGHS_BASE (0x400AC000U) |

| #define | CAN0_BASE (0x400B4000U) |

| #define | CAN1_BASE (0x400B8000U) |

| #define | TRNG_BASE (0x400BC000U) |

| #define | ADC_BASE (0x400C0000U) |

| #define | DMAC_BASE (0x400C4000U) |

| #define | DACC_BASE (0x400C8000U) |

| #define | SMC_BASE (0x400E0000U) |

| #define | SDRAM_BASE (0x400E0200U) |

| #define | MATRIX_BASE (0x400E0400U) |

| #define | PMC_BASE (0x400E0600U) |

| #define | UART_BASE (0x400E0800U) |

| #define | CHIPID_BASE (0x400E0940U) |

| #define | EEFC0_BASE (0x400E0A00U) |

| #define | EEFC1_BASE (0x400E0C00U) |

| #define | PIOA_BASE (0x400E0E00U) |

| #define | PIOB_BASE (0x400E1000U) |

| #define | PIOC_BASE (0x400E1200U) |

| #define | PIOD_BASE (0x400E1400U) |

| #define | PIOE_BASE (0x400E1600U) |

| #define | PIOF_BASE (0x400E1800U) |

| #define | RSTC_BASE (0x400E1A00U) |

| #define | SUPC_BASE (0x400E1A10U) |

| #define | RTT_BASE (0x400E1A30U) |

| #define | WDT_BASE (0x400E1A50U) |

| #define | RTC_BASE (0x400E1A60U) |

| #define | GPBR_BASE (0x400E1A90U) |

Macro Definition Documentation

◆ ADC_BASE

| #define ADC_BASE (0x400C0000U) |

Definition at line 51 of file sam/3a/memorymap.h.

◆ CAN0_BASE

| #define CAN0_BASE (0x400B4000U) |

Definition at line 48 of file sam/3a/memorymap.h.

◆ CAN1_BASE

| #define CAN1_BASE (0x400B8000U) |

Definition at line 49 of file sam/3a/memorymap.h.

◆ CHIPID_BASE

| #define CHIPID_BASE (0x400E0940U) |

Definition at line 61 of file sam/3a/memorymap.h.

◆ DACC_BASE

| #define DACC_BASE (0x400C8000U) |

Definition at line 53 of file sam/3a/memorymap.h.

◆ DMAC_BASE

| #define DMAC_BASE (0x400C4000U) |

Definition at line 52 of file sam/3a/memorymap.h.

◆ EEFC0_BASE

| #define EEFC0_BASE (0x400E0A00U) |

Definition at line 62 of file sam/3a/memorymap.h.

◆ EEFC1_BASE

| #define EEFC1_BASE (0x400E0C00U) |

Definition at line 63 of file sam/3a/memorymap.h.

◆ GPBR_BASE

| #define GPBR_BASE (0x400E1A90U) |

Definition at line 75 of file sam/3a/memorymap.h.

◆ HSMCI_BASE

| #define HSMCI_BASE (0x40000000U) |

Definition at line 27 of file sam/3a/memorymap.h.

◆ MATRIX_BASE

| #define MATRIX_BASE (0x400E0400U) |

Definition at line 58 of file sam/3a/memorymap.h.

◆ PIOA_BASE

| #define PIOA_BASE (0x400E0E00U) |

Definition at line 64 of file sam/3a/memorymap.h.

◆ PIOB_BASE

| #define PIOB_BASE (0x400E1000U) |

Definition at line 65 of file sam/3a/memorymap.h.

◆ PIOC_BASE

| #define PIOC_BASE (0x400E1200U) |

Definition at line 66 of file sam/3a/memorymap.h.

◆ PIOD_BASE

| #define PIOD_BASE (0x400E1400U) |

Definition at line 67 of file sam/3a/memorymap.h.

◆ PIOE_BASE

| #define PIOE_BASE (0x400E1600U) |

Definition at line 68 of file sam/3a/memorymap.h.

◆ PIOF_BASE

| #define PIOF_BASE (0x400E1800U) |

Definition at line 69 of file sam/3a/memorymap.h.

◆ PMC_BASE

| #define PMC_BASE (0x400E0600U) |

Definition at line 59 of file sam/3a/memorymap.h.

◆ PWM_BASE

| #define PWM_BASE (0x40094000U) |

Definition at line 42 of file sam/3a/memorymap.h.

◆ RSTC_BASE

| #define RSTC_BASE (0x400E1A00U) |

Definition at line 70 of file sam/3a/memorymap.h.

◆ RTC_BASE

| #define RTC_BASE (0x400E1A60U) |

Definition at line 74 of file sam/3a/memorymap.h.

◆ RTT_BASE

| #define RTT_BASE (0x400E1A30U) |

Definition at line 72 of file sam/3a/memorymap.h.

◆ SDRAM_BASE

| #define SDRAM_BASE (0x400E0200U) |

Definition at line 57 of file sam/3a/memorymap.h.

◆ SMC_BASE

| #define SMC_BASE (0x400E0000U) |

Definition at line 56 of file sam/3a/memorymap.h.

◆ SPI0_BASE

| #define SPI0_BASE (0x40008000U) |

Definition at line 29 of file sam/3a/memorymap.h.

◆ SPI1_BASE

| #define SPI1_BASE (0x4000C000U) |

Definition at line 30 of file sam/3a/memorymap.h.

◆ SSC_BASE

| #define SSC_BASE (0x40004000U) |

Definition at line 28 of file sam/3a/memorymap.h.

◆ SUPC_BASE

| #define SUPC_BASE (0x400E1A10U) |

Definition at line 71 of file sam/3a/memorymap.h.

◆ TC0_BASE

| #define TC0_BASE (0x40080000U) |

Definition at line 31 of file sam/3a/memorymap.h.

◆ TC1_BASE

| #define TC1_BASE (0x40080040U) |

Definition at line 32 of file sam/3a/memorymap.h.

◆ TC2_BASE

| #define TC2_BASE (0x40080080U) |

Definition at line 33 of file sam/3a/memorymap.h.

◆ TC3_BASE

| #define TC3_BASE (0x40084000U) |

Definition at line 34 of file sam/3a/memorymap.h.

◆ TC4_BASE

| #define TC4_BASE (0x40084040U) |

Definition at line 35 of file sam/3a/memorymap.h.

◆ TC5_BASE

| #define TC5_BASE (0x40084080U) |

Definition at line 36 of file sam/3a/memorymap.h.

◆ TC6_BASE

| #define TC6_BASE (0x40088000U) |

Definition at line 37 of file sam/3a/memorymap.h.

◆ TC7_BASE

| #define TC7_BASE (0x40088040U) |

Definition at line 38 of file sam/3a/memorymap.h.

◆ TC8_BASE

| #define TC8_BASE (0x40088080U) |

Definition at line 39 of file sam/3a/memorymap.h.

◆ TRNG_BASE

| #define TRNG_BASE (0x400BC000U) |

Definition at line 50 of file sam/3a/memorymap.h.

◆ TWI0_BASE

| #define TWI0_BASE (0x4008C000U) |

Definition at line 40 of file sam/3a/memorymap.h.

◆ TWI1_BASE

| #define TWI1_BASE (0x40090000U) |

Definition at line 41 of file sam/3a/memorymap.h.

◆ UART_BASE

| #define UART_BASE (0x400E0800U) |

Definition at line 60 of file sam/3a/memorymap.h.

◆ UOTGHS_BASE

| #define UOTGHS_BASE (0x400AC000U) |

Definition at line 47 of file sam/3a/memorymap.h.

◆ USART0_BASE

| #define USART0_BASE (0x40098000U) |

Definition at line 43 of file sam/3a/memorymap.h.

◆ USART1_BASE

| #define USART1_BASE (0x4009C000U) |

Definition at line 44 of file sam/3a/memorymap.h.

◆ USART2_BASE

| #define USART2_BASE (0x400A0000U) |

Definition at line 45 of file sam/3a/memorymap.h.

◆ USART3_BASE

| #define USART3_BASE (0x400A4000U) |

Definition at line 46 of file sam/3a/memorymap.h.

◆ WDT_BASE

| #define WDT_BASE (0x400E1A50U) |

Definition at line 73 of file sam/3a/memorymap.h.