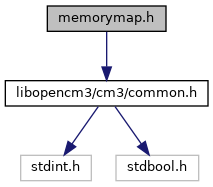

#include <libopencm3/cm3/common.h>

Go to the source code of this file.

Macros | |

| #define | SPI_BASE (0x40008000U) |

| #define | TC0_BASE (0x40010000U) |

| #define | TC1_BASE (0x40010040U) |

| #define | TC2_BASE (0x40010080U) |

| #define | TC3_BASE (0x40014000U) |

| #define | TC4_BASE (0x40014040U) |

| #define | TC5_BASE (0x40014080U) |

| #define | TWI0_BASE (0x40018000U) |

| #define | TWI1_BASE (0x4001C000U) |

| #define | PWM_BASE (0x40020000U) |

| #define | USART0_BASE (0x40024000U) |

| #define | USART1_BASE (0x40028000U) |

| #define | ADC_BASE (0x40038000U) |

| #define | DACC_BASE (0x4003C000U) |

| #define | SMC_BASE (0x400E0000U) |

| #define | MATRIX_BASE (0x400E0200U) |

| #define | PMC_BASE (0x400E0400U) |

| #define | UART0_BASE (0x400E0600U) |

| #define | CHIPID_BASE (0x400E0740U) |

| #define | UART1_BASE (0x400E0800U) |

| #define | EEFC_BASE (0x400E0A00U) |

| #define | PIOA_BASE (0x400E0E00U) |

| #define | PIOB_BASE (0x400E1000U) |

| #define | PIOC_BASE (0x400E1200U) |

| #define | RSTC_BASE (0x400E1400U) |

| #define | SUPC_BASE (0x400E1410U) |

| #define | RTT_BASE (0x400E1430U) |

| #define | WDT_BASE (0x400E1450U) |

| #define | RTC_BASE (0x400E1460U) |

| #define | GPBR_BASE (0x400E1490U) |

Macro Definition Documentation

◆ ADC_BASE

| #define ADC_BASE (0x40038000U) |

Definition at line 39 of file sam/3n/memorymap.h.

◆ CHIPID_BASE

| #define CHIPID_BASE (0x400E0740U) |

Definition at line 47 of file sam/3n/memorymap.h.

◆ DACC_BASE

| #define DACC_BASE (0x4003C000U) |

Definition at line 40 of file sam/3n/memorymap.h.

◆ EEFC_BASE

| #define EEFC_BASE (0x400E0A00U) |

Definition at line 49 of file sam/3n/memorymap.h.

◆ GPBR_BASE

| #define GPBR_BASE (0x400E1490U) |

Definition at line 58 of file sam/3n/memorymap.h.

◆ MATRIX_BASE

| #define MATRIX_BASE (0x400E0200U) |

Definition at line 44 of file sam/3n/memorymap.h.

◆ PIOA_BASE

| #define PIOA_BASE (0x400E0E00U) |

Definition at line 50 of file sam/3n/memorymap.h.

◆ PIOB_BASE

| #define PIOB_BASE (0x400E1000U) |

Definition at line 51 of file sam/3n/memorymap.h.

◆ PIOC_BASE

| #define PIOC_BASE (0x400E1200U) |

Definition at line 52 of file sam/3n/memorymap.h.

◆ PMC_BASE

| #define PMC_BASE (0x400E0400U) |

Definition at line 45 of file sam/3n/memorymap.h.

◆ PWM_BASE

| #define PWM_BASE (0x40020000U) |

Definition at line 36 of file sam/3n/memorymap.h.

◆ RSTC_BASE

| #define RSTC_BASE (0x400E1400U) |

Definition at line 53 of file sam/3n/memorymap.h.

◆ RTC_BASE

| #define RTC_BASE (0x400E1460U) |

Definition at line 57 of file sam/3n/memorymap.h.

◆ RTT_BASE

| #define RTT_BASE (0x400E1430U) |

Definition at line 55 of file sam/3n/memorymap.h.

◆ SMC_BASE

| #define SMC_BASE (0x400E0000U) |

Definition at line 43 of file sam/3n/memorymap.h.

◆ SPI_BASE

| #define SPI_BASE (0x40008000U) |

Definition at line 27 of file sam/3n/memorymap.h.

◆ SUPC_BASE

| #define SUPC_BASE (0x400E1410U) |

Definition at line 54 of file sam/3n/memorymap.h.

◆ TC0_BASE

| #define TC0_BASE (0x40010000U) |

Definition at line 28 of file sam/3n/memorymap.h.

◆ TC1_BASE

| #define TC1_BASE (0x40010040U) |

Definition at line 29 of file sam/3n/memorymap.h.

◆ TC2_BASE

| #define TC2_BASE (0x40010080U) |

Definition at line 30 of file sam/3n/memorymap.h.

◆ TC3_BASE

| #define TC3_BASE (0x40014000U) |

Definition at line 31 of file sam/3n/memorymap.h.

◆ TC4_BASE

| #define TC4_BASE (0x40014040U) |

Definition at line 32 of file sam/3n/memorymap.h.

◆ TC5_BASE

| #define TC5_BASE (0x40014080U) |

Definition at line 33 of file sam/3n/memorymap.h.

◆ TWI0_BASE

| #define TWI0_BASE (0x40018000U) |

Definition at line 34 of file sam/3n/memorymap.h.

◆ TWI1_BASE

| #define TWI1_BASE (0x4001C000U) |

Definition at line 35 of file sam/3n/memorymap.h.

◆ UART0_BASE

| #define UART0_BASE (0x400E0600U) |

Definition at line 46 of file sam/3n/memorymap.h.

◆ UART1_BASE

| #define UART1_BASE (0x400E0800U) |

Definition at line 48 of file sam/3n/memorymap.h.

◆ USART0_BASE

| #define USART0_BASE (0x40024000U) |

Definition at line 37 of file sam/3n/memorymap.h.

◆ USART1_BASE

| #define USART1_BASE (0x40028000U) |

Definition at line 38 of file sam/3n/memorymap.h.

◆ WDT_BASE

| #define WDT_BASE (0x400E1450U) |

Definition at line 56 of file sam/3n/memorymap.h.