port.h File Reference

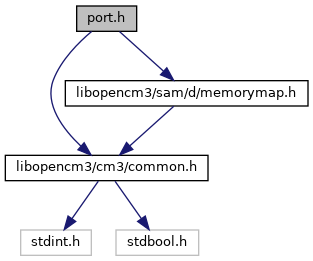

Include dependency graph for port.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | PORTA (PORT_BASE + 0) |

| #define | PORTB (PORT_BASE + 0x80) |

| #define | GPIO0 (1 << 0) |

| #define | GPIO1 (1 << 1) |

| #define | GPIO2 (1 << 2) |

| #define | GPIO3 (1 << 3) |

| #define | GPIO4 (1 << 4) |

| #define | GPIO5 (1 << 5) |

| #define | GPIO6 (1 << 6) |

| #define | GPIO7 (1 << 7) |

| #define | GPIO8 (1 << 8) |

| #define | GPIO9 (1 << 9) |

| #define | GPIO10 (1 << 10) |

| #define | GPIO11 (1 << 11) |

| #define | GPIO12 (1 << 12) |

| #define | GPIO13 (1 << 13) |

| #define | GPIO14 (1 << 14) |

| #define | GPIO15 (1 << 15) |

| #define | GPIO16 (1 << 16) |

| #define | GPIO17 (1 << 17) |

| #define | GPIO18 (1 << 18) |

| #define | GPIO19 (1 << 19) |

| #define | GPIO20 (1 << 20) |

| #define | GPIO21 (1 << 21) |

| #define | GPIO22 (1 << 22) |

| #define | GPIO23 (1 << 23) |

| #define | GPIO24 (1 << 24) |

| #define | GPIO25 (1 << 25) |

| #define | GPIO26 (1 << 26) |

| #define | GPIO27 (1 << 27) |

| #define | GPIO28 (1 << 28) |

| #define | GPIO29 (1 << 29) |

| #define | GPIO30 (1 << 30) |

| #define | GPIO31 (1 << 31) |

| #define | GPIO_ALL 0xffff |

| #define | PORT_DIR(port) MMIO32((port) + 0x0000) |

| Direction register. More... | |

| #define | PORT_DIRCLR(port) MMIO32((port) + 0x0004) |

| Direction clear register. More... | |

| #define | PORT_DIRSET(port) MMIO32((port) + 0x0008) |

| Direction set register. More... | |

| #define | PORT_DIRTGL(port) MMIO32((port) + 0x000c) |

| Direction toggle register. More... | |

| #define | PORT_OUT(port) MMIO32((port) + 0x0010) |

| output register More... | |

| #define | PORT_OUTCLR(port) MMIO32((port) + 0x0014) |

| output clear register More... | |

| #define | PORT_OUTSET(port) MMIO32((port) + 0x0018) |

| output set register More... | |

| #define | PORT_OUTTGL(port) MMIO32((port) + 0x001c) |

| output toggle register More... | |

| #define | PORT_IN(port) MMIO32((port) + 0x0020) |

| input register More... | |

| #define | PORT_CTRL(port) MMIO32((port) + 0x0024) |

| Control register. More... | |

| #define | PORT_WRCONFIG(port) MMIO32((port) + 0x0028) |

| Write configuration register. More... | |

| #define | PORT_PMUX(port, n) MMIO8((port) + 0x0030 + (n)) |

| Peripheral multiplexing registers. More... | |

| #define | PORT_PINCFG(port, n) MMIO8((port) + 0x0040 + (n)) |

| Pin configuration registers. More... | |

| #define | PORT_WRCONFIG_HWSEL (1 << 31) |

| HWSEL: Half word select: 0 [15:0], 1 [31:16]. More... | |

| #define | PORT_WRCONFIG_WRPINCFG (1 << 30) |

| WRPINCFG: Write PINCFG: 1 to update pins for selected by PINMASK. More... | |

| #define | PORT_WRCONFIG_WRPMUX (1 << 28) |

| WRPMUX: Write PMUX: 1 to update pins pmux for selected by PINMASK. More... | |

| #define | PORT_WRCONFIG_PMUX(mux) ((0xf & (mux)) << 24) |

| PMUX: Peripheral Multiplexing: determine pmux for pins selected by PINMASK. More... | |

| #define | PORT_WRCONFIG_DRVSTR (1 << 22) |

| DRVSTR: Output Driver Strength Selection: determine strength for pins in PINMASK. More... | |

| #define | PORT_WRCONFIG_PULLEN (1 << 18) |

| PULLEN: Pull Enable: enable PINCFGy.PULLEN for pins in PINMASK. More... | |

| #define | PORT_WRCONFIG_INEN (1 << 17) |

| INEN: Input Enable: enable PINCFGy.INEN for pins in PINMASK. More... | |

| #define | PORT_WRCONFIG_PMUXEN (1 << 16) |

| PMUXEN: Peripheral Multiplexer Enable: enable PINCFGy.PMUXEN for pins in PINMASK. More... | |

| #define | PORT_WRCONFIG_PINMASK(pins) ((0xffff & (pins)) << 0) |

| PINMASK: Pin Mask for Multiple Pin Configuration: select pins to be configured [31:16] if HWSET=1, [15:0] if HWSET=0. More... | |

| #define | PORT_PMUX_PMUXO(mux) ((0xf & (mux)) << 4) |

| PMUXO: Peripheral Multiplexing for Odd-Numbered Pin: 2*x+1 pin multiplexing. More... | |

| #define | PORT_PMUX_PMUXE(mux) ((0xf & (mux)) << 0) |

| PMUXE: Peripheral Multiplexing for Even-Numbered Pin: 2*x pin multiplexing. More... | |

| #define | PORT_PINCFG_DRVSTR (1 << 6) |

| DRVSTR: Output Driver Strength Selection. More... | |

| #define | PORT_PINCFG_PULLEN (1 << 2) |

| PULLEN: Pull Enable. More... | |

| #define | PORT_PINCFG_INEN (1 << 1) |

| INEN: Input Enable. More... | |

| #define | PORT_PINCFG_PMUXEN (1 << 0) |

| PMUXEN: Peripheral Multiplexer Enable. More... | |

| #define | GPIO_MODE_INPUT 0x00 |

| #define | GPIO_MODE_OUTPUT 0x01 |

| #define | GPIO_MODE_INOUT 0x02 |

| #define | GPIO_CNF_FLOAT 0x00 |

| #define | GPIO_CNF_PULLDOWN 0x01 |

| #define | GPIO_CNF_PULLUP 0x02 |

| #define | GPIO_CNF_AF 0x03 |

Enumerations | |

| enum | port_mux { PORT_PMUX_FUN_A = 0 , PORT_PMUX_FUN_B , PORT_PMUX_FUN_C , PORT_PMUX_FUN_D , PORT_PMUX_FUN_E , PORT_PMUX_FUN_F , PORT_PMUX_FUN_G , PORT_PMUX_FUN_H , PORT_PMUX_FUN_I } |

Functions | |

| void | gpio_mode_setup (uint32_t gpioport, uint8_t mode, uint8_t cnf, uint32_t gpios) |

| Initialize GPIO pins. More... | |

| void | gpio_set_af (uint32_t gpioport, uint8_t af, uint32_t gpios) |

| Alternate function GPIO pins. More... | |

| void | gpio_set (uint32_t gpioport, uint32_t gpios) |

| Set a group of Pins. More... | |

| void | gpio_clear (uint32_t gpioport, uint32_t gpios) |

| Clear a group of Pins. More... | |

| uint32_t | gpio_get (uint32_t gpioport, uint32_t gpios) |

| Read level of a group of Pins. More... | |

| void | gpio_toggle (uint32_t gpioport, uint32_t gpios) |

| Toggle level of a group of Pins. More... | |

| uint32_t | port_read (uint32_t port) |

| Read level for all pins from a port. More... | |

| void | port_write (uint32_t port, uint32_t data) |

| Set level for all pins from a port. More... | |