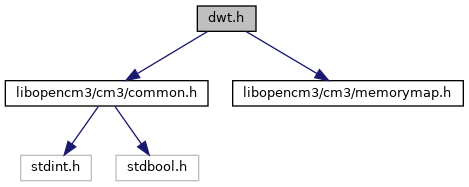

Include dependency graph for dwt.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| bool | dwt_enable_cycle_counter (void) |

| DebugTrace Enable the CPU cycle counter. More... | |

| uint32_t | dwt_read_cycle_counter (void) |

| DebugTrace Read the CPU cycle counter. More... | |