rtc_common_l1f024.h File Reference

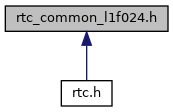

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | RTC_TR MMIO32(RTC_BASE + 0x00) |

| RTC time register (RTC_TR) More... | |

| #define | RTC_DR MMIO32(RTC_BASE + 0x04) |

| RTC date register (RTC_DR) More... | |

| #define | RTC_CR MMIO32(RTC_BASE + 0x08) |

| RTC control register (RTC_CR) More... | |

| #define | RTC_ISR MMIO32(RTC_BASE + 0x0c) |

| RTC initialization and status register (RTC_ISR) More... | |

| #define | RTC_PRER MMIO32(RTC_BASE + 0x10) |

| RTC prescaler register (RTC_PRER) More... | |

| #define | RTC_WUTR MMIO32(RTC_BASE + 0x14) |

| RTC wakeup timer register (RTC_WUTR) More... | |

| #define | RTC_CALIBR MMIO32(RTC_BASE + 0x18) |

| RTC calibration register (RTC_CALIBR) NB: see also RTC_CALR. More... | |

| #define | RTC_ALRMAR MMIO32(RTC_BASE + 0x1c) |

| RTC alarm X register (RTC_ALRMxR) More... | |

| #define | RTC_ALRMBR MMIO32(RTC_BASE + 0x20) |

| #define | RTC_WPR MMIO32(RTC_BASE + 0x24) |

| RTC write protection register (RTC_WPR) More... | |

| #define | RTC_SSR MMIO32(RTC_BASE + 0x28) |

| RTC sub second register (RTC_SSR) (high and med+ only) More... | |

| #define | RTC_SHIFTR MMIO32(RTC_BASE + 0x2c) |

| RTC shift control register (RTC_SHIFTR) (high and med+ only) More... | |

| #define | RTC_TSTR MMIO32(RTC_BASE + 0x30) |

| RTC time stamp time register (RTC_TSTR) More... | |

| #define | RTC_TSDR MMIO32(RTC_BASE + 0x34) |

| RTC time stamp date register (RTC_TSDR) More... | |

| #define | RTC_TSSSR MMIO32(RTC_BASE + 0x38) |

| RTC timestamp sub second register (RTC_TSSSR) (high and med+ only) More... | |

| #define | RTC_CALR MMIO32(RTC_BASE + 0x3c) |

| RTC calibration register (RTC_CALR) (high and med+ only) More... | |

| #define | RTC_TAFCR MMIO32(RTC_BASE + 0x40) |

| RTC tamper and alternate function configuration register (RTC_TAFCR) More... | |

| #define | RTC_ALRMASSR MMIO32(RTC_BASE + 0x44) |

| RTC alarm X sub second register (RTC_ALRMxSSR) (high and med+ only) More... | |

| #define | RTC_ALRMBSSR MMIO32(RTC_BASE + 0x48) |

| #define | RTC_BKP_BASE (RTC_BASE + 0x50) |

| #define | RTC_BKPXR(reg) MMIO32(RTC_BKP_BASE + (4 * (reg))) |

| RTC backup registers (RTC_BKPxR) More... | |

| #define | RTC_TR_PM (1 << 22) |

| AM/PM notation. More... | |

| #define | RTC_TR_HT_SHIFT (20) |

| Hour tens in BCD format shift. More... | |

| #define | RTC_TR_HT_MASK (0x3) |

| Hour tens in BCD format mask. More... | |

| #define | RTC_TR_HU_SHIFT (16) |

| Hour units in BCD format shift. More... | |

| #define | RTC_TR_HU_MASK (0xf) |

| Hour units in BCD format mask. More... | |

| #define | RTC_TR_MNT_SHIFT (12) |

| Minute tens in BCD format shift. More... | |

| #define | RTC_TR_MNT_MASK (0x7) |

| Minute tens in BCD format mask. More... | |

| #define | RTC_TR_MNU_SHIFT (8) |

| Minute units in BCD format shift. More... | |

| #define | RTC_TR_MNU_MASK (0xf) |

| Minute units in BCD format mask. More... | |

| #define | RTC_TR_ST_SHIFT (4) |

| Second tens in BCD format shift. More... | |

| #define | RTC_TR_ST_MASK (0x7) |

| Second tens in BCD format mask. More... | |

| #define | RTC_TR_SU_SHIFT (0) |

| Second units in BCD format shift. More... | |

| #define | RTC_TR_SU_MASK (0xf) |

| Second units in BCD format mask. More... | |

| #define | RTC_DR_YT_SHIFT (20) |

| Year tens in BCD format shift. More... | |

| #define | RTC_DR_YT_MASK (0xf) |

| Year tens in BCD format mask. More... | |

| #define | RTC_DR_YU_SHIFT (16) |

| Year units in BCD format shift. More... | |

| #define | RTC_DR_YU_MASK (0xf) |

| Year units in BCD format mask. More... | |

| #define | RTC_DR_WDU_SHIFT (13) |

| Weekday units shift. More... | |

| #define | RTC_DR_WDU_MASK (0x7) |

| Weekday units mask. More... | |

| #define | RTC_DR_MT_SHIFT (12) |

| Month tens in BCD format shift. More... | |

| #define | RTC_DR_MT_MASK (1) |

| Month tens in BCD format mask. More... | |

| #define | RTC_DR_MU_SHIFT (8) |

| Month units in BCD format shift. More... | |

| #define | RTC_DR_MU_MASK (0xf) |

| Month units in BCD format mask. More... | |

| #define | RTC_DR_DT_SHIFT (4) |

| Date tens in BCD format shift. More... | |

| #define | RTC_DR_DT_MASK (0x3) |

| Date tens in BCD format mask. More... | |

| #define | RTC_DR_DU_SHIFT (0) |

| Date units in BCD format shift. More... | |

| #define | RTC_DR_DU_MASK (0xf) |

| Date units in BCD format mask. More... | |

| #define | RTC_CR_COE (1<<23) |

| Calibration output enable. More... | |

| #define | RTC_CR_OSEL_SHIFT 21 |

| #define | RTC_CR_OSEL_MASK (0x3) |

| #define | RTC_CR_OSEL_DISABLED (0x0) |

| #define | RTC_CR_OSEL_ALARMA (0x1) |

| #define | RTC_CR_OSEL_ALARMB (0x2) |

| #define | RTC_CR_OSEL_WAKEUP (0x3) |

| #define | RTC_CR_POL (1<<20) |

| Output polarity. More... | |

| #define | RTC_CR_COSEL (1<<19) |

| Calibration output selection. More... | |

| #define | RTC_CR_BKP (1<<18) |

| Backup. More... | |

| #define | RTC_CR_SUB1H (1<<17) |

| Subtract 1 hour (winter time change) More... | |

| #define | RTC_CR_ADD1H (1<<16) |

| Add 1 hour (summer time change) More... | |

| #define | RTC_CR_TSIE (1<<15) |

| Timestamp interrupt enable. More... | |

| #define | RTC_CR_WUTIE (1<<14) |

| Wakeup timer interrupt enable. More... | |

| #define | RTC_CR_ALRBIE (1<<13) |

| Alarm B interrupt enable. More... | |

| #define | RTC_CR_ALRAIE (1<<12) |

| Alarm A interrupt enable. More... | |

| #define | RTC_CR_TSE (1<<11) |

| Time stamp enable. More... | |

| #define | RTC_CR_WUTE (1<<10) |

| Wakeup timer enable. More... | |

| #define | RTC_CR_ALRBE (1<<9) |

| Alarm B enable. More... | |

| #define | RTC_CR_ALRAE (1<<8) |

| Alarm A enable. More... | |

| #define | RTC_CR_DCE (1<<7) |

| Course digital calibration enable. More... | |

| #define | RTC_CR_FMT (1<<6) |

| Hour format. More... | |

| #define | RTC_CR_BYPSHAD (1<<5) |

| Bypass the shadow registers. More... | |

| #define | RTC_CR_REFCKON (1<<4) |

| Reference clock detection enable. More... | |

| #define | RTC_CR_TSEDGE (1<<3) |

| Timestamp event active edge. More... | |

| #define | RTC_CR_WUCLKSEL_SHIFT (0) |

| #define | RTC_CR_WUCLKSEL_MASK (0x7) |

| #define | RTC_CR_WUCLKSEL_RTC_DIV16 (0x0) |

| #define | RTC_CR_WUCLKSEL_RTC_DIV8 (0x1) |

| #define | RTC_CR_WUCLKSEL_RTC_DIV4 (0x2) |

| #define | RTC_CR_WUCLKSEL_RTC_DIV2 (0x3) |

| #define | RTC_CR_WUCLKSEL_SPRE (0x4) |

| #define | RTC_CR_WUCLKSEL_SPRE_216 (0x6) |

| #define | RTC_ISR_RECALPF (1<<16) |

| RECALPF: Recalib pending flag. More... | |

| #define | RTC_ISR_TAMP3F (1<<15) |

| TAMP3F: TAMPER3 detection flag (not on F4) More... | |

| #define | RTC_ISR_TAMP2F (1<<14) |

| TAMP2F: TAMPER2 detection flag. More... | |

| #define | RTC_ISR_TAMP1F (1<<13) |

| TAMP1F: TAMPER detection flag. More... | |

| #define | RTC_ISR_TSOVF (1<<12) |

| TSOVF: Timestamp overflow flag. More... | |

| #define | RTC_ISR_TSF (1<<11) |

| TSF: Timestamp flag. More... | |

| #define | RTC_ISR_WUTF (1<<10) |

| WUTF: Wakeup timer flag. More... | |

| #define | RTC_ISR_ALRBF (1<<9) |

| ALRBF: Alarm B flag. More... | |

| #define | RTC_ISR_ALRAF (1<<8) |

| ALRAF: Alarm A flag. More... | |

| #define | RTC_ISR_INIT (1<<7) |

| INIT: Initialization mode. More... | |

| #define | RTC_ISR_INITF (1<<6) |

| INITF: Initialization flag. More... | |

| #define | RTC_ISR_RSF (1<<5) |

| RSF: Registers sync flag. More... | |

| #define | RTC_ISR_INITS (1<<4) |

| INITS: Init status flag. More... | |

| #define | RTC_ISR_SHPF (1<<3) |

| SHPF: Shift operation pending. More... | |

| #define | RTC_ISR_WUTWF (1<<2) |

| WUTWF: Wakeup timer write flag. More... | |

| #define | RTC_ISR_ALRBWF (1<<1) |

| ALRBWF: Alarm B write flag. More... | |

| #define | RTC_ISR_ALRAWF (1<<0) |

| ALRAWF: Alarm A write flag. More... | |

| #define | RTC_PRER_PREDIV_A_SHIFT (16) |

| Async prescaler factor shift. More... | |

| #define | RTC_PRER_PREDIV_A_MASK (0x7f) |

| Async prescaler factor mask. More... | |

| #define | RTC_PRER_PREDIV_S_SHIFT (0) |

| Sync prescaler factor shift. More... | |

| #define | RTC_PRER_PREDIV_S_MASK (0x7fff) |

| Sync prescaler factor mask. More... | |

| #define | RTC_CALIBR_DCS (1 << 7) |

| #define | RTC_CALIBR_DC_SHIFT (0) |

| #define | RTC_CALIBR_DC_MASK (0x1f) |

| #define | RTC_ALRMXR_MSK4 (1<<31) |

| #define | RTC_ALRMXR_WDSEL (1<<30) |

| #define | RTC_ALRMXR_DT_SHIFT (28) |

| #define | RTC_ALRMXR_DT_MASK (0x3) |

| #define | RTC_ALRMXR_DU_SHIFT (24) |

| #define | RTC_ALRMXR_DU_MASK (0xf) |

| #define | RTC_ALRMXR_MSK3 (1<<23) |

| #define | RTC_ALRMXR_PM (1<<22) |

| #define | RTC_ALRMXR_HT_SHIFT (20) |

| #define | RTC_ALRMXR_HT_MASK (0x3) |

| #define | RTC_ALRMXR_HU_SHIFT (16) |

| #define | RTC_ALRMXR_HU_MASK (0xf) |

| #define | RTC_ALRMXR_MSK2 (1<<15) |

| #define | RTC_ALRMXR_MNT_SHIFT (12) |

| #define | RTC_ALRMXR_MNT_MASK (0x7) |

| #define | RTC_ALRMXR_MNU_SHIFT (8) |

| #define | RTC_ALRMXR_MNU_MASK (0xf) |

| #define | RTC_ALRMXR_MSK1 (1<<7) |

| #define | RTC_ALRMXR_ST_SHIFT (4) |

| #define | RTC_ALRMXR_ST_MASK (0x7) |

| #define | RTC_ALRMXR_SU_SHIFT (0) |

| #define | RTC_ALRMXR_SU_MASK (0xf) |

| #define | RTC_SHIFTR_ADD1S (1<<31) |

| #define | RTC_SHIFTR_SUBFS_SHIFT (0) |

| #define | RTC_SHIFTR_SUBFS_MASK (0x7fff) |

| #define | RTC_TSTR_PM (1<<22) |

| #define | RTC_TSTR_HT_SHIFT (20) |

| #define | RTC_TSTR_HT_MASK (0x3) |

| #define | RTC_TSTR_HU_SHIFT (16) |

| #define | RTC_TSTR_HU_MASK (0xf) |

| #define | RTC_TSTR_MNT_SHIFT (12) |

| #define | RTC_TSTR_MNT_MASK (0x7) |

| #define | RTC_TSTR_MNU_SHIFT (8) |

| #define | RTC_TSTR_MNU_MASK (0xf) |

| #define | RTC_TSTR_ST_SHIFT (4) |

| #define | RTC_TSTR_ST_MASK (0x7) |

| #define | RTC_TSTR_SU_SHIFT (0) |

| #define | RTC_TSTR_SU_MASK (0xf) |

| #define | RTC_TSDR_WDU_SHIFT (13) |

| #define | RTC_TSDR_WDU_MASK (0x7) |

| #define | RTC_TSDR_MT (1<<12) |

| #define | RTC_TSDR_MU_SHIFT (8) |

| #define | RTC_TSDR_MU_MASK (0xf) |

| #define | RTC_TSDR_DT_SHIFT (4) |

| #define | RTC_TSDR_DT_MASK (0x3) |

| #define | RTC_TSDR_DU_SHIFT (0) |

| #define | RTC_TSDR_DU_MASK (0xf) |

| #define | RTC_CALR_CALP (1 << 15) |

| #define | RTC_CALR_CALW8 (1 << 14) |

| #define | RTC_CALR_CALW16 (1 << 13) |

| #define | RTC_CALR_CALM_SHIFT (0) |

| #define | RTC_CALR_CALM_MASK (0x1ff) |

| #define | RTC_TAFCR_ALARMOUTTYPE (1<<18) |

| #define | RTC_TAFCR_TAMPPUDIS (1<<15) |

| #define | RTC_TAFCR_TAMPPRCH_SHIFT (13) |

| #define | RTC_TAFCR_TAMPPRCH_MASK (0x3) |

| #define | RTC_TAFCR_TAMPPRCH_1RTC (0x0) |

| #define | RTC_TAFCR_TAMPPRCH_2RTC (0x1) |

| #define | RTC_TAFCR_TAMPPRCH_4RTC (0x2) |

| #define | RTC_TAFCR_TAMPPRCH_8RTC (0x3) |

| #define | RTC_TAFCR_TAMPFLT_SHIFT (11) |

| #define | RTC_TAFCR_TAMPFLT_MASK (0x3) |

| #define | RTC_TAFCR_TAMPFLT_EDGE1 (0x0) |

| #define | RTC_TAFCR_TAMPFLT_EDGE2 (0x1) |

| #define | RTC_TAFCR_TAMPFLT_EDGE4 (0x2) |

| #define | RTC_TAFCR_TAMPFLT_EDGE8 (0x3) |

| #define | RTC_TAFCR_TAMPFREQ_SHIFT (8) |

| #define | RTC_TAFCR_TAMPFREQ_MASK (0x7) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV32K (0x0) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV16K (0x1) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV8K (0x2) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV4K (0x3) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV2K (0x4) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV1K (0x5) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV512 (0x6) |

| #define | RTC_TAFCR_TAMPFREQ_RTCDIV256 (0x7) |

| #define | RTC_TAFCR_TAMPTS (1<<7) |

| #define | RTC_TAFCR_TAMP3TRG (1<<6) |

| #define | RTC_TAFCR_TAMP3E (1<<5) |

| #define | RTC_TAFCR_TAMP2TRG (1<<4) |

| #define | RTC_TAFCR_TAMP2E (1<<3) |

| #define | RTC_TAFCR_TAMPIE (1<<2) |

| #define | RTC_TAFCR_TAMP1TRG (1<<1) |

| #define | RTC_TAFCR_TAMP1E (1<<0) |

| #define | RTC_ALRMXSSR_MASKSS_SHIFT (24) |

| #define | RTC_ALARXSSR_MASKSS_MASK (0xf) |

| #define | RTC_ALRMXSSR_SS_SHIFT (0) |

| #define | RTC_ALARXSSR_SS_MASK (0x7fff) |

Enumerations | |

| enum | rtc_weekday { RTC_DR_WDU_MON = 0x01 , RTC_DR_WDU_TUE , RTC_DR_WDU_WED , RTC_DR_WDU_THU , RTC_DR_WDU_FRI , RTC_DR_WDU_SAT , RTC_DR_WDU_SUN } |

Functions | |

| void | rtc_set_prescaler (uint32_t sync, uint32_t async) |

| Set RTC prescalars. More... | |

| void | rtc_wait_for_synchro (void) |

| Wait for RTC registers to be synchronised with the APB1 bus. More... | |

| void | rtc_lock (void) |

| Lock write access to the RTC registers. More... | |

| void | rtc_unlock (void) |

| Unlock write access to the RTC registers. More... | |

| void | rtc_set_wakeup_time (uint16_t wkup_time, uint8_t rtc_cr_wucksel) |

| Sets the wakeup time auto-reload value. More... | |

| void | rtc_clear_wakeup_flag (void) |

| Clears the wakeup flag. More... | |

| void | rtc_set_init_flag (void) |

| Sets the initialization flag. More... | |

| void | rtc_clear_init_flag (void) |

| Clears (resets) the initialization flag. More... | |

| bool | rtc_init_flag_is_ready (void) |

| Returns if the RTC_ISR init flag RTC_ISR_INITF is set. More... | |

| void | rtc_wait_for_init_ready (void) |

| Waits infinitely for initialization flag to be set in RTC_ISR. More... | |

| void | rtc_set_bypass_shadow_register (void) |

| void | rtc_enable_bypass_shadow_register (void) |

| Sets the bypass shadow bit in RTC_CR. More... | |

| void | rtc_disable_bypass_shadow_register (void) |

| Clears the bypass shadow bit in RTC_CR. More... | |

| void | rtc_set_am_format (void) |

| Sets the RTC control register hour format to AM (24h) More... | |

| void | rtc_set_pm_format (void) |

| Sets the RTC control register hour format to PM (12h) More... | |

| void | rtc_calendar_set_year (uint8_t year) |

| Sets the RTC BCD calendar year value. More... | |

| void | rtc_calendar_set_weekday (enum rtc_weekday rtc_dr_wdu) |

| Sets the RTC BCD calendar weekday. More... | |

| void | rtc_calendar_set_month (uint8_t month) |

| Sets the RTC BCD calendar month value. More... | |

| void | rtc_calendar_set_day (uint8_t day) |

| Sets the RTC BCD calendar day value. More... | |

| void | rtc_calendar_set_date (uint8_t year, uint8_t month, uint8_t day, enum rtc_weekday rtc_dr_wdu) |

| Sets the RTC BCD calendar value. More... | |

| void | rtc_time_set_hour (uint8_t hour, bool use_am_notation) |

| Sets the RTC BCD time hour value. More... | |

| void | rtc_time_set_minute (uint8_t minute) |

| Sets the RTC BCD time minute value. More... | |

| void | rtc_time_set_second (uint8_t second) |

| Sets the RTC BCD time second value. More... | |

| void | rtc_time_set_time (uint8_t hour, uint8_t minute, uint8_t second, bool use_am_notation) |

| Sets the RTC BCD time. More... | |