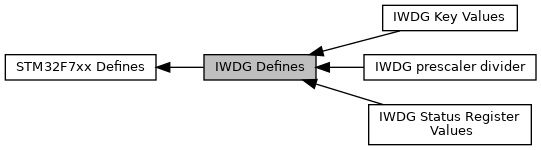

Defined Constants and Types for the STM32F7xx Independent Watchdog Timer More...

Modules | |

| IWDG Key Values | |

| IWDG prescaler divider | |

| IWDG Status Register Values | |

Macros | |

| #define | IWDG_KR MMIO32(IWDG_BASE + 0x00) |

| Key Register (IWDG_KR) More... | |

| #define | IWDG_PR MMIO32(IWDG_BASE + 0x04) |

| Prescaler register (IWDG_PR) More... | |

| #define | IWDG_RLR MMIO32(IWDG_BASE + 0x08) |

| Reload register (IWDG_RLR) More... | |

| #define | IWDG_SR MMIO32(IWDG_BASE + 0x0c) |

| Status register (IWDG_SR) More... | |

| #define | IWDG_PR_LSB 0 |

| #define | IWDG_WINR MMIO32(IWDG_BASE + 0x10) |

| Window Register (IWDG_WINR) More... | |

Functions | |

| void | iwdg_start (void) |

| IWDG Enable Watchdog Timer. More... | |

| void | iwdg_set_period_ms (uint32_t period) |

| IWDG Set Period in Milliseconds. More... | |

| bool | iwdg_reload_busy (void) |

| IWDG Get Reload Register Status. More... | |

| bool | iwdg_prescaler_busy (void) |

| IWDG Get Prescaler Register Status. More... | |

| void | iwdg_reset (void) |

| IWDG reset Watchdog Timer. More... | |

Detailed Description

Defined Constants and Types for the STM32F7xx Independent Watchdog Timer

- Version

- 1.0.0

- Date

- 11 April 2018

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ IWDG_KR

Key Register (IWDG_KR)

Definition at line 40 of file iwdg_common_all.h.

◆ IWDG_PR

Prescaler register (IWDG_PR)

Definition at line 43 of file iwdg_common_all.h.

◆ IWDG_PR_LSB

| #define IWDG_PR_LSB 0 |

Definition at line 70 of file iwdg_common_all.h.

◆ IWDG_RLR

Reload register (IWDG_RLR)

Definition at line 46 of file iwdg_common_all.h.

◆ IWDG_SR

Status register (IWDG_SR)

Definition at line 49 of file iwdg_common_all.h.

◆ IWDG_WINR

Window Register (IWDG_WINR)

Definition at line 48 of file iwdg_common_v2.h.

Function Documentation

◆ iwdg_prescaler_busy()

| bool iwdg_prescaler_busy | ( | void | ) |

IWDG Get Prescaler Register Status.

- Returns

- boolean: TRUE if the prescaler register is busy and unavailable for loading a new period value.

Definition at line 135 of file iwdg_common_all.c.

References IWDG_SR, and IWDG_SR_PVU.

Referenced by iwdg_set_period_ms().

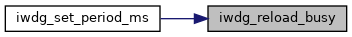

◆ iwdg_reload_busy()

| bool iwdg_reload_busy | ( | void | ) |

IWDG Get Reload Register Status.

- Returns

- boolean: TRUE if the reload register is busy and unavailable for loading a new count value.

Definition at line 123 of file iwdg_common_all.c.

References IWDG_SR, and IWDG_SR_RVU.

Referenced by iwdg_set_period_ms().

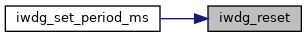

◆ iwdg_reset()

| void iwdg_reset | ( | void | ) |

IWDG reset Watchdog Timer.

The watchdog timer is reset. The counter restarts from the value in the reload register.

Definition at line 147 of file iwdg_common_all.c.

References IWDG_KR, and IWDG_KR_RESET.

Referenced by iwdg_set_period_ms().

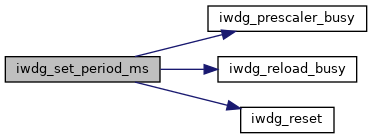

◆ iwdg_set_period_ms()

| void iwdg_set_period_ms | ( | uint32_t | period | ) |

IWDG Set Period in Milliseconds.

The countdown period is converted into count and prescale values. The maximum period is 32.76 seconds; values above this are truncated. Periods less than 1ms are not supported by this library.

A delay of up to 5 clock cycles of the LSI clock (about 156 microseconds) can occasionally occur if the prescale or preload registers are currently busy loading a previous value.

- Parameters

-

[in] period uint32_t Period in milliseconds (< 32760) from a watchdog reset until a system reset is issued.

Definition at line 73 of file iwdg_common_all.c.

References COUNT_LENGTH, COUNT_MASK, IWDG_KR, IWDG_KR_UNLOCK, IWDG_PR, iwdg_prescaler_busy(), iwdg_reload_busy(), iwdg_reset(), and IWDG_RLR.

◆ iwdg_start()

| void iwdg_start | ( | void | ) |

IWDG Enable Watchdog Timer.

The watchdog timer is started. The timeout period defaults to 512 milliseconds unless it has been previously defined.

Definition at line 54 of file iwdg_common_all.c.

References IWDG_KR, and IWDG_KR_START.