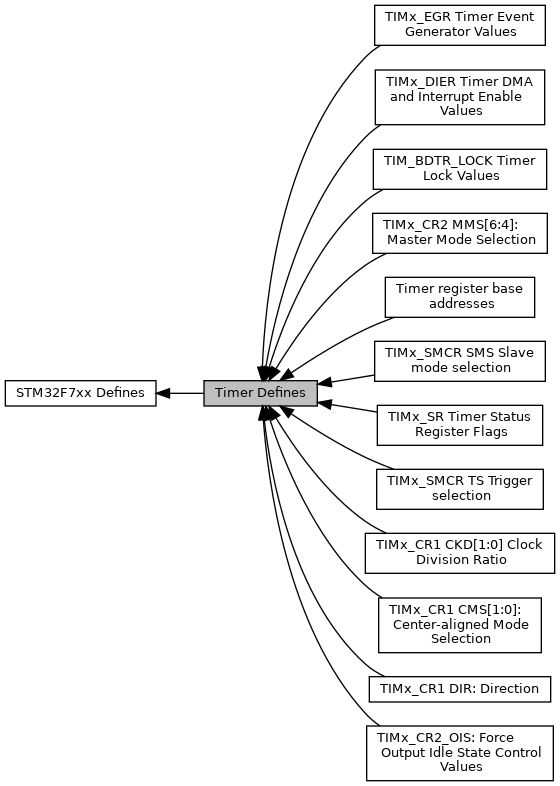

libopencm3 Defined Constants and Types for the STM32F7xx Timers More...

Functions | |

| void | timer_enable_irq (uint32_t timer_peripheral, uint32_t irq) |

| Enable Interrupts for a Timer. More... | |

| void | timer_disable_irq (uint32_t timer_peripheral, uint32_t irq) |

| Disable Interrupts for a Timer. More... | |

| bool | timer_interrupt_source (uint32_t timer_peripheral, uint32_t flag) |

| Return Interrupt Source. More... | |

| bool | timer_get_flag (uint32_t timer_peripheral, uint32_t flag) |

| Read a Status Flag. More... | |

| void | timer_clear_flag (uint32_t timer_peripheral, uint32_t flag) |

| Clear a Status Flag. More... | |

| void | timer_set_mode (uint32_t timer_peripheral, uint32_t clock_div, uint32_t alignment, uint32_t direction) |

| Set the Timer Mode. More... | |

| void | timer_set_clock_division (uint32_t timer_peripheral, uint32_t clock_div) |

| Set Input Filter and Dead-time Clock Divider Ratio. More... | |

| void | timer_enable_preload (uint32_t timer_peripheral) |

| Enable Auto-Reload Buffering. More... | |

| void | timer_disable_preload (uint32_t timer_peripheral) |

| Disable Auto-Reload Buffering. More... | |

| void | timer_set_alignment (uint32_t timer_peripheral, uint32_t alignment) |

| Specify the counter alignment mode. More... | |

| void | timer_direction_up (uint32_t timer_peripheral) |

| Set the Timer to Count Up. More... | |

| void | timer_direction_down (uint32_t timer_peripheral) |

| Set the Timer to Count Down. More... | |

| void | timer_one_shot_mode (uint32_t timer_peripheral) |

| Enable the Timer for One Cycle and Stop. More... | |

| void | timer_continuous_mode (uint32_t timer_peripheral) |

| Enable the Timer to Run Continuously. More... | |

| void | timer_update_on_any (uint32_t timer_peripheral) |

| Set the Timer to Generate Update IRQ or DMA on any Event. More... | |

| void | timer_update_on_overflow (uint32_t timer_peripheral) |

| Set the Timer to Generate Update IRQ or DMA only from Under/Overflow Events. More... | |

| void | timer_enable_update_event (uint32_t timer_peripheral) |

| Enable Timer Update Events. More... | |

| void | timer_disable_update_event (uint32_t timer_peripheral) |

| Disable Timer Update Events. More... | |

| void | timer_enable_counter (uint32_t timer_peripheral) |

| Enable the timer to start counting. More... | |

| void | timer_disable_counter (uint32_t timer_peripheral) |

| Stop the timer from counting. More... | |

| void | timer_set_output_idle_state (uint32_t timer_peripheral, uint32_t outputs) |

| Set Timer Output Idle States High. More... | |

| void | timer_reset_output_idle_state (uint32_t timer_peripheral, uint32_t outputs) |

| Set Timer Output Idle States Low. More... | |

| void | timer_set_ti1_ch123_xor (uint32_t timer_peripheral) |

| Set Timer 1 Input to XOR of Three Channels. More... | |

| void | timer_set_ti1_ch1 (uint32_t timer_peripheral) |

| Set Timer 1 Input to Channel 1. More... | |

| void | timer_set_master_mode (uint32_t timer_peripheral, uint32_t mode) |

| Set the Master Mode. More... | |

| void | timer_set_dma_on_compare_event (uint32_t timer_peripheral) |

| Set Timer DMA Requests on Capture/Compare Events. More... | |

| void | timer_set_dma_on_update_event (uint32_t timer_peripheral) |

| Set Timer DMA Requests on Update Events. More... | |

| void | timer_enable_compare_control_update_on_trigger (uint32_t timer_peripheral) |

| Enable Timer Capture/Compare Control Update with Trigger. More... | |

| void | timer_disable_compare_control_update_on_trigger (uint32_t timer_peripheral) |

| Disable Timer Capture/Compare Control Update with Trigger. More... | |

| void | timer_enable_preload_complementry_enable_bits (uint32_t timer_peripheral) |

| Enable Timer Capture/Compare Control Preload. More... | |

| void | timer_disable_preload_complementry_enable_bits (uint32_t timer_peripheral) |

| Disable Timer Capture/Compare Control Preload. More... | |

| void | timer_set_prescaler (uint32_t timer_peripheral, uint32_t value) |

| Set the Value for the Timer Prescaler. More... | |

| void | timer_set_repetition_counter (uint32_t timer_peripheral, uint32_t value) |

| Set the Value for the Timer Repetition Counter. More... | |

| void | timer_set_period (uint32_t timer_peripheral, uint32_t period) |

| Timer Set Period. More... | |

| void | timer_enable_oc_clear (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Enable the Output Compare Clear Function. More... | |

| void | timer_disable_oc_clear (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Disable the Output Compare Clear Function. More... | |

| void | timer_set_oc_fast_mode (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Enable the Output Compare Fast Mode. More... | |

| void | timer_set_oc_slow_mode (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Enable the Output Compare Slow Mode. More... | |

| void | timer_set_oc_mode (uint32_t timer_peripheral, enum tim_oc_id oc_id, enum tim_oc_mode oc_mode) |

| Timer Set Output Compare Mode. More... | |

| void | timer_enable_oc_preload (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Enable the Output Compare Preload Register. More... | |

| void | timer_disable_oc_preload (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Disable the Output Compare Preload Register. More... | |

| void | timer_set_oc_polarity_high (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Set the Output Polarity High. More... | |

| void | timer_set_oc_polarity_low (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Set the Output Polarity Low. More... | |

| void | timer_enable_oc_output (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Enable the Output Compare. More... | |

| void | timer_disable_oc_output (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Disable the Output Compare. More... | |

| void | timer_set_oc_idle_state_set (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer set Output Compare Idle State High. More... | |

| void | timer_set_oc_idle_state_unset (uint32_t timer_peripheral, enum tim_oc_id oc_id) |

| Timer Set Output Compare Idle State Low. More... | |

| void | timer_set_oc_value (uint32_t timer_peripheral, enum tim_oc_id oc_id, uint32_t value) |

| Timer Set Output Compare Value. More... | |

| void | timer_enable_break_main_output (uint32_t timer_peripheral) |

| Enable Output in Break. More... | |

| void | timer_disable_break_main_output (uint32_t timer_peripheral) |

| Disable Output in Break. More... | |

| void | timer_enable_break_automatic_output (uint32_t timer_peripheral) |

| Enable Automatic Output in Break. More... | |

| void | timer_disable_break_automatic_output (uint32_t timer_peripheral) |

| Disable Automatic Output in Break. More... | |

| void | timer_set_break_polarity_high (uint32_t timer_peripheral) |

| Activate Break when Input High. More... | |

| void | timer_set_break_polarity_low (uint32_t timer_peripheral) |

| Activate Break when Input Low. More... | |

| void | timer_enable_break (uint32_t timer_peripheral) |

| Enable Break. More... | |

| void | timer_disable_break (uint32_t timer_peripheral) |

| Disable Break. More... | |

| void | timer_set_enabled_off_state_in_run_mode (uint32_t timer_peripheral) |

| Enable Off-State in Run Mode. More... | |

| void | timer_set_disabled_off_state_in_run_mode (uint32_t timer_peripheral) |

| Disable Off-State in Run Mode. More... | |

| void | timer_set_enabled_off_state_in_idle_mode (uint32_t timer_peripheral) |

| Enable Off-State in Idle Mode. More... | |

| void | timer_set_disabled_off_state_in_idle_mode (uint32_t timer_peripheral) |

| Disable Off-State in Idle Mode. More... | |

| void | timer_set_break_lock (uint32_t timer_peripheral, uint32_t lock) |

| Set Lock Bits. More... | |

| void | timer_set_deadtime (uint32_t timer_peripheral, uint32_t deadtime) |

| Set Deadtime. More... | |

| void | timer_generate_event (uint32_t timer_peripheral, uint32_t event) |

| Force generate a timer event. More... | |

| uint32_t | timer_get_counter (uint32_t timer_peripheral) |

| Read Counter. More... | |

| void | timer_set_counter (uint32_t timer_peripheral, uint32_t count) |

| Set Counter. More... | |

| void | timer_ic_set_filter (uint32_t timer, enum tim_ic_id ic, enum tim_ic_filter flt) |

| Set Input Capture Filter Parameters. More... | |

| void | timer_ic_set_prescaler (uint32_t timer, enum tim_ic_id ic, enum tim_ic_psc psc) |

| Set Input Capture Prescaler. More... | |

| void | timer_ic_set_input (uint32_t timer, enum tim_ic_id ic, enum tim_ic_input in) |

| Set Capture/Compare Channel Direction/Input. More... | |

| void | timer_ic_enable (uint32_t timer, enum tim_ic_id ic) |

| Enable Timer Input Capture. More... | |

| void | timer_ic_disable (uint32_t timer, enum tim_ic_id ic) |

| Disable Timer Input Capture. More... | |

| void | timer_slave_set_filter (uint32_t timer, enum tim_ic_filter flt) |

| Set External Trigger Filter Parameters for Slave. More... | |

| void | timer_slave_set_prescaler (uint32_t timer, enum tim_ic_psc psc) |

| Set External Trigger Prescaler for Slave. More... | |

| void | timer_slave_set_polarity (uint32_t timer, enum tim_et_pol pol) |

| Set External Trigger Polarity for Slave. More... | |

| void | timer_slave_set_mode (uint32_t timer, uint8_t mode) |

| Set Slave Mode. More... | |

| void | timer_slave_set_trigger (uint32_t timer, uint8_t trigger) |

| Set Slave Trigger Source. More... | |

| void | timer_slave_set_extclockmode2 (uint32_t timer_peripheral, enum tim_ecm2_state state) |

| Set External Clock Mode 2. More... | |

Detailed Description

libopencm3 Defined Constants and Types for the STM32F7xx Timers

- Version

- 1.0.0

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ TIM10_ARR

| #define TIM10_ARR TIM_ARR(TIM10) |

Definition at line 289 of file timer_common_all.h.

◆ TIM10_CCER

| #define TIM10_CCER TIM_CCER(TIM10) |

Definition at line 229 of file timer_common_all.h.

◆ TIM10_CCMR1

| #define TIM10_CCMR1 TIM_CCMR1(TIM10) |

Definition at line 202 of file timer_common_all.h.

◆ TIM10_CCR1

| #define TIM10_CCR1 TIM_CCR1(TIM10) |

Definition at line 315 of file timer_common_all.h.

◆ TIM10_CNT

| #define TIM10_CNT TIM_CNT(TIM10) |

Definition at line 249 of file timer_common_all.h.

◆ TIM10_CR1

| #define TIM10_CR1 TIM_CR1(TIM10) |

Definition at line 98 of file timer_common_all.h.

◆ TIM10_DIER

| #define TIM10_DIER TIM_DIER(TIM10) |

Definition at line 144 of file timer_common_all.h.

◆ TIM10_EGR

| #define TIM10_EGR TIM_EGR(TIM10) |

Definition at line 184 of file timer_common_all.h.

◆ TIM10_PSC

| #define TIM10_PSC TIM_PSC(TIM10) |

Definition at line 269 of file timer_common_all.h.

◆ TIM10_SR

| #define TIM10_SR TIM_SR(TIM10) |

Definition at line 164 of file timer_common_all.h.

◆ TIM11_ARR

| #define TIM11_ARR TIM_ARR(TIM11) |

Definition at line 290 of file timer_common_all.h.

◆ TIM11_CCER

| #define TIM11_CCER TIM_CCER(TIM11) |

Definition at line 230 of file timer_common_all.h.

◆ TIM11_CCMR1

| #define TIM11_CCMR1 TIM_CCMR1(TIM11) |

Definition at line 203 of file timer_common_all.h.

◆ TIM11_CCR1

| #define TIM11_CCR1 TIM_CCR1(TIM11) |

Definition at line 316 of file timer_common_all.h.

◆ TIM11_CNT

| #define TIM11_CNT TIM_CNT(TIM11) |

Definition at line 250 of file timer_common_all.h.

◆ TIM11_CR1

| #define TIM11_CR1 TIM_CR1(TIM11) |

Definition at line 99 of file timer_common_all.h.

◆ TIM11_DIER

| #define TIM11_DIER TIM_DIER(TIM11) |

Definition at line 145 of file timer_common_all.h.

◆ TIM11_EGR

| #define TIM11_EGR TIM_EGR(TIM11) |

Definition at line 185 of file timer_common_all.h.

◆ TIM11_PSC

| #define TIM11_PSC TIM_PSC(TIM11) |

Definition at line 270 of file timer_common_all.h.

◆ TIM11_SR

| #define TIM11_SR TIM_SR(TIM11) |

Definition at line 165 of file timer_common_all.h.

◆ TIM12_ARR

| #define TIM12_ARR TIM_ARR(TIM12) |

Definition at line 291 of file timer_common_all.h.

◆ TIM12_CCER

| #define TIM12_CCER TIM_CCER(TIM12) |

Definition at line 231 of file timer_common_all.h.

◆ TIM12_CCMR1

| #define TIM12_CCMR1 TIM_CCMR1(TIM12) |

Definition at line 204 of file timer_common_all.h.

◆ TIM12_CCR1

| #define TIM12_CCR1 TIM_CCR1(TIM12) |

Definition at line 317 of file timer_common_all.h.

◆ TIM12_CCR2

| #define TIM12_CCR2 TIM_CCR2(TIM12) |

Definition at line 333 of file timer_common_all.h.

◆ TIM12_CNT

| #define TIM12_CNT TIM_CNT(TIM12) |

Definition at line 251 of file timer_common_all.h.

◆ TIM12_CR1

| #define TIM12_CR1 TIM_CR1(TIM12) |

Definition at line 100 of file timer_common_all.h.

◆ TIM12_DIER

| #define TIM12_DIER TIM_DIER(TIM12) |

Definition at line 146 of file timer_common_all.h.

◆ TIM12_EGR

| #define TIM12_EGR TIM_EGR(TIM12) |

Definition at line 186 of file timer_common_all.h.

◆ TIM12_PSC

| #define TIM12_PSC TIM_PSC(TIM12) |

Definition at line 271 of file timer_common_all.h.

◆ TIM12_SMCR

| #define TIM12_SMCR TIM_SMCR(TIM12) |

Definition at line 130 of file timer_common_all.h.

◆ TIM12_SR

| #define TIM12_SR TIM_SR(TIM12) |

Definition at line 166 of file timer_common_all.h.

◆ TIM13_ARR

| #define TIM13_ARR TIM_ARR(TIM13) |

Definition at line 292 of file timer_common_all.h.

◆ TIM13_CCER

| #define TIM13_CCER TIM_CCER(TIM13) |

Definition at line 232 of file timer_common_all.h.

◆ TIM13_CCMR1

| #define TIM13_CCMR1 TIM_CCMR1(TIM13) |

Definition at line 205 of file timer_common_all.h.

◆ TIM13_CCR1

| #define TIM13_CCR1 TIM_CCR1(TIM13) |

Definition at line 318 of file timer_common_all.h.

◆ TIM13_CNT

| #define TIM13_CNT TIM_CNT(TIM13) |

Definition at line 252 of file timer_common_all.h.

◆ TIM13_CR1

| #define TIM13_CR1 TIM_CR1(TIM13) |

Definition at line 101 of file timer_common_all.h.

◆ TIM13_DIER

| #define TIM13_DIER TIM_DIER(TIM13) |

Definition at line 147 of file timer_common_all.h.

◆ TIM13_EGR

| #define TIM13_EGR TIM_EGR(TIM13) |

Definition at line 187 of file timer_common_all.h.

◆ TIM13_PSC

| #define TIM13_PSC TIM_PSC(TIM13) |

Definition at line 272 of file timer_common_all.h.

◆ TIM13_SR

| #define TIM13_SR TIM_SR(TIM13) |

Definition at line 167 of file timer_common_all.h.

◆ TIM14_ARR

| #define TIM14_ARR TIM_ARR(TIM14) |

Definition at line 293 of file timer_common_all.h.

◆ TIM14_CCER

| #define TIM14_CCER TIM_CCER(TIM14) |

Definition at line 233 of file timer_common_all.h.

◆ TIM14_CCMR1

| #define TIM14_CCMR1 TIM_CCMR1(TIM14) |

Definition at line 206 of file timer_common_all.h.

◆ TIM14_CCR1

| #define TIM14_CCR1 TIM_CCR1(TIM14) |

Definition at line 319 of file timer_common_all.h.

◆ TIM14_CNT

| #define TIM14_CNT TIM_CNT(TIM14) |

Definition at line 253 of file timer_common_all.h.

◆ TIM14_CR1

| #define TIM14_CR1 TIM_CR1(TIM14) |

Definition at line 102 of file timer_common_all.h.

◆ TIM14_DIER

| #define TIM14_DIER TIM_DIER(TIM14) |

Definition at line 148 of file timer_common_all.h.

◆ TIM14_EGR

| #define TIM14_EGR TIM_EGR(TIM14) |

Definition at line 188 of file timer_common_all.h.

◆ TIM14_PSC

| #define TIM14_PSC TIM_PSC(TIM14) |

Definition at line 273 of file timer_common_all.h.

◆ TIM14_SR

| #define TIM14_SR TIM_SR(TIM14) |

Definition at line 168 of file timer_common_all.h.

◆ TIM15_ARR

| #define TIM15_ARR TIM_ARR(TIM15) |

Definition at line 294 of file timer_common_all.h.

◆ TIM15_BDTR

| #define TIM15_BDTR TIM_BDTR(TIM15) |

Definition at line 358 of file timer_common_all.h.

◆ TIM15_CCER

| #define TIM15_CCER TIM_CCER(TIM15) |

Definition at line 234 of file timer_common_all.h.

◆ TIM15_CCMR1

| #define TIM15_CCMR1 TIM_CCMR1(TIM15) |

Definition at line 207 of file timer_common_all.h.

◆ TIM15_CCR1

| #define TIM15_CCR1 TIM_CCR1(TIM15) |

Definition at line 320 of file timer_common_all.h.

◆ TIM15_CCR2

| #define TIM15_CCR2 TIM_CCR2(TIM15) |

Definition at line 334 of file timer_common_all.h.

◆ TIM15_CNT

| #define TIM15_CNT TIM_CNT(TIM15) |

Definition at line 254 of file timer_common_all.h.

◆ TIM15_CR1

| #define TIM15_CR1 TIM_CR1(TIM15) |

Definition at line 103 of file timer_common_all.h.

◆ TIM15_CR2

| #define TIM15_CR2 TIM_CR2(TIM15) |

Definition at line 117 of file timer_common_all.h.

◆ TIM15_DCR

| #define TIM15_DCR TIM_DCR(TIM15) |

Definition at line 370 of file timer_common_all.h.

◆ TIM15_DIER

| #define TIM15_DIER TIM_DIER(TIM15) |

Definition at line 149 of file timer_common_all.h.

◆ TIM15_DMAR

| #define TIM15_DMAR TIM_DMAR(TIM15) |

Definition at line 382 of file timer_common_all.h.

◆ TIM15_EGR

| #define TIM15_EGR TIM_EGR(TIM15) |

Definition at line 189 of file timer_common_all.h.

◆ TIM15_PSC

| #define TIM15_PSC TIM_PSC(TIM15) |

Definition at line 274 of file timer_common_all.h.

◆ TIM15_RCR

| #define TIM15_RCR TIM_RCR(TIM15) |

Definition at line 302 of file timer_common_all.h.

◆ TIM15_SMCR

| #define TIM15_SMCR TIM_SMCR(TIM15) |

Definition at line 131 of file timer_common_all.h.

◆ TIM15_SR

| #define TIM15_SR TIM_SR(TIM15) |

Definition at line 169 of file timer_common_all.h.

◆ TIM16_ARR

| #define TIM16_ARR TIM_ARR(TIM16) |

Definition at line 295 of file timer_common_all.h.

◆ TIM16_BDTR

| #define TIM16_BDTR TIM_BDTR(TIM16) |

Definition at line 359 of file timer_common_all.h.

◆ TIM16_CCER

| #define TIM16_CCER TIM_CCER(TIM16) |

Definition at line 235 of file timer_common_all.h.

◆ TIM16_CCMR1

| #define TIM16_CCMR1 TIM_CCMR1(TIM16) |

Definition at line 208 of file timer_common_all.h.

◆ TIM16_CCR1

| #define TIM16_CCR1 TIM_CCR1(TIM16) |

Definition at line 321 of file timer_common_all.h.

◆ TIM16_CNT

| #define TIM16_CNT TIM_CNT(TIM16) |

Definition at line 255 of file timer_common_all.h.

◆ TIM16_CR1

| #define TIM16_CR1 TIM_CR1(TIM16) |

Definition at line 104 of file timer_common_all.h.

◆ TIM16_CR2

| #define TIM16_CR2 TIM_CR2(TIM16) |

Definition at line 118 of file timer_common_all.h.

◆ TIM16_DCR

| #define TIM16_DCR TIM_DCR(TIM16) |

Definition at line 371 of file timer_common_all.h.

◆ TIM16_DIER

| #define TIM16_DIER TIM_DIER(TIM16) |

Definition at line 150 of file timer_common_all.h.

◆ TIM16_DMAR

| #define TIM16_DMAR TIM_DMAR(TIM16) |

Definition at line 383 of file timer_common_all.h.

◆ TIM16_EGR

| #define TIM16_EGR TIM_EGR(TIM16) |

Definition at line 190 of file timer_common_all.h.

◆ TIM16_PSC

| #define TIM16_PSC TIM_PSC(TIM16) |

Definition at line 275 of file timer_common_all.h.

◆ TIM16_RCR

| #define TIM16_RCR TIM_RCR(TIM16) |

Definition at line 303 of file timer_common_all.h.

◆ TIM16_SR

| #define TIM16_SR TIM_SR(TIM16) |

Definition at line 170 of file timer_common_all.h.

◆ TIM17_ARR

| #define TIM17_ARR TIM_ARR(TIM17) |

Definition at line 296 of file timer_common_all.h.

◆ TIM17_BDTR

| #define TIM17_BDTR TIM_BDTR(TIM17) |

Definition at line 360 of file timer_common_all.h.

◆ TIM17_CCER

| #define TIM17_CCER TIM_CCER(TIM17) |

Definition at line 236 of file timer_common_all.h.

◆ TIM17_CCMR1

| #define TIM17_CCMR1 TIM_CCMR1(TIM17) |

Definition at line 209 of file timer_common_all.h.

◆ TIM17_CCR1

| #define TIM17_CCR1 TIM_CCR1(TIM17) |

Definition at line 322 of file timer_common_all.h.

◆ TIM17_CNT

| #define TIM17_CNT TIM_CNT(TIM17) |

Definition at line 256 of file timer_common_all.h.

◆ TIM17_CR1

| #define TIM17_CR1 TIM_CR1(TIM17) |

Definition at line 105 of file timer_common_all.h.

◆ TIM17_CR2

| #define TIM17_CR2 TIM_CR2(TIM17) |

Definition at line 119 of file timer_common_all.h.

◆ TIM17_DCR

| #define TIM17_DCR TIM_DCR(TIM17) |

Definition at line 372 of file timer_common_all.h.

◆ TIM17_DIER

| #define TIM17_DIER TIM_DIER(TIM17) |

Definition at line 151 of file timer_common_all.h.

◆ TIM17_DMAR

| #define TIM17_DMAR TIM_DMAR(TIM17) |

Definition at line 384 of file timer_common_all.h.

◆ TIM17_EGR

| #define TIM17_EGR TIM_EGR(TIM17) |

Definition at line 191 of file timer_common_all.h.

◆ TIM17_PSC

| #define TIM17_PSC TIM_PSC(TIM17) |

Definition at line 276 of file timer_common_all.h.

◆ TIM17_RCR

| #define TIM17_RCR TIM_RCR(TIM17) |

Definition at line 304 of file timer_common_all.h.

◆ TIM17_SR

| #define TIM17_SR TIM_SR(TIM17) |

Definition at line 171 of file timer_common_all.h.

◆ TIM1_ARR

Definition at line 280 of file timer_common_all.h.

◆ TIM1_BDTR

Definition at line 356 of file timer_common_all.h.

◆ TIM1_CCER

Definition at line 222 of file timer_common_all.h.

◆ TIM1_CCMR1

Definition at line 195 of file timer_common_all.h.

◆ TIM1_CCMR2

Definition at line 213 of file timer_common_all.h.

◆ TIM1_CCR1

Definition at line 308 of file timer_common_all.h.

◆ TIM1_CCR2

Definition at line 326 of file timer_common_all.h.

◆ TIM1_CCR3

Definition at line 338 of file timer_common_all.h.

◆ TIM1_CCR4

Definition at line 347 of file timer_common_all.h.

◆ TIM1_CNT

Definition at line 240 of file timer_common_all.h.

◆ TIM1_CR1

Definition at line 89 of file timer_common_all.h.

◆ TIM1_CR2

Definition at line 109 of file timer_common_all.h.

◆ TIM1_DCR

Definition at line 364 of file timer_common_all.h.

◆ TIM1_DIER

Definition at line 135 of file timer_common_all.h.

◆ TIM1_DMAR

Definition at line 376 of file timer_common_all.h.

◆ TIM1_EGR

Definition at line 175 of file timer_common_all.h.

◆ TIM1_PSC

Definition at line 260 of file timer_common_all.h.

◆ TIM1_RCR

Definition at line 300 of file timer_common_all.h.

◆ TIM1_SMCR

Definition at line 123 of file timer_common_all.h.

◆ TIM1_SR

Definition at line 155 of file timer_common_all.h.

◆ TIM2_ARR

Definition at line 281 of file timer_common_all.h.

◆ TIM2_CCER

Definition at line 223 of file timer_common_all.h.

◆ TIM2_CCMR1

Definition at line 196 of file timer_common_all.h.

◆ TIM2_CCMR2

Definition at line 214 of file timer_common_all.h.

◆ TIM2_CCR1

Definition at line 309 of file timer_common_all.h.

◆ TIM2_CCR2

Definition at line 327 of file timer_common_all.h.

◆ TIM2_CCR3

Definition at line 339 of file timer_common_all.h.

◆ TIM2_CCR4

Definition at line 348 of file timer_common_all.h.

◆ TIM2_CNT

Definition at line 241 of file timer_common_all.h.

◆ TIM2_CR1

Definition at line 90 of file timer_common_all.h.

◆ TIM2_CR2

Definition at line 110 of file timer_common_all.h.

◆ TIM2_DCR

Definition at line 365 of file timer_common_all.h.

◆ TIM2_DIER

Definition at line 136 of file timer_common_all.h.

◆ TIM2_DMAR

Definition at line 377 of file timer_common_all.h.

◆ TIM2_EGR

Definition at line 176 of file timer_common_all.h.

◆ TIM2_PSC

Definition at line 261 of file timer_common_all.h.

◆ TIM2_SMCR

Definition at line 124 of file timer_common_all.h.

◆ TIM2_SR

Definition at line 156 of file timer_common_all.h.

◆ TIM3_ARR

Definition at line 282 of file timer_common_all.h.

◆ TIM3_CCER

Definition at line 224 of file timer_common_all.h.

◆ TIM3_CCMR1

Definition at line 197 of file timer_common_all.h.

◆ TIM3_CCMR2

Definition at line 215 of file timer_common_all.h.

◆ TIM3_CCR1

Definition at line 310 of file timer_common_all.h.

◆ TIM3_CCR2

Definition at line 328 of file timer_common_all.h.

◆ TIM3_CCR3

Definition at line 340 of file timer_common_all.h.

◆ TIM3_CCR4

Definition at line 349 of file timer_common_all.h.

◆ TIM3_CNT

Definition at line 242 of file timer_common_all.h.

◆ TIM3_CR1

Definition at line 91 of file timer_common_all.h.

◆ TIM3_CR2

Definition at line 111 of file timer_common_all.h.

◆ TIM3_DCR

Definition at line 366 of file timer_common_all.h.

◆ TIM3_DIER

Definition at line 137 of file timer_common_all.h.

◆ TIM3_DMAR

Definition at line 378 of file timer_common_all.h.

◆ TIM3_EGR

Definition at line 177 of file timer_common_all.h.

◆ TIM3_PSC

Definition at line 262 of file timer_common_all.h.

◆ TIM3_SMCR

Definition at line 125 of file timer_common_all.h.

◆ TIM3_SR

Definition at line 157 of file timer_common_all.h.

◆ TIM4_ARR

| #define TIM4_ARR TIM_ARR(TIM4) |

Definition at line 283 of file timer_common_all.h.

◆ TIM4_CCER

| #define TIM4_CCER TIM_CCER(TIM4) |

Definition at line 225 of file timer_common_all.h.

◆ TIM4_CCMR1

| #define TIM4_CCMR1 TIM_CCMR1(TIM4) |

Definition at line 198 of file timer_common_all.h.

◆ TIM4_CCMR2

| #define TIM4_CCMR2 TIM_CCMR2(TIM4) |

Definition at line 216 of file timer_common_all.h.

◆ TIM4_CCR1

| #define TIM4_CCR1 TIM_CCR1(TIM4) |

Definition at line 311 of file timer_common_all.h.

◆ TIM4_CCR2

| #define TIM4_CCR2 TIM_CCR2(TIM4) |

Definition at line 329 of file timer_common_all.h.

◆ TIM4_CCR3

| #define TIM4_CCR3 TIM_CCR3(TIM4) |

Definition at line 341 of file timer_common_all.h.

◆ TIM4_CCR4

| #define TIM4_CCR4 TIM_CCR4(TIM4) |

Definition at line 350 of file timer_common_all.h.

◆ TIM4_CNT

| #define TIM4_CNT TIM_CNT(TIM4) |

Definition at line 243 of file timer_common_all.h.

◆ TIM4_CR1

| #define TIM4_CR1 TIM_CR1(TIM4) |

Definition at line 92 of file timer_common_all.h.

◆ TIM4_CR2

| #define TIM4_CR2 TIM_CR2(TIM4) |

Definition at line 112 of file timer_common_all.h.

◆ TIM4_DCR

| #define TIM4_DCR TIM_DCR(TIM4) |

Definition at line 367 of file timer_common_all.h.

◆ TIM4_DIER

| #define TIM4_DIER TIM_DIER(TIM4) |

Definition at line 138 of file timer_common_all.h.

◆ TIM4_DMAR

| #define TIM4_DMAR TIM_DMAR(TIM4) |

Definition at line 379 of file timer_common_all.h.

◆ TIM4_EGR

| #define TIM4_EGR TIM_EGR(TIM4) |

Definition at line 178 of file timer_common_all.h.

◆ TIM4_PSC

| #define TIM4_PSC TIM_PSC(TIM4) |

Definition at line 263 of file timer_common_all.h.

◆ TIM4_SMCR

| #define TIM4_SMCR TIM_SMCR(TIM4) |

Definition at line 126 of file timer_common_all.h.

◆ TIM4_SR

| #define TIM4_SR TIM_SR(TIM4) |

Definition at line 158 of file timer_common_all.h.

◆ TIM5_ARR

Definition at line 284 of file timer_common_all.h.

◆ TIM5_CCER

Definition at line 226 of file timer_common_all.h.

◆ TIM5_CCMR1

Definition at line 199 of file timer_common_all.h.

◆ TIM5_CCMR2

Definition at line 217 of file timer_common_all.h.

◆ TIM5_CCR1

Definition at line 312 of file timer_common_all.h.

◆ TIM5_CCR2

Definition at line 330 of file timer_common_all.h.

◆ TIM5_CCR3

Definition at line 342 of file timer_common_all.h.

◆ TIM5_CCR4

Definition at line 351 of file timer_common_all.h.

◆ TIM5_CNT

Definition at line 244 of file timer_common_all.h.

◆ TIM5_CR1

Definition at line 93 of file timer_common_all.h.

◆ TIM5_CR2

Definition at line 113 of file timer_common_all.h.

◆ TIM5_DCR

Definition at line 368 of file timer_common_all.h.

◆ TIM5_DIER

Definition at line 139 of file timer_common_all.h.

◆ TIM5_DMAR

Definition at line 380 of file timer_common_all.h.

◆ TIM5_EGR

Definition at line 179 of file timer_common_all.h.

◆ TIM5_PSC

Definition at line 264 of file timer_common_all.h.

◆ TIM5_SMCR

Definition at line 127 of file timer_common_all.h.

◆ TIM5_SR

Definition at line 159 of file timer_common_all.h.

◆ TIM6_ARR

Definition at line 285 of file timer_common_all.h.

◆ TIM6_CNT

Definition at line 245 of file timer_common_all.h.

◆ TIM6_CR1

Definition at line 94 of file timer_common_all.h.

◆ TIM6_CR2

Definition at line 114 of file timer_common_all.h.

◆ TIM6_DIER

Definition at line 140 of file timer_common_all.h.

◆ TIM6_EGR

Definition at line 180 of file timer_common_all.h.

◆ TIM6_PSC

Definition at line 265 of file timer_common_all.h.

◆ TIM6_SR

Definition at line 160 of file timer_common_all.h.

◆ TIM7_ARR

Definition at line 286 of file timer_common_all.h.

◆ TIM7_CNT

Definition at line 246 of file timer_common_all.h.

◆ TIM7_CR1

Definition at line 95 of file timer_common_all.h.

◆ TIM7_CR2

Definition at line 115 of file timer_common_all.h.

◆ TIM7_DIER

Definition at line 141 of file timer_common_all.h.

◆ TIM7_EGR

Definition at line 181 of file timer_common_all.h.

◆ TIM7_PSC

Definition at line 266 of file timer_common_all.h.

◆ TIM7_SR

Definition at line 161 of file timer_common_all.h.

◆ TIM8_ARR

| #define TIM8_ARR TIM_ARR(TIM8) |

Definition at line 287 of file timer_common_all.h.

◆ TIM8_BDTR

| #define TIM8_BDTR TIM_BDTR(TIM8) |

Definition at line 357 of file timer_common_all.h.

◆ TIM8_CCER

| #define TIM8_CCER TIM_CCER(TIM8) |

Definition at line 227 of file timer_common_all.h.

◆ TIM8_CCMR1

| #define TIM8_CCMR1 TIM_CCMR1(TIM8) |

Definition at line 200 of file timer_common_all.h.

◆ TIM8_CCMR2

| #define TIM8_CCMR2 TIM_CCMR2(TIM8) |

Definition at line 218 of file timer_common_all.h.

◆ TIM8_CCR1

| #define TIM8_CCR1 TIM_CCR1(TIM8) |

Definition at line 313 of file timer_common_all.h.

◆ TIM8_CCR2

| #define TIM8_CCR2 TIM_CCR2(TIM8) |

Definition at line 331 of file timer_common_all.h.

◆ TIM8_CCR3

| #define TIM8_CCR3 TIM_CCR3(TIM8) |

Definition at line 343 of file timer_common_all.h.

◆ TIM8_CCR4

| #define TIM8_CCR4 TIM_CCR4(TIM8) |

Definition at line 352 of file timer_common_all.h.

◆ TIM8_CNT

| #define TIM8_CNT TIM_CNT(TIM8) |

Definition at line 247 of file timer_common_all.h.

◆ TIM8_CR1

| #define TIM8_CR1 TIM_CR1(TIM8) |

Definition at line 96 of file timer_common_all.h.

◆ TIM8_CR2

| #define TIM8_CR2 TIM_CR2(TIM8) |

Definition at line 116 of file timer_common_all.h.

◆ TIM8_DCR

| #define TIM8_DCR TIM_DCR(TIM8) |

Definition at line 369 of file timer_common_all.h.

◆ TIM8_DIER

| #define TIM8_DIER TIM_DIER(TIM8) |

Definition at line 142 of file timer_common_all.h.

◆ TIM8_DMAR

| #define TIM8_DMAR TIM_DMAR(TIM8) |

Definition at line 381 of file timer_common_all.h.

◆ TIM8_EGR

| #define TIM8_EGR TIM_EGR(TIM8) |

Definition at line 182 of file timer_common_all.h.

◆ TIM8_PSC

| #define TIM8_PSC TIM_PSC(TIM8) |

Definition at line 267 of file timer_common_all.h.

◆ TIM8_RCR

| #define TIM8_RCR TIM_RCR(TIM8) |

Definition at line 301 of file timer_common_all.h.

◆ TIM8_SMCR

| #define TIM8_SMCR TIM_SMCR(TIM8) |

Definition at line 128 of file timer_common_all.h.

◆ TIM8_SR

| #define TIM8_SR TIM_SR(TIM8) |

Definition at line 162 of file timer_common_all.h.

◆ TIM9_ARR

| #define TIM9_ARR TIM_ARR(TIM9) |

Definition at line 288 of file timer_common_all.h.

◆ TIM9_CCER

| #define TIM9_CCER TIM_CCER(TIM9) |

Definition at line 228 of file timer_common_all.h.

◆ TIM9_CCMR1

| #define TIM9_CCMR1 TIM_CCMR1(TIM9) |

Definition at line 201 of file timer_common_all.h.

◆ TIM9_CCR1

| #define TIM9_CCR1 TIM_CCR1(TIM9) |

Definition at line 314 of file timer_common_all.h.

◆ TIM9_CCR2

| #define TIM9_CCR2 TIM_CCR2(TIM9) |

Definition at line 332 of file timer_common_all.h.

◆ TIM9_CNT

| #define TIM9_CNT TIM_CNT(TIM9) |

Definition at line 248 of file timer_common_all.h.

◆ TIM9_CR1

| #define TIM9_CR1 TIM_CR1(TIM9) |

Definition at line 97 of file timer_common_all.h.

◆ TIM9_DIER

| #define TIM9_DIER TIM_DIER(TIM9) |

Definition at line 143 of file timer_common_all.h.

◆ TIM9_EGR

| #define TIM9_EGR TIM_EGR(TIM9) |

Definition at line 183 of file timer_common_all.h.

◆ TIM9_PSC

| #define TIM9_PSC TIM_PSC(TIM9) |

Definition at line 268 of file timer_common_all.h.

◆ TIM9_SMCR

| #define TIM9_SMCR TIM_SMCR(TIM9) |

Definition at line 129 of file timer_common_all.h.

◆ TIM9_SR

| #define TIM9_SR TIM_SR(TIM9) |

Definition at line 163 of file timer_common_all.h.

◆ TIM_ARR

| #define TIM_ARR | ( | tim_base | ) | MMIO32((tim_base) + 0x2C) |

Definition at line 279 of file timer_common_all.h.

◆ TIM_BDTR

| #define TIM_BDTR | ( | tim_base | ) | MMIO32((tim_base) + 0x44) |

Definition at line 355 of file timer_common_all.h.

◆ TIM_BDTR_AOE

| #define TIM_BDTR_AOE (1 << 14) |

Definition at line 1018 of file timer_common_all.h.

◆ TIM_BDTR_BKE

| #define TIM_BDTR_BKE (1 << 12) |

Definition at line 1024 of file timer_common_all.h.

◆ TIM_BDTR_BKP

| #define TIM_BDTR_BKP (1 << 13) |

Definition at line 1021 of file timer_common_all.h.

◆ TIM_BDTR_DBA_MASK

| #define TIM_BDTR_DBA_MASK (0x1F << 0) |

Definition at line 1052 of file timer_common_all.h.

◆ TIM_BDTR_DBL_MASK

| #define TIM_BDTR_DBL_MASK (0x1F << 8) |

Definition at line 1049 of file timer_common_all.h.

◆ TIM_BDTR_DTG_MASK

| #define TIM_BDTR_DTG_MASK 0x00FF |

Definition at line 1044 of file timer_common_all.h.

◆ TIM_BDTR_MOE

| #define TIM_BDTR_MOE (1 << 15) |

Definition at line 1015 of file timer_common_all.h.

◆ TIM_BDTR_OSSI

| #define TIM_BDTR_OSSI (1 << 10) |

Definition at line 1030 of file timer_common_all.h.

◆ TIM_BDTR_OSSR

| #define TIM_BDTR_OSSR (1 << 11) |

Definition at line 1027 of file timer_common_all.h.

◆ TIM_CCER

| #define TIM_CCER | ( | tim_base | ) | MMIO32((tim_base) + 0x20) |

Definition at line 221 of file timer_common_all.h.

◆ TIM_CCER_CC1E

| #define TIM_CCER_CC1E (1 << 0) |

Definition at line 978 of file timer_common_all.h.

◆ TIM_CCER_CC1NE

| #define TIM_CCER_CC1NE (1 << 2) |

Definition at line 972 of file timer_common_all.h.

◆ TIM_CCER_CC1NP

| #define TIM_CCER_CC1NP (1 << 3) |

Definition at line 969 of file timer_common_all.h.

◆ TIM_CCER_CC1P

| #define TIM_CCER_CC1P (1 << 1) |

Definition at line 975 of file timer_common_all.h.

◆ TIM_CCER_CC2E

| #define TIM_CCER_CC2E (1 << 4) |

Definition at line 966 of file timer_common_all.h.

◆ TIM_CCER_CC2NE

| #define TIM_CCER_CC2NE (1 << 6) |

Definition at line 960 of file timer_common_all.h.

◆ TIM_CCER_CC2NP

| #define TIM_CCER_CC2NP (1 << 7) |

Definition at line 957 of file timer_common_all.h.

◆ TIM_CCER_CC2P

| #define TIM_CCER_CC2P (1 << 5) |

Definition at line 963 of file timer_common_all.h.

◆ TIM_CCER_CC3E

| #define TIM_CCER_CC3E (1 << 8) |

Definition at line 954 of file timer_common_all.h.

◆ TIM_CCER_CC3NE

| #define TIM_CCER_CC3NE (1 << 10) |

Definition at line 948 of file timer_common_all.h.

◆ TIM_CCER_CC3NP

| #define TIM_CCER_CC3NP (1 << 11) |

Definition at line 945 of file timer_common_all.h.

◆ TIM_CCER_CC3P

| #define TIM_CCER_CC3P (1 << 9) |

Definition at line 951 of file timer_common_all.h.

◆ TIM_CCER_CC4E

| #define TIM_CCER_CC4E (1 << 12) |

Definition at line 942 of file timer_common_all.h.

◆ TIM_CCER_CC4NP

| #define TIM_CCER_CC4NP (1 << 15) |

Definition at line 936 of file timer_common_all.h.

◆ TIM_CCER_CC4P

| #define TIM_CCER_CC4P (1 << 13) |

Definition at line 939 of file timer_common_all.h.

◆ TIM_CCMR1

| #define TIM_CCMR1 | ( | tim_base | ) | MMIO32((tim_base) + 0x18) |

Definition at line 194 of file timer_common_all.h.

◆ TIM_CCMR1_CC1S_IN_TI1

| #define TIM_CCMR1_CC1S_IN_TI1 (0x1 << 0) |

Definition at line 759 of file timer_common_all.h.

◆ TIM_CCMR1_CC1S_IN_TI2

| #define TIM_CCMR1_CC1S_IN_TI2 (0x2 << 0) |

Definition at line 758 of file timer_common_all.h.

◆ TIM_CCMR1_CC1S_IN_TRC

| #define TIM_CCMR1_CC1S_IN_TRC (0x3 << 0) |

Definition at line 760 of file timer_common_all.h.

◆ TIM_CCMR1_CC1S_MASK

| #define TIM_CCMR1_CC1S_MASK (0x3 << 0) |

Definition at line 761 of file timer_common_all.h.

◆ TIM_CCMR1_CC1S_OUT

| #define TIM_CCMR1_CC1S_OUT (0x0 << 0) |

Definition at line 757 of file timer_common_all.h.

◆ TIM_CCMR1_CC2S_IN_TI1

| #define TIM_CCMR1_CC2S_IN_TI1 (0x2 << 8) |

Definition at line 730 of file timer_common_all.h.

◆ TIM_CCMR1_CC2S_IN_TI2

| #define TIM_CCMR1_CC2S_IN_TI2 (0x1 << 8) |

Definition at line 729 of file timer_common_all.h.

◆ TIM_CCMR1_CC2S_IN_TRC

| #define TIM_CCMR1_CC2S_IN_TRC (0x3 << 8) |

Definition at line 731 of file timer_common_all.h.

◆ TIM_CCMR1_CC2S_MASK

| #define TIM_CCMR1_CC2S_MASK (0x3 << 8) |

Definition at line 732 of file timer_common_all.h.

◆ TIM_CCMR1_CC2S_OUT

| #define TIM_CCMR1_CC2S_OUT (0x0 << 8) |

Definition at line 728 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_CK_INT_N_2

| #define TIM_CCMR1_IC1F_CK_INT_N_2 (0x1 << 4) |

Definition at line 793 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_CK_INT_N_4

| #define TIM_CCMR1_IC1F_CK_INT_N_4 (0x2 << 4) |

Definition at line 794 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_CK_INT_N_8

| #define TIM_CCMR1_IC1F_CK_INT_N_8 (0x3 << 4) |

Definition at line 795 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_16_N_5

| #define TIM_CCMR1_IC1F_DTF_DIV_16_N_5 (0xA << 4) |

Definition at line 802 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_16_N_6

| #define TIM_CCMR1_IC1F_DTF_DIV_16_N_6 (0xB << 4) |

Definition at line 803 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_16_N_8

| #define TIM_CCMR1_IC1F_DTF_DIV_16_N_8 (0xC << 4) |

Definition at line 804 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_2_N_6

| #define TIM_CCMR1_IC1F_DTF_DIV_2_N_6 (0x4 << 4) |

Definition at line 796 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_2_N_8

| #define TIM_CCMR1_IC1F_DTF_DIV_2_N_8 (0x5 << 4) |

Definition at line 797 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_32_N_5

| #define TIM_CCMR1_IC1F_DTF_DIV_32_N_5 (0xD << 4) |

Definition at line 805 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_32_N_6

| #define TIM_CCMR1_IC1F_DTF_DIV_32_N_6 (0xE << 4) |

Definition at line 806 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_32_N_8

| #define TIM_CCMR1_IC1F_DTF_DIV_32_N_8 (0xF << 4) |

Definition at line 807 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_4_N_6

| #define TIM_CCMR1_IC1F_DTF_DIV_4_N_6 (0x6 << 4) |

Definition at line 798 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_4_N_8

| #define TIM_CCMR1_IC1F_DTF_DIV_4_N_8 (0x7 << 4) |

Definition at line 799 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_8_N_6

| #define TIM_CCMR1_IC1F_DTF_DIV_8_N_6 (0x8 << 4) |

Definition at line 800 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_DTF_DIV_8_N_8

| #define TIM_CCMR1_IC1F_DTF_DIV_8_N_8 (0x9 << 4) |

Definition at line 801 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_MASK

| #define TIM_CCMR1_IC1F_MASK (0xF << 4) |

Definition at line 808 of file timer_common_all.h.

◆ TIM_CCMR1_IC1F_OFF

| #define TIM_CCMR1_IC1F_OFF (0x0 << 4) |

Definition at line 792 of file timer_common_all.h.

◆ TIM_CCMR1_IC1PSC_2

| #define TIM_CCMR1_IC1PSC_2 (0x1 << 2) |

Definition at line 812 of file timer_common_all.h.

◆ TIM_CCMR1_IC1PSC_4

| #define TIM_CCMR1_IC1PSC_4 (0x2 << 2) |

Definition at line 813 of file timer_common_all.h.

◆ TIM_CCMR1_IC1PSC_8

| #define TIM_CCMR1_IC1PSC_8 (0x3 << 2) |

Definition at line 814 of file timer_common_all.h.

◆ TIM_CCMR1_IC1PSC_MASK

| #define TIM_CCMR1_IC1PSC_MASK (0x3 << 2) |

Definition at line 815 of file timer_common_all.h.

◆ TIM_CCMR1_IC1PSC_OFF

| #define TIM_CCMR1_IC1PSC_OFF (0x0 << 2) |

Definition at line 811 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_CK_INT_N_2

| #define TIM_CCMR1_IC2F_CK_INT_N_2 (0x1 << 12) |

Definition at line 767 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_CK_INT_N_4

| #define TIM_CCMR1_IC2F_CK_INT_N_4 (0x2 << 12) |

Definition at line 768 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_CK_INT_N_8

| #define TIM_CCMR1_IC2F_CK_INT_N_8 (0x3 << 12) |

Definition at line 769 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_16_N_5

| #define TIM_CCMR1_IC2F_DTF_DIV_16_N_5 (0xA << 12) |

Definition at line 776 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_16_N_6

| #define TIM_CCMR1_IC2F_DTF_DIV_16_N_6 (0xB << 12) |

Definition at line 777 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_16_N_8

| #define TIM_CCMR1_IC2F_DTF_DIV_16_N_8 (0xC << 12) |

Definition at line 778 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_2_N_6

| #define TIM_CCMR1_IC2F_DTF_DIV_2_N_6 (0x4 << 12) |

Definition at line 770 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_2_N_8

| #define TIM_CCMR1_IC2F_DTF_DIV_2_N_8 (0x5 << 12) |

Definition at line 771 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_32_N_5

| #define TIM_CCMR1_IC2F_DTF_DIV_32_N_5 (0xD << 12) |

Definition at line 779 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_32_N_6

| #define TIM_CCMR1_IC2F_DTF_DIV_32_N_6 (0xE << 12) |

Definition at line 780 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_32_N_8

| #define TIM_CCMR1_IC2F_DTF_DIV_32_N_8 (0xF << 12) |

Definition at line 781 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_4_N_6

| #define TIM_CCMR1_IC2F_DTF_DIV_4_N_6 (0x6 << 12) |

Definition at line 772 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_4_N_8

| #define TIM_CCMR1_IC2F_DTF_DIV_4_N_8 (0x7 << 12) |

Definition at line 773 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_8_N_6

| #define TIM_CCMR1_IC2F_DTF_DIV_8_N_6 (0x8 << 12) |

Definition at line 774 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_DTF_DIV_8_N_8

| #define TIM_CCMR1_IC2F_DTF_DIV_8_N_8 (0x9 << 12) |

Definition at line 775 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_MASK

| #define TIM_CCMR1_IC2F_MASK (0xF << 12) |

Definition at line 782 of file timer_common_all.h.

◆ TIM_CCMR1_IC2F_OFF

| #define TIM_CCMR1_IC2F_OFF (0x0 << 12) |

Definition at line 766 of file timer_common_all.h.

◆ TIM_CCMR1_IC2PSC_2

| #define TIM_CCMR1_IC2PSC_2 (0x1 << 10) |

Definition at line 786 of file timer_common_all.h.

◆ TIM_CCMR1_IC2PSC_4

| #define TIM_CCMR1_IC2PSC_4 (0x2 << 10) |

Definition at line 787 of file timer_common_all.h.

◆ TIM_CCMR1_IC2PSC_8

| #define TIM_CCMR1_IC2PSC_8 (0x3 << 10) |

Definition at line 788 of file timer_common_all.h.

◆ TIM_CCMR1_IC2PSC_MASK

| #define TIM_CCMR1_IC2PSC_MASK (0x3 << 10) |

Definition at line 789 of file timer_common_all.h.

◆ TIM_CCMR1_IC2PSC_OFF

| #define TIM_CCMR1_IC2PSC_OFF (0x0 << 10) |

Definition at line 785 of file timer_common_all.h.

◆ TIM_CCMR1_OC1CE

| #define TIM_CCMR1_OC1CE (1 << 7) |

Definition at line 735 of file timer_common_all.h.

◆ TIM_CCMR1_OC1FE

| #define TIM_CCMR1_OC1FE (1 << 2) |

Definition at line 752 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_ACTIVE

| #define TIM_CCMR1_OC1M_ACTIVE (0x1 << 4) |

Definition at line 739 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_FORCE_HIGH

| #define TIM_CCMR1_OC1M_FORCE_HIGH (0x5 << 4) |

Definition at line 743 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_FORCE_LOW

| #define TIM_CCMR1_OC1M_FORCE_LOW (0x4 << 4) |

Definition at line 742 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_FROZEN

| #define TIM_CCMR1_OC1M_FROZEN (0x0 << 4) |

Definition at line 738 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_INACTIVE

| #define TIM_CCMR1_OC1M_INACTIVE (0x2 << 4) |

Definition at line 740 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_MASK

| #define TIM_CCMR1_OC1M_MASK (0x7 << 4) |

Definition at line 746 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_PWM1

| #define TIM_CCMR1_OC1M_PWM1 (0x6 << 4) |

Definition at line 744 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_PWM2

| #define TIM_CCMR1_OC1M_PWM2 (0x7 << 4) |

Definition at line 745 of file timer_common_all.h.

◆ TIM_CCMR1_OC1M_TOGGLE

| #define TIM_CCMR1_OC1M_TOGGLE (0x3 << 4) |

Definition at line 741 of file timer_common_all.h.

◆ TIM_CCMR1_OC1PE

| #define TIM_CCMR1_OC1PE (1 << 3) |

Definition at line 749 of file timer_common_all.h.

◆ TIM_CCMR1_OC2CE

| #define TIM_CCMR1_OC2CE (1 << 15) |

Definition at line 706 of file timer_common_all.h.

◆ TIM_CCMR1_OC2FE

| #define TIM_CCMR1_OC2FE (1 << 10) |

Definition at line 723 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_ACTIVE

| #define TIM_CCMR1_OC2M_ACTIVE (0x1 << 12) |

Definition at line 710 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_FORCE_HIGH

| #define TIM_CCMR1_OC2M_FORCE_HIGH (0x5 << 12) |

Definition at line 714 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_FORCE_LOW

| #define TIM_CCMR1_OC2M_FORCE_LOW (0x4 << 12) |

Definition at line 713 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_FROZEN

| #define TIM_CCMR1_OC2M_FROZEN (0x0 << 12) |

Definition at line 709 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_INACTIVE

| #define TIM_CCMR1_OC2M_INACTIVE (0x2 << 12) |

Definition at line 711 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_MASK

| #define TIM_CCMR1_OC2M_MASK (0x7 << 12) |

Definition at line 717 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_PWM1

| #define TIM_CCMR1_OC2M_PWM1 (0x6 << 12) |

Definition at line 715 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_PWM2

| #define TIM_CCMR1_OC2M_PWM2 (0x7 << 12) |

Definition at line 716 of file timer_common_all.h.

◆ TIM_CCMR1_OC2M_TOGGLE

| #define TIM_CCMR1_OC2M_TOGGLE (0x3 << 12) |

Definition at line 712 of file timer_common_all.h.

◆ TIM_CCMR1_OC2PE

| #define TIM_CCMR1_OC2PE (1 << 11) |

Definition at line 720 of file timer_common_all.h.

◆ TIM_CCMR2

| #define TIM_CCMR2 | ( | tim_base | ) | MMIO32((tim_base) + 0x1C) |

Definition at line 212 of file timer_common_all.h.

◆ TIM_CCMR2_CC3S_IN_TI3

| #define TIM_CCMR2_CC3S_IN_TI3 (0x1 << 0) |

Definition at line 874 of file timer_common_all.h.

◆ TIM_CCMR2_CC3S_IN_TI4

| #define TIM_CCMR2_CC3S_IN_TI4 (0x2 << 0) |

Definition at line 875 of file timer_common_all.h.

◆ TIM_CCMR2_CC3S_IN_TRC

| #define TIM_CCMR2_CC3S_IN_TRC (0x3 << 0) |

Definition at line 876 of file timer_common_all.h.

◆ TIM_CCMR2_CC3S_MASK

| #define TIM_CCMR2_CC3S_MASK (0x3 << 0) |

Definition at line 877 of file timer_common_all.h.

◆ TIM_CCMR2_CC3S_OUT

| #define TIM_CCMR2_CC3S_OUT (0x0 << 0) |

Definition at line 873 of file timer_common_all.h.

◆ TIM_CCMR2_CC4S_IN_TI3

| #define TIM_CCMR2_CC4S_IN_TI3 (0x2 << 8) |

Definition at line 846 of file timer_common_all.h.

◆ TIM_CCMR2_CC4S_IN_TI4

| #define TIM_CCMR2_CC4S_IN_TI4 (0x1 << 8) |

Definition at line 845 of file timer_common_all.h.

◆ TIM_CCMR2_CC4S_IN_TRC

| #define TIM_CCMR2_CC4S_IN_TRC (0x3 << 8) |

Definition at line 847 of file timer_common_all.h.

◆ TIM_CCMR2_CC4S_MASK

| #define TIM_CCMR2_CC4S_MASK (0x3 << 8) |

Definition at line 848 of file timer_common_all.h.

◆ TIM_CCMR2_CC4S_OUT

| #define TIM_CCMR2_CC4S_OUT (0x0 << 8) |

Definition at line 844 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_CK_INT_N_2

| #define TIM_CCMR2_IC3F_CK_INT_N_2 (0x1 << 4) |

Definition at line 909 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_CK_INT_N_4

| #define TIM_CCMR2_IC3F_CK_INT_N_4 (0x2 << 4) |

Definition at line 910 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_CK_INT_N_8

| #define TIM_CCMR2_IC3F_CK_INT_N_8 (0x3 << 4) |

Definition at line 911 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_16_N_5

| #define TIM_CCMR2_IC3F_DTF_DIV_16_N_5 (0xA << 4) |

Definition at line 918 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_16_N_6

| #define TIM_CCMR2_IC3F_DTF_DIV_16_N_6 (0xB << 4) |

Definition at line 919 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_16_N_8

| #define TIM_CCMR2_IC3F_DTF_DIV_16_N_8 (0xC << 4) |

Definition at line 920 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_2_N_6

| #define TIM_CCMR2_IC3F_DTF_DIV_2_N_6 (0x4 << 4) |

Definition at line 912 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_2_N_8

| #define TIM_CCMR2_IC3F_DTF_DIV_2_N_8 (0x5 << 4) |

Definition at line 913 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_32_N_5

| #define TIM_CCMR2_IC3F_DTF_DIV_32_N_5 (0xD << 4) |

Definition at line 921 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_32_N_6

| #define TIM_CCMR2_IC3F_DTF_DIV_32_N_6 (0xE << 4) |

Definition at line 922 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_32_N_8

| #define TIM_CCMR2_IC3F_DTF_DIV_32_N_8 (0xF << 4) |

Definition at line 923 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_4_N_6

| #define TIM_CCMR2_IC3F_DTF_DIV_4_N_6 (0x6 << 4) |

Definition at line 914 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_4_N_8

| #define TIM_CCMR2_IC3F_DTF_DIV_4_N_8 (0x7 << 4) |

Definition at line 915 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_8_N_6

| #define TIM_CCMR2_IC3F_DTF_DIV_8_N_6 (0x8 << 4) |

Definition at line 916 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_DTF_DIV_8_N_8

| #define TIM_CCMR2_IC3F_DTF_DIV_8_N_8 (0x9 << 4) |

Definition at line 917 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_MASK

| #define TIM_CCMR2_IC3F_MASK (0xF << 4) |

Definition at line 924 of file timer_common_all.h.

◆ TIM_CCMR2_IC3F_OFF

| #define TIM_CCMR2_IC3F_OFF (0x0 << 4) |

Definition at line 908 of file timer_common_all.h.

◆ TIM_CCMR2_IC3PSC_2

| #define TIM_CCMR2_IC3PSC_2 (0x1 << 2) |

Definition at line 928 of file timer_common_all.h.

◆ TIM_CCMR2_IC3PSC_4

| #define TIM_CCMR2_IC3PSC_4 (0x2 << 2) |

Definition at line 929 of file timer_common_all.h.

◆ TIM_CCMR2_IC3PSC_8

| #define TIM_CCMR2_IC3PSC_8 (0x3 << 2) |

Definition at line 930 of file timer_common_all.h.

◆ TIM_CCMR2_IC3PSC_MASK

| #define TIM_CCMR2_IC3PSC_MASK (0x3 << 2) |

Definition at line 931 of file timer_common_all.h.

◆ TIM_CCMR2_IC3PSC_OFF

| #define TIM_CCMR2_IC3PSC_OFF (0x0 << 2) |

Definition at line 927 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_CK_INT_N_2

| #define TIM_CCMR2_IC4F_CK_INT_N_2 (0x1 << 12) |

Definition at line 883 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_CK_INT_N_4

| #define TIM_CCMR2_IC4F_CK_INT_N_4 (0x2 << 12) |

Definition at line 884 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_CK_INT_N_8

| #define TIM_CCMR2_IC4F_CK_INT_N_8 (0x3 << 12) |

Definition at line 885 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_16_N_5

| #define TIM_CCMR2_IC4F_DTF_DIV_16_N_5 (0xA << 12) |

Definition at line 892 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_16_N_6

| #define TIM_CCMR2_IC4F_DTF_DIV_16_N_6 (0xB << 12) |

Definition at line 893 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_16_N_8

| #define TIM_CCMR2_IC4F_DTF_DIV_16_N_8 (0xC << 12) |

Definition at line 894 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_2_N_6

| #define TIM_CCMR2_IC4F_DTF_DIV_2_N_6 (0x4 << 12) |

Definition at line 886 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_2_N_8

| #define TIM_CCMR2_IC4F_DTF_DIV_2_N_8 (0x5 << 12) |

Definition at line 887 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_32_N_5

| #define TIM_CCMR2_IC4F_DTF_DIV_32_N_5 (0xD << 12) |

Definition at line 895 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_32_N_6

| #define TIM_CCMR2_IC4F_DTF_DIV_32_N_6 (0xE << 12) |

Definition at line 896 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_32_N_8

| #define TIM_CCMR2_IC4F_DTF_DIV_32_N_8 (0xF << 12) |

Definition at line 897 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_4_N_6

| #define TIM_CCMR2_IC4F_DTF_DIV_4_N_6 (0x6 << 12) |

Definition at line 888 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_4_N_8

| #define TIM_CCMR2_IC4F_DTF_DIV_4_N_8 (0x7 << 12) |

Definition at line 889 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_8_N_6

| #define TIM_CCMR2_IC4F_DTF_DIV_8_N_6 (0x8 << 12) |

Definition at line 890 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_DTF_DIV_8_N_8

| #define TIM_CCMR2_IC4F_DTF_DIV_8_N_8 (0x9 << 12) |

Definition at line 891 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_MASK

| #define TIM_CCMR2_IC4F_MASK (0xF << 12) |

Definition at line 898 of file timer_common_all.h.

◆ TIM_CCMR2_IC4F_OFF

| #define TIM_CCMR2_IC4F_OFF (0x0 << 12) |

Definition at line 882 of file timer_common_all.h.

◆ TIM_CCMR2_IC4PSC_2

| #define TIM_CCMR2_IC4PSC_2 (0x1 << 10) |

Definition at line 902 of file timer_common_all.h.

◆ TIM_CCMR2_IC4PSC_4

| #define TIM_CCMR2_IC4PSC_4 (0x2 << 10) |

Definition at line 903 of file timer_common_all.h.

◆ TIM_CCMR2_IC4PSC_8

| #define TIM_CCMR2_IC4PSC_8 (0x3 << 10) |

Definition at line 904 of file timer_common_all.h.

◆ TIM_CCMR2_IC4PSC_MASK

| #define TIM_CCMR2_IC4PSC_MASK (0x3 << 10) |

Definition at line 905 of file timer_common_all.h.

◆ TIM_CCMR2_IC4PSC_OFF

| #define TIM_CCMR2_IC4PSC_OFF (0x0 << 10) |

Definition at line 901 of file timer_common_all.h.

◆ TIM_CCMR2_OC3CE

| #define TIM_CCMR2_OC3CE (1 << 7) |

Definition at line 851 of file timer_common_all.h.

◆ TIM_CCMR2_OC3FE

| #define TIM_CCMR2_OC3FE (1 << 2) |

Definition at line 868 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_ACTIVE

| #define TIM_CCMR2_OC3M_ACTIVE (0x1 << 4) |

Definition at line 855 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_FORCE_HIGH

| #define TIM_CCMR2_OC3M_FORCE_HIGH (0x5 << 4) |

Definition at line 859 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_FORCE_LOW

| #define TIM_CCMR2_OC3M_FORCE_LOW (0x4 << 4) |

Definition at line 858 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_FROZEN

| #define TIM_CCMR2_OC3M_FROZEN (0x0 << 4) |

Definition at line 854 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_INACTIVE

| #define TIM_CCMR2_OC3M_INACTIVE (0x2 << 4) |

Definition at line 856 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_MASK

| #define TIM_CCMR2_OC3M_MASK (0x7 << 4) |

Definition at line 862 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_PWM1

| #define TIM_CCMR2_OC3M_PWM1 (0x6 << 4) |

Definition at line 860 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_PWM2

| #define TIM_CCMR2_OC3M_PWM2 (0x7 << 4) |

Definition at line 861 of file timer_common_all.h.

◆ TIM_CCMR2_OC3M_TOGGLE

| #define TIM_CCMR2_OC3M_TOGGLE (0x3 << 4) |

Definition at line 857 of file timer_common_all.h.

◆ TIM_CCMR2_OC3PE

| #define TIM_CCMR2_OC3PE (1 << 3) |

Definition at line 865 of file timer_common_all.h.

◆ TIM_CCMR2_OC4CE

| #define TIM_CCMR2_OC4CE (1 << 15) |

Definition at line 822 of file timer_common_all.h.

◆ TIM_CCMR2_OC4FE

| #define TIM_CCMR2_OC4FE (1 << 10) |

Definition at line 839 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_ACTIVE

| #define TIM_CCMR2_OC4M_ACTIVE (0x1 << 12) |

Definition at line 826 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_FORCE_HIGH

| #define TIM_CCMR2_OC4M_FORCE_HIGH (0x5 << 12) |

Definition at line 830 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_FORCE_LOW

| #define TIM_CCMR2_OC4M_FORCE_LOW (0x4 << 12) |

Definition at line 829 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_FROZEN

| #define TIM_CCMR2_OC4M_FROZEN (0x0 << 12) |

Definition at line 825 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_INACTIVE

| #define TIM_CCMR2_OC4M_INACTIVE (0x2 << 12) |

Definition at line 827 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_MASK

| #define TIM_CCMR2_OC4M_MASK (0x7 << 12) |

Definition at line 833 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_PWM1

| #define TIM_CCMR2_OC4M_PWM1 (0x6 << 12) |

Definition at line 831 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_PWM2

| #define TIM_CCMR2_OC4M_PWM2 (0x7 << 12) |

Definition at line 832 of file timer_common_all.h.

◆ TIM_CCMR2_OC4M_TOGGLE

| #define TIM_CCMR2_OC4M_TOGGLE (0x3 << 12) |

Definition at line 828 of file timer_common_all.h.

◆ TIM_CCMR2_OC4PE

| #define TIM_CCMR2_OC4PE (1 << 11) |

Definition at line 836 of file timer_common_all.h.

◆ TIM_CCR1

| #define TIM_CCR1 | ( | tim_base | ) | MMIO32((tim_base) + 0x34) |

Definition at line 307 of file timer_common_all.h.

◆ TIM_CCR2

| #define TIM_CCR2 | ( | tim_base | ) | MMIO32((tim_base) + 0x38) |

Definition at line 325 of file timer_common_all.h.

◆ TIM_CCR3

| #define TIM_CCR3 | ( | tim_base | ) | MMIO32((tim_base) + 0x3C) |

Definition at line 337 of file timer_common_all.h.

◆ TIM_CCR4

| #define TIM_CCR4 | ( | tim_base | ) | MMIO32((tim_base) + 0x40) |

Definition at line 346 of file timer_common_all.h.

◆ TIM_CNT

| #define TIM_CNT | ( | tim_base | ) | MMIO32((tim_base) + 0x24) |

Definition at line 239 of file timer_common_all.h.

◆ TIM_CR1

| #define TIM_CR1 | ( | tim_base | ) | MMIO32((tim_base) + 0x00) |

Definition at line 88 of file timer_common_all.h.

◆ TIM_CR1_ARPE

| #define TIM_CR1_ARPE (1 << 7) |

Definition at line 399 of file timer_common_all.h.

◆ TIM_CR1_CEN

| #define TIM_CR1_CEN (1 << 0) |

Definition at line 430 of file timer_common_all.h.

◆ TIM_CR1_OPM

| #define TIM_CR1_OPM (1 << 3) |

Definition at line 421 of file timer_common_all.h.

◆ TIM_CR1_UDIS

| #define TIM_CR1_UDIS (1 << 1) |

Definition at line 427 of file timer_common_all.h.

◆ TIM_CR1_URS

| #define TIM_CR1_URS (1 << 2) |

Definition at line 424 of file timer_common_all.h.

◆ TIM_CR2

| #define TIM_CR2 | ( | tim_base | ) | MMIO32((tim_base) + 0x04) |

Definition at line 108 of file timer_common_all.h.

◆ TIM_CR2_CCDS

| #define TIM_CR2_CCDS (1 << 3) |

Definition at line 479 of file timer_common_all.h.

◆ TIM_CR2_CCPC

| #define TIM_CR2_CCPC (1 << 0) |

Definition at line 485 of file timer_common_all.h.

◆ TIM_CR2_CCUS

| #define TIM_CR2_CCUS (1 << 2) |

Definition at line 482 of file timer_common_all.h.

◆ TIM_CR2_TI1S

| #define TIM_CR2_TI1S (1 << 7) |

Definition at line 461 of file timer_common_all.h.

◆ TIM_DCR

| #define TIM_DCR | ( | tim_base | ) | MMIO32((tim_base) + 0x48) |

Definition at line 363 of file timer_common_all.h.

◆ TIM_DIER

| #define TIM_DIER | ( | tim_base | ) | MMIO32((tim_base) + 0x0C) |

Definition at line 134 of file timer_common_all.h.

◆ TIM_DMAR

| #define TIM_DMAR | ( | tim_base | ) | MMIO32((tim_base) + 0x4C) |

Definition at line 375 of file timer_common_all.h.

◆ TIM_EGR

| #define TIM_EGR | ( | tim_base | ) | MMIO32((tim_base) + 0x14) |

Definition at line 174 of file timer_common_all.h.

◆ TIM_PSC

| #define TIM_PSC | ( | tim_base | ) | MMIO32((tim_base) + 0x28) |

Definition at line 259 of file timer_common_all.h.

◆ TIM_RCR

| #define TIM_RCR | ( | tim_base | ) | MMIO32((tim_base) + 0x30) |

Definition at line 299 of file timer_common_all.h.

◆ TIM_SMCR

| #define TIM_SMCR | ( | tim_base | ) | MMIO32((tim_base) + 0x08) |

Definition at line 122 of file timer_common_all.h.

◆ TIM_SMCR_ECE

| #define TIM_SMCR_ECE (1 << 14) |

Definition at line 493 of file timer_common_all.h.

◆ TIM_SMCR_ETF_CK_INT_N_2

| #define TIM_SMCR_ETF_CK_INT_N_2 (0x1 << 8) |

Definition at line 504 of file timer_common_all.h.

◆ TIM_SMCR_ETF_CK_INT_N_4

| #define TIM_SMCR_ETF_CK_INT_N_4 (0x2 << 8) |

Definition at line 505 of file timer_common_all.h.

◆ TIM_SMCR_ETF_CK_INT_N_8

| #define TIM_SMCR_ETF_CK_INT_N_8 (0x3 << 8) |

Definition at line 506 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_16_N_5

| #define TIM_SMCR_ETF_DTS_DIV_16_N_5 (0xA << 8) |

Definition at line 513 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_16_N_6

| #define TIM_SMCR_ETF_DTS_DIV_16_N_6 (0xB << 8) |

Definition at line 514 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_16_N_8

| #define TIM_SMCR_ETF_DTS_DIV_16_N_8 (0xC << 8) |

Definition at line 515 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_2_N_6

| #define TIM_SMCR_ETF_DTS_DIV_2_N_6 (0x4 << 8) |

Definition at line 507 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_2_N_8

| #define TIM_SMCR_ETF_DTS_DIV_2_N_8 (0x5 << 8) |

Definition at line 508 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_32_N_5

| #define TIM_SMCR_ETF_DTS_DIV_32_N_5 (0xD << 8) |

Definition at line 516 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_32_N_6

| #define TIM_SMCR_ETF_DTS_DIV_32_N_6 (0xE << 8) |

Definition at line 517 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_32_N_8

| #define TIM_SMCR_ETF_DTS_DIV_32_N_8 (0xF << 8) |

Definition at line 518 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_4_N_6

| #define TIM_SMCR_ETF_DTS_DIV_4_N_6 (0x6 << 8) |

Definition at line 509 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_4_N_8

| #define TIM_SMCR_ETF_DTS_DIV_4_N_8 (0x7 << 8) |

Definition at line 510 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_8_N_6

| #define TIM_SMCR_ETF_DTS_DIV_8_N_6 (0x8 << 8) |

Definition at line 511 of file timer_common_all.h.

◆ TIM_SMCR_ETF_DTS_DIV_8_N_8

| #define TIM_SMCR_ETF_DTS_DIV_8_N_8 (0x9 << 8) |

Definition at line 512 of file timer_common_all.h.

◆ TIM_SMCR_ETF_MASK

| #define TIM_SMCR_ETF_MASK (0xF << 8) |

Definition at line 519 of file timer_common_all.h.

◆ TIM_SMCR_ETF_OFF

| #define TIM_SMCR_ETF_OFF (0x0 << 8) |

Definition at line 503 of file timer_common_all.h.

◆ TIM_SMCR_ETP

| #define TIM_SMCR_ETP (1 << 15) |

Definition at line 490 of file timer_common_all.h.

◆ TIM_SMCR_ETPS_ETRP_DIV_2

| #define TIM_SMCR_ETPS_ETRP_DIV_2 (0x1 << 12) |

Definition at line 497 of file timer_common_all.h.

◆ TIM_SMCR_ETPS_ETRP_DIV_4

| #define TIM_SMCR_ETPS_ETRP_DIV_4 (0x2 << 12) |

Definition at line 498 of file timer_common_all.h.

◆ TIM_SMCR_ETPS_ETRP_DIV_8

| #define TIM_SMCR_ETPS_ETRP_DIV_8 (0x3 << 12) |

Definition at line 499 of file timer_common_all.h.

◆ TIM_SMCR_ETPS_MASK

| #define TIM_SMCR_ETPS_MASK (0X3 << 12) |

Definition at line 500 of file timer_common_all.h.

◆ TIM_SMCR_ETPS_OFF

| #define TIM_SMCR_ETPS_OFF (0x0 << 12) |

Definition at line 496 of file timer_common_all.h.

◆ TIM_SMCR_MSM

| #define TIM_SMCR_MSM (1 << 7) |

Definition at line 522 of file timer_common_all.h.

◆ TIM_SR

| #define TIM_SR | ( | tim_base | ) | MMIO32((tim_base) + 0x10) |

Definition at line 154 of file timer_common_all.h.

Enumeration Type Documentation

◆ tim_ecm2_state

| enum tim_ecm2_state |

External clock mode 2.

| Enumerator | |

|---|---|

| TIM_ECM2_DISABLED | |

| TIM_ECM2_ENABLED | |

Definition at line 1147 of file timer_common_all.h.

◆ tim_et_pol

| enum tim_et_pol |

Slave external trigger polarity.

| Enumerator | |

|---|---|

| TIM_ET_RISING | |

| TIM_ET_FALLING | |

Definition at line 1141 of file timer_common_all.h.

◆ tim_ic_filter

| enum tim_ic_filter |

Input Capture input filter.

The frequency used to sample the input and the number of events needed to validate an output transition.

TIM_IC_CK_INT_N_x No division from the Deadtime and Sampling Clock frequency (DTF), filter length x TIM_IC_DTF_DIV_y_N_x Division by y from the DTF, filter length x

Definition at line 1098 of file timer_common_all.h.

◆ tim_ic_id

| enum tim_ic_id |

Input Capture channel designators.

| Enumerator | |

|---|---|

| TIM_IC1 | |

| TIM_IC2 | |

| TIM_IC3 | |

| TIM_IC4 | |

Definition at line 1084 of file timer_common_all.h.

◆ tim_ic_input

| enum tim_ic_input |

Input Capture input source.

The direction of the channel (input/output) as well as the input used.

| Enumerator | |

|---|---|

| TIM_IC_OUT | |

| TIM_IC_IN_TI1 | |

| TIM_IC_IN_TI2 | |

| TIM_IC_IN_TRC | |

| TIM_IC_IN_TI3 | |

| TIM_IC_IN_TI4 | |

Definition at line 1131 of file timer_common_all.h.

◆ tim_ic_psc

| enum tim_ic_psc |

Input Capture input prescaler.

TIM_IC_PSC_x Input capture is done every x events

| Enumerator | |

|---|---|

| TIM_IC_PSC_OFF | |

| TIM_IC_PSC_2 | |

| TIM_IC_PSC_4 | |

| TIM_IC_PSC_8 | |

Definition at line 1120 of file timer_common_all.h.

◆ tim_oc_id

| enum tim_oc_id |

Output Compare channel designators.

| Enumerator | |

|---|---|

| TIM_OC1 | |

| TIM_OC1N | |

| TIM_OC2 | |

| TIM_OC2N | |

| TIM_OC3 | |

| TIM_OC3N | |

| TIM_OC4 | |

Definition at line 1061 of file timer_common_all.h.

◆ tim_oc_mode

| enum tim_oc_mode |

Output Compare mode designators.

| Enumerator | |

|---|---|

| TIM_OCM_FROZEN | |

| TIM_OCM_ACTIVE | |

| TIM_OCM_INACTIVE | |

| TIM_OCM_TOGGLE | |

| TIM_OCM_FORCE_LOW | |

| TIM_OCM_FORCE_HIGH | |

| TIM_OCM_PWM1 | |

| TIM_OCM_PWM2 | |

Definition at line 1072 of file timer_common_all.h.

Function Documentation

◆ timer_clear_flag()

| void timer_clear_flag | ( | uint32_t | timer_peripheral, |

| uint32_t | flag | ||

| ) |

Clear a Status Flag.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses [in] flag Unsigned int32. TIMx_SR Timer Status Register Flags. Status register flag.

Definition at line 203 of file timer_common_all.c.

References TIM_SR.

◆ timer_continuous_mode()

| void timer_continuous_mode | ( | uint32_t | timer_peripheral | ) |

Enable the Timer to Run Continuously.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 365 of file timer_common_all.c.

References TIM_CR1.

◆ timer_direction_down()

| void timer_direction_down | ( | uint32_t | timer_peripheral | ) |

Set the Timer to Count Down.

This has no effect if the timer is set to center aligned.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 341 of file timer_common_all.c.

References TIM_CR1, and TIM_CR1_DIR_DOWN.

◆ timer_direction_up()

| void timer_direction_up | ( | uint32_t | timer_peripheral | ) |

Set the Timer to Count Up.

This has no effect if the timer is set to center aligned.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 327 of file timer_common_all.c.

References TIM_CR1.

◆ timer_disable_break()

| void timer_disable_break | ( | uint32_t | timer_peripheral | ) |

Disable Break.

Disables the break function of an advanced timer.

- Note

- Not all timers support Break/Deadtime features

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base TIM1 or TIM8

Definition at line 1476 of file timer_common_all.c.

References TIM_BDTR.

◆ timer_disable_break_automatic_output()

| void timer_disable_break_automatic_output | ( | uint32_t | timer_peripheral | ) |

Disable Automatic Output in Break.

Disables the automatic output feature of the Break function of an advanced timer so that the output is re-enabled at the next update event following a break event.

- Note

- Not all timers support Break/Deadtime features

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base TIM1 or TIM8

Definition at line 1412 of file timer_common_all.c.

References TIM_BDTR.

◆ timer_disable_break_main_output()

| void timer_disable_break_main_output | ( | uint32_t | timer_peripheral | ) |

Disable Output in Break.

Disables the output in the Break feature of an advanced timer. This clears the Master Output Enable in the Break and Deadtime Register.

- Note

- Not all timers support Break/Deadtime features

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base TIM1 or TIM8

Definition at line 1376 of file timer_common_all.c.

References TIM_BDTR.

◆ timer_disable_compare_control_update_on_trigger()

| void timer_disable_compare_control_update_on_trigger | ( | uint32_t | timer_peripheral | ) |

Disable Timer Capture/Compare Control Update with Trigger.

If the capture/compare control bits CCxE, CCxNE and OCxM are set to be preloaded, they are updated by software generating the COMG event (timer_generate_event).

- Note

- This setting is only valid for the advanced timer channels with complementary outputs.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 600 of file timer_common_all.c.

References TIM_CR2.

◆ timer_disable_counter()

| void timer_disable_counter | ( | uint32_t | timer_peripheral | ) |

Stop the timer from counting.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 447 of file timer_common_all.c.

References TIM_CR1.

◆ timer_disable_irq()

| void timer_disable_irq | ( | uint32_t | timer_peripheral, |

| uint32_t | irq | ||

| ) |

Disable Interrupts for a Timer.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses [in] irq Unsigned int32. TIMx_DIER Timer DMA and Interrupt Enable Values. Logical OR of all interrupt enable bits to be cleared

Definition at line 145 of file timer_common_all.c.

References TIM_DIER.

◆ timer_disable_oc_clear()

| void timer_disable_oc_clear | ( | uint32_t | timer_peripheral, |

| enum tim_oc_id | oc_id | ||

| ) |

Timer Disable the Output Compare Clear Function.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses [in] oc_id enum tim_oc_id OC channel designators TIM_OCx where x=1..4, TIM_OCxN where x=1..3 (no action taken)

Definition at line 736 of file timer_common_all.c.

References TIM_CCMR1, TIM_CCMR2, TIM_OC1, TIM_OC1N, TIM_OC2, TIM_OC2N, TIM_OC3, TIM_OC3N, and TIM_OC4.

◆ timer_disable_oc_output()

| void timer_disable_oc_output | ( | uint32_t | timer_peripheral, |

| enum tim_oc_id | oc_id | ||

| ) |

Timer Disable the Output Compare.

The channel output compare functionality is disabled.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses [in] oc_id enum tim_oc_id OC channel designators TIM_OCx where x=1..4, TIM_OCxN where x=1..3 (only for advanced timers 1 and 8)

Definition at line 1193 of file timer_common_all.c.

References TIM_CCER, TIM_OC1, TIM_OC1N, TIM_OC2, TIM_OC2N, TIM_OC3, TIM_OC3N, and TIM_OC4.

◆ timer_disable_oc_preload()

| void timer_disable_oc_preload | ( | uint32_t | timer_peripheral, |

| enum tim_oc_id | oc_id | ||

| ) |

Timer Disable the Output Compare Preload Register.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses [in] oc_id enum tim_oc_id OC channel designators TIM_OCx where x=1..4, TIM_OCxN where x=1..3 (no action)

Definition at line 1041 of file timer_common_all.c.

References TIM_CCMR1, TIM_CCMR2, TIM_OC1, TIM_OC1N, TIM_OC2, TIM_OC2N, TIM_OC3, TIM_OC3N, and TIM_OC4.

◆ timer_disable_preload()

| void timer_disable_preload | ( | uint32_t | timer_peripheral | ) |

Disable Auto-Reload Buffering.

This causes the counter to be loaded immediately with a new count value when the auto-reload register is written, so that the new value becomes effective for the current count cycle rather than for the cycle following an update event.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 296 of file timer_common_all.c.

References TIM_CR1.

◆ timer_disable_preload_complementry_enable_bits()

| void timer_disable_preload_complementry_enable_bits | ( | uint32_t | timer_peripheral | ) |

Disable Timer Capture/Compare Control Preload.

The capture/compare control bits CCxE, CCxNE and OCxM preload is disabled.

- Note

- This setting is only valid for the advanced timer channels with complementary outputs.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 635 of file timer_common_all.c.

References TIM_CR2.

◆ timer_disable_update_event()

| void timer_disable_update_event | ( | uint32_t | timer_peripheral | ) |

Disable Timer Update Events.

Update events are not generated and the shadow registers keep their values.

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base Timer register base addresses

Definition at line 421 of file timer_common_all.c.

References TIM_CR1, and TIM_CR1_UDIS.

◆ timer_enable_break()

| void timer_enable_break | ( | uint32_t | timer_peripheral | ) |

Enable Break.

Enables the break function of an advanced timer.

- Note

- Not all timers support Break/Deadtime features

- Parameters

-

[in] timer_peripheral Unsigned int32. Timer register address base TIM1 or TIM8

Definition at line 1460 of file timer_common_all.c.

References TIM_BDTR, and TIM_BDTR_BKE.

◆ timer_enable_break_automatic_output()

| void timer_enable_break_automatic_output | ( | uint32_t | timer_peripheral | ) |

Enable Automatic Output in Break.