scb.h File Reference

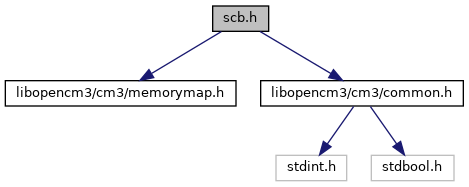

Include dependency graph for scb.h:

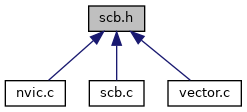

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | scb_exception_stack_frame |

Macros | |

| #define | SCB_CPUID MMIO32(SCB_BASE + 0x00) |

| CPUID: CPUID base register. More... | |

| #define | SCB_ICSR MMIO32(SCB_BASE + 0x04) |

| ICSR: Interrupt Control State Register. More... | |

| #define | SCB_VTOR MMIO32(SCB_BASE + 0x08) |

| VTOR: Vector Table Offset Register. More... | |

| #define | SCB_AIRCR MMIO32(SCB_BASE + 0x0C) |

| AIRCR: Application Interrupt and Reset Control Register. More... | |

| #define | SCB_SCR MMIO32(SCB_BASE + 0x10) |

| SCR: System Control Register. More... | |

| #define | SCB_CCR MMIO32(SCB_BASE + 0x14) |

| CCR: Configuration Control Register. More... | |

| #define | SCB_SHPR32(ipr_id) MMIO32(SCS_BASE + 0xD18 + ((ipr_id) * 4)) |

| System Handler Priority 8 bits Registers, SHPR1/2/3. More... | |

| #define | SCB_SHCSR MMIO32(SCB_BASE + 0x24) |

| SHCSR: System Handler Control and State Register. More... | |

| #define | SCB_DFSR MMIO32(SCB_BASE + 0x30) |

| DFSR: Debug Fault Status Register. More... | |

| #define | SCB_CPUID_IMPLEMENTER_LSB 24 |

| Implementer[31:24]: Implementer code. More... | |

| #define | SCB_CPUID_IMPLEMENTER (0xFF << SCB_CPUID_IMPLEMENTER_LSB) |

| #define | SCB_CPUID_VARIANT_LSB 20 |

| Variant[23:20]: Variant number. More... | |

| #define | SCB_CPUID_VARIANT (0xF << SCB_CPUID_VARIANT_LSB) |

| #define | SCB_CPUID_CONSTANT_LSB 16 |

| Constant[19:16] Reads as 0xF (ARMv7-M) M3, M4 Reads as 0xC (ARMv6-M) M0, M0+. More... | |

| #define | SCB_CPUID_CONSTANT (0xF << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_CONSTANT_ARMV6 (0xC << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_CONSTANT_ARMV7 (0xF << SCB_CPUID_CONSTANT_LSB) |

| #define | SCB_CPUID_PARTNO_LSB 4 |

| PartNo[15:4]: Part number of the processor. More... | |

| #define | SCB_CPUID_PARTNO (0xFFF << SCB_CPUID_PARTNO_LSB) |

| #define | SCB_CPUID_REVISION_LSB 0 |

| Revision[3:0]: Revision number. More... | |

| #define | SCB_CPUID_REVISION (0xF << SCB_CPUID_REVISION_LSB) |

| #define | SCB_ICSR_NMIPENDSET (1 << 31) |

| NMIPENDSET: NMI set-pending bit. More... | |

| #define | SCB_ICSR_PENDSVSET (1 << 28) |

| PENDSVSET: PendSV set-pending bit. More... | |

| #define | SCB_ICSR_PENDSVCLR (1 << 27) |

| PENDSVCLR: PendSV clear-pending bit. More... | |

| #define | SCB_ICSR_PENDSTSET (1 << 26) |

| PENDSTSET: SysTick exception set-pending bit. More... | |

| #define | SCB_ICSR_PENDSTCLR (1 << 25) |

| PENDSTCLR: SysTick exception clear-pending bit. More... | |

| #define | SCB_ICSR_ISRPREEMPT (1 << 23) |

| Bit 23: reserved for debug - reads as 0 when not in debug mode. More... | |

| #define | SCB_ICSR_ISRPENDING (1 << 22) |

| ISRPENDING: Interrupt pending flag, excluding NMI and Faults. More... | |

| #define | SCB_ICSR_VECTPENDING_LSB 12 |

| VECTPENDING[21:12] Pending vector. More... | |

| #define | SCB_ICSR_VECTPENDING (0x1FF << SCB_ICSR_VECTPENDING_LSB) |

| #define | SCB_ICSR_RETOBASE (1 << 11) |

| RETOBASE: Return to base level. More... | |

| #define | SCB_ICSR_VECTACTIVE_LSB 0 |

| VECTACTIVE[8:0] Active vector. More... | |

| #define | SCB_ICSR_VECTACTIVE (0x1FF << SCB_ICSR_VECTACTIVE_LSB) |

| #define | SCB_VTOR_TBLOFF_LSB 7 |

| #define | SCB_VTOR_TBLOFF (0x1FFFFFF << SCB_VTOR_TBLOFF_LSB) |

| #define | SCB_AIRCR_VECTKEYSTAT_LSB 16 |

| VECTKEYSTAT[31:16]/ VECTKEY[31:16] Register key. More... | |

| #define | SCB_AIRCR_VECTKEYSTAT (0xFFFF << SCB_AIRCR_VECTKEYSTAT_LSB) |

| #define | SCB_AIRCR_VECTKEY (0x05FA << SCB_AIRCR_VECTKEYSTAT_LSB) |

| #define | SCB_AIRCR_ENDIANESS (1 << 15) |

| ENDIANNESS Data endianness bit. More... | |

| #define | SCB_AIRCR_SYSRESETREQ (1 << 2) |

| SYSRESETREQ System reset request. More... | |

| #define | SCB_AIRCR_VECTCLRACTIVE (1 << 1) |

| VECTCLRACTIVE clears state information for exceptions. More... | |

| #define | SCB_SCR_SEVONPEND (1 << 4) |

| SEVONPEND Send Event on Pending bit. More... | |

| #define | SCB_SCR_SLEEPDEEP (1 << 2) |

| SLEEPDEEP implementation defined. More... | |

| #define | SCB_SCR_SLEEPONEXIT (1 << 1) |

| SLEEPONEXIT sleep when exiting ISR. More... | |

| #define | SCB_CCR_STKALIGN (1 << 9) |

| STKALIGN set to zero to break things :) More... | |

| #define | SCB_CCR_UNALIGN_TRP (1 << 3) |

| UNALIGN_TRP set to trap on unaligned. More... | |

| #define | SCB_SHPR_PRI_4_MEMMANAGE 0 |

| #define | SCB_SHPR_PRI_5_BUSFAULT 1 |

| #define | SCB_SHPR_PRI_6_USAGEFAULT 2 |

| #define | SCB_SHPR_PRI_7_RESERVED 3 |

| #define | SCB_SHPR_PRI_8_RESERVED 4 |

| #define | SCB_SHPR_PRI_9_RESERVED 5 |

| #define | SCB_SHPR_PRI_10_RESERVED 6 |

| #define | SCB_SHPR_PRI_11_SVCALL 7 |

| #define | SCB_SHPR_PRI_12_RESERVED 8 |

| #define | SCB_SHPR_PRI_13_RESERVED 9 |

| #define | SCB_SHPR_PRI_14_PENDSV 10 |

| #define | SCB_SHPR_PRI_15_SYSTICK 11 |

| #define | SCB_SHCSR_SVCALLPENDED (1 << 15) |

| #define | SCB_GET_EXCEPTION_STACK_FRAME(f) |

Functions | |

| void | scb_reset_system (void) |