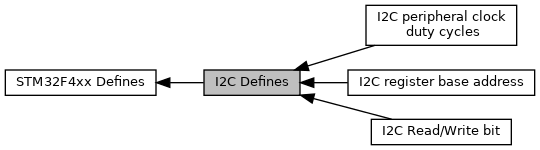

Defined Constants and Types for the STM32F4xx I2C More...

Modules | |

| I2C register base address | |

| I2C peripheral clock duty cycles | |

| I2C Read/Write bit | |

Macros | |

| #define | I2C_FLTR(i2c_base) MMIO32((i2c_base) + 0x24) |

| FLTR register (I2Cx_FLTR) (noise filter) More... | |

| #define | I2C1_FLTR I2C_FLTR(I2C1) |

| #define | I2C2_FLTR I2C_FLTR(I2C2) |

| #define | I2C3_FLTR I2C_FLTR(I2C3) |

| #define | I2C_FLTR_DNF_MASK 0xF |

| Bits [3:0] DNF - Digital noise filter These bits configure a digital noise filter on SDA and SCL pins. More... | |

| #define | I2C_FLTR_DNF_SHIFT 0 |

| #define | I2C_FLTR_ANOFF (1<<4) |

| Bit 4 - Analog Noise filter disable Turns off the built in analog noise filter. More... | |

| #define | I2C_CR1(i2c_base) MMIO32((i2c_base) + 0x00) |

| #define | I2C1_CR1 I2C_CR1(I2C1) |

| #define | I2C2_CR1 I2C_CR1(I2C2) |

| #define | I2C_CR2(i2c_base) MMIO32((i2c_base) + 0x04) |

| #define | I2C1_CR2 I2C_CR2(I2C1) |

| #define | I2C2_CR2 I2C_CR2(I2C2) |

| #define | I2C_OAR1(i2c_base) MMIO32((i2c_base) + 0x08) |

| #define | I2C1_OAR1 I2C_OAR1(I2C1) |

| #define | I2C2_OAR1 I2C_OAR1(I2C2) |

| #define | I2C_OAR2(i2c_base) MMIO32((i2c_base) + 0x0c) |

| #define | I2C1_OAR2 I2C_OAR2(I2C1) |

| #define | I2C2_OAR2 I2C_OAR2(I2C2) |

| #define | I2C_DR(i2c_base) MMIO32((i2c_base) + 0x10) |

| #define | I2C1_DR I2C_DR(I2C1) |

| #define | I2C2_DR I2C_DR(I2C2) |

| #define | I2C_SR1(i2c_base) MMIO32((i2c_base) + 0x14) |

| #define | I2C1_SR1 I2C_SR1(I2C1) |

| #define | I2C2_SR1 I2C_SR1(I2C2) |

| #define | I2C_SR2(i2c_base) MMIO32((i2c_base) + 0x18) |

| #define | I2C1_SR2 I2C_SR2(I2C1) |

| #define | I2C2_SR2 I2C_SR2(I2C2) |

| #define | I2C_CCR(i2c_base) MMIO32((i2c_base) + 0x1c) |

| #define | I2C1_CCR I2C_CCR(I2C1) |

| #define | I2C2_CCR I2C_CCR(I2C2) |

| #define | I2C_TRISE(i2c_base) MMIO32((i2c_base) + 0x20) |

| #define | I2C1_TRISE I2C_TRISE(I2C1) |

| #define | I2C2_TRISE I2C_TRISE(I2C2) |

| #define | I2C_CR1_SWRST (1 << 15) |

| #define | I2C_CR1_ALERT (1 << 13) |

| #define | I2C_CR1_PEC (1 << 12) |

| #define | I2C_CR1_POS (1 << 11) |

| #define | I2C_CR1_ACK (1 << 10) |

| #define | I2C_CR1_STOP (1 << 9) |

| #define | I2C_CR1_START (1 << 8) |

| #define | I2C_CR1_NOSTRETCH (1 << 7) |

| #define | I2C_CR1_ENGC (1 << 6) |

| #define | I2C_CR1_ENPEC (1 << 5) |

| #define | I2C_CR1_ENARP (1 << 4) |

| #define | I2C_CR1_SMBTYPE (1 << 3) |

| #define | I2C_CR1_SMBUS (1 << 1) |

| #define | I2C_CR1_PE (1 << 0) |

| #define | I2C_CR2_LAST (1 << 12) |

| #define | I2C_CR2_DMAEN (1 << 11) |

| #define | I2C_CR2_ITBUFEN (1 << 10) |

| #define | I2C_CR2_ITEVTEN (1 << 9) |

| #define | I2C_CR2_ITERREN (1 << 8) |

| #define | I2C_OAR1_ADDMODE (1 << 15) |

| #define | I2C_OAR1_ADDMODE_7BIT 0 |

| #define | I2C_OAR1_ADDMODE_10BIT 1 |

| #define | I2C_OAR2_ENDUAL (1 << 0) |

| #define | I2C_SR1_SMBALERT (1 << 15) |

| #define | I2C_SR1_TIMEOUT (1 << 14) |

| #define | I2C_SR1_PECERR (1 << 12) |

| #define | I2C_SR1_OVR (1 << 11) |

| #define | I2C_SR1_AF (1 << 10) |

| #define | I2C_SR1_ARLO (1 << 9) |

| #define | I2C_SR1_BERR (1 << 8) |

| #define | I2C_SR1_TxE (1 << 7) |

| #define | I2C_SR1_RxNE (1 << 6) |

| #define | I2C_SR1_STOPF (1 << 4) |

| #define | I2C_SR1_ADD10 (1 << 3) |

| #define | I2C_SR1_BTF (1 << 2) |

| #define | I2C_SR1_ADDR (1 << 1) |

| #define | I2C_SR1_SB (1 << 0) |

| #define | I2C_SR2_DUALF (1 << 7) |

| #define | I2C_SR2_SMBHOST (1 << 6) |

| #define | I2C_SR2_SMBDEFAULT (1 << 5) |

| #define | I2C_SR2_GENCALL (1 << 4) |

| #define | I2C_SR2_TRA (1 << 2) |

| #define | I2C_SR2_BUSY (1 << 1) |

| #define | I2C_SR2_MSL (1 << 0) |

| #define | I2C_CCR_FS (1 << 15) |

Functions | |

| void | i2c_peripheral_enable (uint32_t i2c) |

| I2C Peripheral Enable. More... | |

| void | i2c_peripheral_disable (uint32_t i2c) |

| I2C Peripheral Disable. More... | |

| void | i2c_send_start (uint32_t i2c) |

| I2C Send Start Condition. More... | |

| void | i2c_send_stop (uint32_t i2c) |

| I2C Send Stop Condition. More... | |

| void | i2c_clear_stop (uint32_t i2c) |

| I2C Clear Stop Flag. More... | |

| void | i2c_set_own_7bit_slave_address (uint32_t i2c, uint8_t slave) |

| I2C Set the 7 bit Slave Address for the Peripheral. More... | |

| void | i2c_set_own_10bit_slave_address (uint32_t i2c, uint16_t slave) |

| I2C Set the 10 bit Slave Address for the Peripheral. More... | |

| void | i2c_set_own_7bit_slave_address_two (uint32_t i2c, uint8_t slave) |

| I2C Set the secondary 7 bit Slave Address for the Peripheral. More... | |

| void | i2c_enable_dual_addressing_mode (uint32_t i2c) |

| I2C Enable dual addressing mode for the Peripheral. More... | |

| void | i2c_disable_dual_addressing_mode (uint32_t i2c) |

| I2C Disable dual addressing mode for the Peripheral. More... | |

| void | i2c_set_clock_frequency (uint32_t i2c, uint8_t freq) |

| I2C Set Peripheral Clock Frequency. More... | |

| void | i2c_send_data (uint32_t i2c, uint8_t data) |

| I2C Send Data. More... | |

| void | i2c_set_fast_mode (uint32_t i2c) |

| I2C Set Fast Mode. More... | |

| void | i2c_set_standard_mode (uint32_t i2c) |

| I2C Set Standard Mode. More... | |

| void | i2c_set_ccr (uint32_t i2c, uint16_t freq) |

| I2C Set Bus Clock Frequency. More... | |

| void | i2c_set_trise (uint32_t i2c, uint16_t trise) |

| I2C Set the Rise Time. More... | |

| void | i2c_send_7bit_address (uint32_t i2c, uint8_t slave, uint8_t readwrite) |

| I2C Send the 7-bit Slave Address. More... | |

| uint8_t | i2c_get_data (uint32_t i2c) |

| I2C Get Data. More... | |

| void | i2c_enable_interrupt (uint32_t i2c, uint32_t interrupt) |

| I2C Enable Interrupt. More... | |

| void | i2c_disable_interrupt (uint32_t i2c, uint32_t interrupt) |

| I2C Disable Interrupt. More... | |

| void | i2c_enable_ack (uint32_t i2c) |

| I2C Enable ACK. More... | |

| void | i2c_disable_ack (uint32_t i2c) |

| I2C Disable ACK. More... | |

| void | i2c_nack_next (uint32_t i2c) |

| I2C NACK Next Byte. More... | |

| void | i2c_nack_current (uint32_t i2c) |

| I2C NACK Next Byte. More... | |

| void | i2c_set_dutycycle (uint32_t i2c, uint32_t dutycycle) |

| I2C Set clock duty cycle. More... | |

| void | i2c_enable_dma (uint32_t i2c) |

| I2C Enable DMA. More... | |

| void | i2c_disable_dma (uint32_t i2c) |

| I2C Disable DMA. More... | |

| void | i2c_set_dma_last_transfer (uint32_t i2c) |

| I2C Set DMA last transfer. More... | |

| void | i2c_clear_dma_last_transfer (uint32_t i2c) |

| I2C Clear DMA last transfer. More... | |

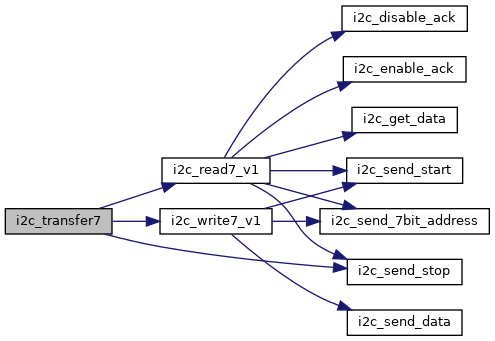

| void | i2c_transfer7 (uint32_t i2c, uint8_t addr, const uint8_t *w, size_t wn, uint8_t *r, size_t rn) |

| Run a write/read transaction to a given 7bit i2c address If both write & read are provided, the read will use repeated start. More... | |

| void | i2c_set_speed (uint32_t i2c, enum i2c_speeds speed, uint32_t clock_megahz) |

| Set the i2c communication speed. More... | |

Detailed Description

Defined Constants and Types for the STM32F4xx I2C

- Version

- 1.0.0

- Date

- 12 October 2012

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ I2C1_CCR

Definition at line 94 of file i2c_common_v1.h.

◆ I2C1_CR1

Definition at line 59 of file i2c_common_v1.h.

◆ I2C1_CR2

Definition at line 64 of file i2c_common_v1.h.

◆ I2C1_DR

Definition at line 79 of file i2c_common_v1.h.

◆ I2C1_FLTR

◆ I2C1_OAR1

Definition at line 69 of file i2c_common_v1.h.

◆ I2C1_OAR2

Definition at line 74 of file i2c_common_v1.h.

◆ I2C1_SR1

Definition at line 84 of file i2c_common_v1.h.

◆ I2C1_SR2

Definition at line 89 of file i2c_common_v1.h.

◆ I2C1_TRISE

Definition at line 99 of file i2c_common_v1.h.

◆ I2C2_CCR

Definition at line 95 of file i2c_common_v1.h.

◆ I2C2_CR1

Definition at line 60 of file i2c_common_v1.h.

◆ I2C2_CR2

Definition at line 65 of file i2c_common_v1.h.

◆ I2C2_DR

Definition at line 80 of file i2c_common_v1.h.

◆ I2C2_FLTR

◆ I2C2_OAR1

Definition at line 70 of file i2c_common_v1.h.

◆ I2C2_OAR2

Definition at line 75 of file i2c_common_v1.h.

◆ I2C2_SR1

Definition at line 85 of file i2c_common_v1.h.

◆ I2C2_SR2

Definition at line 90 of file i2c_common_v1.h.

◆ I2C2_TRISE

Definition at line 100 of file i2c_common_v1.h.

◆ I2C3_FLTR

◆ I2C_CCR

| #define I2C_CCR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x1c) |

Definition at line 93 of file i2c_common_v1.h.

◆ I2C_CCR_FS

| #define I2C_CCR_FS (1 << 15) |

Definition at line 335 of file i2c_common_v1.h.

◆ I2C_CR1

| #define I2C_CR1 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x00) |

Definition at line 58 of file i2c_common_v1.h.

◆ I2C_CR1_ACK

| #define I2C_CR1_ACK (1 << 10) |

Definition at line 132 of file i2c_common_v1.h.

◆ I2C_CR1_ALERT

| #define I2C_CR1_ALERT (1 << 13) |

Definition at line 123 of file i2c_common_v1.h.

◆ I2C_CR1_ENARP

| #define I2C_CR1_ENARP (1 << 4) |

Definition at line 150 of file i2c_common_v1.h.

◆ I2C_CR1_ENGC

| #define I2C_CR1_ENGC (1 << 6) |

Definition at line 144 of file i2c_common_v1.h.

◆ I2C_CR1_ENPEC

| #define I2C_CR1_ENPEC (1 << 5) |

Definition at line 147 of file i2c_common_v1.h.

◆ I2C_CR1_NOSTRETCH

| #define I2C_CR1_NOSTRETCH (1 << 7) |

Definition at line 141 of file i2c_common_v1.h.

◆ I2C_CR1_PE

| #define I2C_CR1_PE (1 << 0) |

Definition at line 161 of file i2c_common_v1.h.

◆ I2C_CR1_PEC

| #define I2C_CR1_PEC (1 << 12) |

Definition at line 126 of file i2c_common_v1.h.

◆ I2C_CR1_POS

| #define I2C_CR1_POS (1 << 11) |

Definition at line 129 of file i2c_common_v1.h.

◆ I2C_CR1_SMBTYPE

| #define I2C_CR1_SMBTYPE (1 << 3) |

Definition at line 153 of file i2c_common_v1.h.

◆ I2C_CR1_SMBUS

| #define I2C_CR1_SMBUS (1 << 1) |

Definition at line 158 of file i2c_common_v1.h.

◆ I2C_CR1_START

| #define I2C_CR1_START (1 << 8) |

Definition at line 138 of file i2c_common_v1.h.

◆ I2C_CR1_STOP

| #define I2C_CR1_STOP (1 << 9) |

Definition at line 135 of file i2c_common_v1.h.

◆ I2C_CR1_SWRST

| #define I2C_CR1_SWRST (1 << 15) |

Definition at line 118 of file i2c_common_v1.h.

◆ I2C_CR2

| #define I2C_CR2 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x04) |

Definition at line 63 of file i2c_common_v1.h.

◆ I2C_CR2_DMAEN

| #define I2C_CR2_DMAEN (1 << 11) |

Definition at line 171 of file i2c_common_v1.h.

◆ I2C_CR2_ITBUFEN

| #define I2C_CR2_ITBUFEN (1 << 10) |

Definition at line 174 of file i2c_common_v1.h.

◆ I2C_CR2_ITERREN

| #define I2C_CR2_ITERREN (1 << 8) |

Definition at line 180 of file i2c_common_v1.h.

◆ I2C_CR2_ITEVTEN

| #define I2C_CR2_ITEVTEN (1 << 9) |

Definition at line 177 of file i2c_common_v1.h.

◆ I2C_CR2_LAST

| #define I2C_CR2_LAST (1 << 12) |

Definition at line 168 of file i2c_common_v1.h.

◆ I2C_DR

| #define I2C_DR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x10) |

Definition at line 78 of file i2c_common_v1.h.

◆ I2C_FLTR

| #define I2C_FLTR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x24) |

◆ I2C_FLTR_ANOFF

| #define I2C_FLTR_ANOFF (1<<4) |

◆ I2C_FLTR_DNF_MASK

| #define I2C_FLTR_DNF_MASK 0xF |

◆ I2C_FLTR_DNF_SHIFT

◆ I2C_OAR1

| #define I2C_OAR1 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x08) |

Definition at line 68 of file i2c_common_v1.h.

◆ I2C_OAR1_ADDMODE

| #define I2C_OAR1_ADDMODE (1 << 15) |

Definition at line 232 of file i2c_common_v1.h.

◆ I2C_OAR1_ADDMODE_10BIT

| #define I2C_OAR1_ADDMODE_10BIT 1 |

Definition at line 234 of file i2c_common_v1.h.

◆ I2C_OAR1_ADDMODE_7BIT

| #define I2C_OAR1_ADDMODE_7BIT 0 |

Definition at line 233 of file i2c_common_v1.h.

◆ I2C_OAR2

| #define I2C_OAR2 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x0c) |

Definition at line 73 of file i2c_common_v1.h.

◆ I2C_OAR2_ENDUAL

| #define I2C_OAR2_ENDUAL (1 << 0) |

Definition at line 249 of file i2c_common_v1.h.

◆ I2C_SR1

| #define I2C_SR1 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x14) |

Definition at line 83 of file i2c_common_v1.h.

◆ I2C_SR1_ADD10

| #define I2C_SR1_ADD10 (1 << 3) |

Definition at line 294 of file i2c_common_v1.h.

◆ I2C_SR1_ADDR

| #define I2C_SR1_ADDR (1 << 1) |

Definition at line 300 of file i2c_common_v1.h.

◆ I2C_SR1_AF

| #define I2C_SR1_AF (1 << 10) |

Definition at line 274 of file i2c_common_v1.h.

◆ I2C_SR1_ARLO

| #define I2C_SR1_ARLO (1 << 9) |

Definition at line 277 of file i2c_common_v1.h.

◆ I2C_SR1_BERR

| #define I2C_SR1_BERR (1 << 8) |

Definition at line 280 of file i2c_common_v1.h.

◆ I2C_SR1_BTF

| #define I2C_SR1_BTF (1 << 2) |

Definition at line 297 of file i2c_common_v1.h.

◆ I2C_SR1_OVR

| #define I2C_SR1_OVR (1 << 11) |

Definition at line 271 of file i2c_common_v1.h.

◆ I2C_SR1_PECERR

| #define I2C_SR1_PECERR (1 << 12) |

Definition at line 268 of file i2c_common_v1.h.

◆ I2C_SR1_RxNE

| #define I2C_SR1_RxNE (1 << 6) |

Definition at line 286 of file i2c_common_v1.h.

◆ I2C_SR1_SB

| #define I2C_SR1_SB (1 << 0) |

Definition at line 303 of file i2c_common_v1.h.

◆ I2C_SR1_SMBALERT

| #define I2C_SR1_SMBALERT (1 << 15) |

Definition at line 260 of file i2c_common_v1.h.

◆ I2C_SR1_STOPF

| #define I2C_SR1_STOPF (1 << 4) |

Definition at line 291 of file i2c_common_v1.h.

◆ I2C_SR1_TIMEOUT

| #define I2C_SR1_TIMEOUT (1 << 14) |

Definition at line 263 of file i2c_common_v1.h.

◆ I2C_SR1_TxE

| #define I2C_SR1_TxE (1 << 7) |

Definition at line 283 of file i2c_common_v1.h.

◆ I2C_SR2

| #define I2C_SR2 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x18) |

Definition at line 88 of file i2c_common_v1.h.

◆ I2C_SR2_BUSY

| #define I2C_SR2_BUSY (1 << 1) |

Definition at line 327 of file i2c_common_v1.h.

◆ I2C_SR2_DUALF

| #define I2C_SR2_DUALF (1 << 7) |

Definition at line 310 of file i2c_common_v1.h.

◆ I2C_SR2_GENCALL

| #define I2C_SR2_GENCALL (1 << 4) |

Definition at line 319 of file i2c_common_v1.h.

◆ I2C_SR2_MSL

| #define I2C_SR2_MSL (1 << 0) |

Definition at line 330 of file i2c_common_v1.h.

◆ I2C_SR2_SMBDEFAULT

| #define I2C_SR2_SMBDEFAULT (1 << 5) |

Definition at line 316 of file i2c_common_v1.h.

◆ I2C_SR2_SMBHOST

| #define I2C_SR2_SMBHOST (1 << 6) |

Definition at line 313 of file i2c_common_v1.h.

◆ I2C_SR2_TRA

| #define I2C_SR2_TRA (1 << 2) |

Definition at line 324 of file i2c_common_v1.h.

◆ I2C_TRISE

| #define I2C_TRISE | ( | i2c_base | ) | MMIO32((i2c_base) + 0x20) |

Definition at line 98 of file i2c_common_v1.h.

Enumeration Type Documentation

◆ i2c_cr2_freq_values

| enum i2c_cr2_freq_values |

Definition at line 184 of file i2c_common_v1.h.

◆ i2c_speeds

| enum i2c_speeds |

I2C speed modes.

| Enumerator | |

|---|---|

| i2c_speed_sm_100k | |

| i2c_speed_fm_400k | |

| i2c_speed_fmp_1m | |

| i2c_speed_unknown | |

Definition at line 379 of file i2c_common_v1.h.

Function Documentation

◆ i2c_clear_dma_last_transfer()

| void i2c_clear_dma_last_transfer | ( | uint32_t | i2c | ) |

I2C Clear DMA last transfer.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 429 of file i2c_common_v1.c.

References I2C_CR2.

◆ i2c_clear_stop()

| void i2c_clear_stop | ( | uint32_t | i2c | ) |

I2C Clear Stop Flag.

Clear the "Send Stop" flag in the I2C config register

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 106 of file i2c_common_v1.c.

References I2C_CR1.

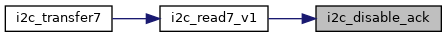

◆ i2c_disable_ack()

| void i2c_disable_ack | ( | uint32_t | i2c | ) |

I2C Disable ACK.

Disables acking of own 7/10 bit address

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 351 of file i2c_common_v1.c.

References I2C_CR1.

Referenced by i2c_read7_v1().

◆ i2c_disable_dma()

| void i2c_disable_dma | ( | uint32_t | i2c | ) |

I2C Disable DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 409 of file i2c_common_v1.c.

References I2C_CR2.

◆ i2c_disable_dual_addressing_mode()

| void i2c_disable_dual_addressing_mode | ( | uint32_t | i2c | ) |

I2C Disable dual addressing mode for the Peripheral.

Only OAR1 is recognised in 7-bit addressing mode.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 181 of file i2c_common_v1.c.

References I2C_OAR2, and I2C_OAR2_ENDUAL.

◆ i2c_disable_interrupt()

| void i2c_disable_interrupt | ( | uint32_t | i2c, |

| uint32_t | interrupt | ||

| ) |

I2C Disable Interrupt.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] interrupt Unsigned int32. Interrupt to disable.

Definition at line 329 of file i2c_common_v1.c.

References I2C_CR2.

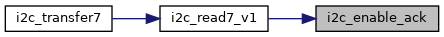

◆ i2c_enable_ack()

| void i2c_enable_ack | ( | uint32_t | i2c | ) |

I2C Enable ACK.

Enables acking of own 7/10 bit address

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 340 of file i2c_common_v1.c.

References I2C_CR1, and I2C_CR1_ACK.

Referenced by i2c_read7_v1().

◆ i2c_enable_dma()

| void i2c_enable_dma | ( | uint32_t | i2c | ) |

I2C Enable DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 399 of file i2c_common_v1.c.

References I2C_CR2, and I2C_CR2_DMAEN.

◆ i2c_enable_dual_addressing_mode()

| void i2c_enable_dual_addressing_mode | ( | uint32_t | i2c | ) |

I2C Enable dual addressing mode for the Peripheral.

Both OAR1 and OAR2 are recognised in 7-bit addressing mode.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 168 of file i2c_common_v1.c.

References I2C_OAR2, and I2C_OAR2_ENDUAL.

◆ i2c_enable_interrupt()

| void i2c_enable_interrupt | ( | uint32_t | i2c, |

| uint32_t | interrupt | ||

| ) |

I2C Enable Interrupt.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] interrupt Unsigned int32. Interrupt to enable.

Definition at line 318 of file i2c_common_v1.c.

References I2C_CR2.

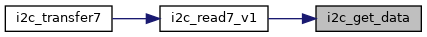

◆ i2c_get_data()

| uint8_t i2c_get_data | ( | uint32_t | i2c | ) |

I2C Get Data.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 307 of file i2c_common_v1.c.

References I2C_DR.

Referenced by i2c_read7_v1().

◆ i2c_nack_current()

| void i2c_nack_current | ( | uint32_t | i2c | ) |

I2C NACK Next Byte.

Causes the I2C controller to NACK the reception of the current byte

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 374 of file i2c_common_v1.c.

References I2C_CR1.

◆ i2c_nack_next()

| void i2c_nack_next | ( | uint32_t | i2c | ) |

I2C NACK Next Byte.

Causes the I2C controller to NACK the reception of the next byte

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 362 of file i2c_common_v1.c.

References I2C_CR1, and I2C_CR1_POS.

◆ i2c_peripheral_disable()

| void i2c_peripheral_disable | ( | uint32_t | i2c | ) |

I2C Peripheral Disable.

This must not be reset while in Master mode until a communication has finished. In Slave mode, the peripheral is disabled only after communication has ended.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 65 of file i2c_common_v1.c.

References I2C_CR1.

◆ i2c_peripheral_enable()

| void i2c_peripheral_enable | ( | uint32_t | i2c | ) |

I2C Peripheral Enable.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 51 of file i2c_common_v1.c.

References I2C_CR1, and I2C_CR1_PE.

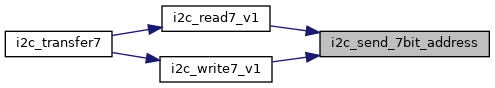

◆ i2c_send_7bit_address()

| void i2c_send_7bit_address | ( | uint32_t | i2c, |

| uint8_t | slave, | ||

| uint8_t | readwrite | ||

| ) |

I2C Send the 7-bit Slave Address.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int16. Slave address 0...1023. [in] readwrite Unsigned int8. Single bit to instruct slave to receive or send I2C Read/Write bit.

Definition at line 297 of file i2c_common_v1.c.

References I2C_DR.

Referenced by i2c_read7_v1(), and i2c_write7_v1().

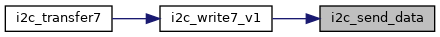

◆ i2c_send_data()

| void i2c_send_data | ( | uint32_t | i2c, |

| uint8_t | data | ||

| ) |

I2C Send Data.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] data Unsigned int8. Byte to send.

Definition at line 214 of file i2c_common_v1.c.

References I2C_DR.

Referenced by i2c_write7_v1().

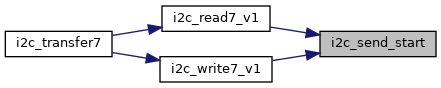

◆ i2c_send_start()

| void i2c_send_start | ( | uint32_t | i2c | ) |

I2C Send Start Condition.

If in Master mode this will cause a restart condition to occur at the end of the current transmission. If in Slave mode, this will initiate a start condition when the current bus activity is completed.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 80 of file i2c_common_v1.c.

References I2C_CR1, and I2C_CR1_START.

Referenced by i2c_read7_v1(), and i2c_write7_v1().

◆ i2c_send_stop()

| void i2c_send_stop | ( | uint32_t | i2c | ) |

I2C Send Stop Condition.

After the current byte transfer this will initiate a stop condition if in Master mode, or simply release the bus if in Slave mode.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 94 of file i2c_common_v1.c.

References I2C_CR1, and I2C_CR1_STOP.

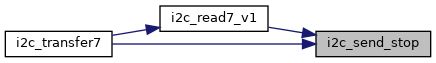

Referenced by i2c_read7_v1(), and i2c_transfer7().

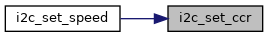

◆ i2c_set_ccr()

| void i2c_set_ccr | ( | uint32_t | i2c, |

| uint16_t | freq | ||

| ) |

I2C Set Bus Clock Frequency.

Set the bus clock frequency. This is a 12 bit number (0...4095) calculated from the formulae given in the STM32F1 reference manual in the description of the CCR field. It is a divisor of the peripheral clock frequency i2c_set_clock_frequency modified by the fast mode setting i2c_set_fast_mode

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] freq Unsigned int16. Bus Clock Frequency Setting 0...4095.

Definition at line 262 of file i2c_common_v1.c.

References I2C_CCR.

Referenced by i2c_set_speed().

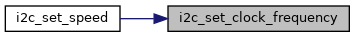

◆ i2c_set_clock_frequency()

| void i2c_set_clock_frequency | ( | uint32_t | i2c, |

| uint8_t | freq | ||

| ) |

I2C Set Peripheral Clock Frequency.

Set the peripheral clock frequency: 2MHz to 36MHz (the APB frequency). Note that this is not the I2C bus clock. This is set in conjunction with the Clock Control register to generate the Master bus clock, see i2c_set_ccr

- Parameters

-

[in] i2c I2C register base address I2C register base address [in] freq Clock Frequency Setting in MHz, valid range depends on part,+ normally 2Mhz->Max APB speed.

Definition at line 199 of file i2c_common_v1.c.

References I2C_CR2.

Referenced by i2c_set_speed().

◆ i2c_set_dma_last_transfer()

| void i2c_set_dma_last_transfer | ( | uint32_t | i2c | ) |

I2C Set DMA last transfer.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 419 of file i2c_common_v1.c.

References I2C_CR2, and I2C_CR2_LAST.

◆ i2c_set_dutycycle()

| void i2c_set_dutycycle | ( | uint32_t | i2c, |

| uint32_t | dutycycle | ||

| ) |

I2C Set clock duty cycle.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] dutycycle Unsigned int32. I2C duty cycle I2C peripheral clock duty cycles.

Definition at line 385 of file i2c_common_v1.c.

References I2C_CCR, I2C_CCR_DUTY, and I2C_CCR_DUTY_DIV2.

◆ i2c_set_fast_mode()

| void i2c_set_fast_mode | ( | uint32_t | i2c | ) |

I2C Set Fast Mode.

Set the clock frequency to the high clock rate mode (up to 400kHz). The actual clock frequency must be set with i2c_set_clock_frequency

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 228 of file i2c_common_v1.c.

References I2C_CCR, and I2C_CCR_FS.

Referenced by i2c_set_speed().

◆ i2c_set_own_10bit_slave_address()

| void i2c_set_own_10bit_slave_address | ( | uint32_t | i2c, |

| uint16_t | slave | ||

| ) |

I2C Set the 10 bit Slave Address for the Peripheral.

This sets an address for Slave mode operation, in 10 bit form.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int16. Slave address 0...1023.

Definition at line 139 of file i2c_common_v1.c.

References I2C_OAR1, and I2C_OAR1_ADDMODE.

◆ i2c_set_own_7bit_slave_address()

| void i2c_set_own_7bit_slave_address | ( | uint32_t | i2c, |

| uint8_t | slave | ||

| ) |

I2C Set the 7 bit Slave Address for the Peripheral.

This sets an address for Slave mode operation, in 7 bit form.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int8. Slave address 0...127.

Definition at line 120 of file i2c_common_v1.c.

References I2C_OAR1.

◆ i2c_set_own_7bit_slave_address_two()

| void i2c_set_own_7bit_slave_address_two | ( | uint32_t | i2c, |

| uint8_t | slave | ||

| ) |

I2C Set the secondary 7 bit Slave Address for the Peripheral.

This sets a secondary address for Slave mode operation, in 7 bit form.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int8. Slave address 0...127.

Definition at line 154 of file i2c_common_v1.c.

References I2C_OAR2.

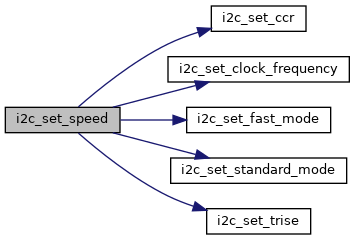

◆ i2c_set_speed()

| void i2c_set_speed | ( | uint32_t | i2c, |

| enum i2c_speeds | speed, | ||

| uint32_t | clock_megahz | ||

| ) |

Set the i2c communication speed.

- Parameters

-

i2c peripheral, eg I2C1 speed one of the listed speed modes i2c_speeds clock_megahz i2c peripheral clock speed in MHz. Usually, rcc_apb1_frequency / 1e6

Definition at line 518 of file i2c_common_v1.c.

References i2c_set_ccr(), i2c_set_clock_frequency(), i2c_set_fast_mode(), i2c_set_standard_mode(), i2c_set_trise(), i2c_speed_fm_400k, and i2c_speed_sm_100k.

◆ i2c_set_standard_mode()

| void i2c_set_standard_mode | ( | uint32_t | i2c | ) |

I2C Set Standard Mode.

Set the clock frequency to the standard clock rate mode (up to 100kHz). The actual clock frequency must be set with i2c_set_clock_frequency

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 242 of file i2c_common_v1.c.

References I2C_CCR.

Referenced by i2c_set_speed().

◆ i2c_set_trise()

| void i2c_set_trise | ( | uint32_t | i2c, |

| uint16_t | trise | ||

| ) |

I2C Set the Rise Time.

Set the maximum rise time on the bus according to the I2C specification, as 1 more than the specified rise time in peripheral clock cycles. This is a 6 bit number.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] trise Unsigned int16. Rise Time Setting 0...63.

Definition at line 283 of file i2c_common_v1.c.

References I2C_TRISE.

Referenced by i2c_set_speed().

◆ i2c_transfer7()

| void i2c_transfer7 | ( | uint32_t | i2c, |

| uint8_t | addr, | ||

| const uint8_t * | w, | ||

| size_t | wn, | ||

| uint8_t * | r, | ||

| size_t | rn | ||

| ) |

Run a write/read transaction to a given 7bit i2c address If both write & read are provided, the read will use repeated start.

Both write and read are optional There are likely still issues with repeated start/stop condtions!

- Parameters

-

i2c peripheral of choice, eg I2C1 addr 7 bit i2c device address w buffer of data to write wn length of w r destination buffer to read into rn number of bytes to read (r should be at least this long)

Definition at line 501 of file i2c_common_v1.c.

References i2c_read7_v1(), i2c_send_stop(), and i2c_write7_v1().