RCC Registers

Reset / Clock Control Registers. More...

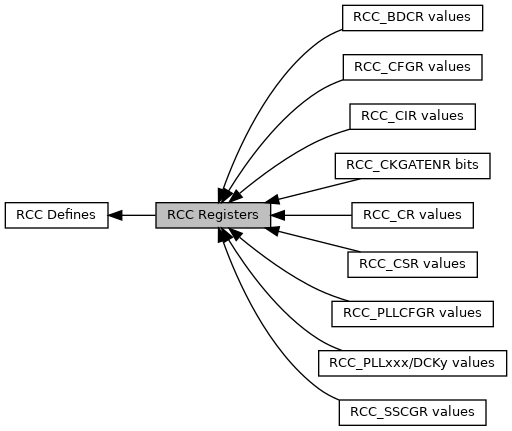

Collaboration diagram for RCC Registers:

Modules | |

| RCC_CR values | |

| Clock Control register values. | |

| RCC_PLLCFGR values | |

| PLL Configuration register values. | |

| RCC_CFGR values | |

| Clock Configuration register values. | |

| RCC_CIR values | |

| Clock Interrupt register values. | |

| RCC_BDCR values | |

| Backup Domain control register values. | |

| RCC_CSR values | |

| Clock control and status register values. | |

| RCC_SSCGR values | |

| Spread spectrum clock generation register values. | |

| RCC_PLLxxx/DCKy values | |

| PLL and other dedicated clock register values. | |

| RCC_CKGATENR bits | |

| Allows to enable or disable the clock gating for the specified IPs. | |

Macros | |

| #define | RCC_CR MMIO32(RCC_BASE + 0x00) |

| Clock control register. More... | |

| #define | RCC_PLLCFGR MMIO32(RCC_BASE + 0x04) |

| PLL Configuration register. More... | |

| #define | RCC_CFGR MMIO32(RCC_BASE + 0x08) |

| Clock Configuration register. More... | |

| #define | RCC_CIR MMIO32(RCC_BASE + 0x0c) |

| Clock interrupt register. More... | |

| #define | RCC_AHB1RSTR MMIO32(RCC_BASE + 0x10) |

| AHB1 peripheral reset register. More... | |

| #define | RCC_AHB2RSTR MMIO32(RCC_BASE + 0x14) |

| AHB2 peripheral reset register. More... | |

| #define | RCC_AHB3RSTR MMIO32(RCC_BASE + 0x18) |

| AHB3 peripheral reset register. More... | |

| #define | RCC_APB1RSTR MMIO32(RCC_BASE + 0x20) |

| APB1 peripheral reset register. More... | |

| #define | RCC_APB2RSTR MMIO32(RCC_BASE + 0x24) |

| APB2 peripheral reset register. More... | |

| #define | RCC_AHB1ENR MMIO32(RCC_BASE + 0x30) |

| AHB1 peripheral enable register. More... | |

| #define | RCC_AHB2ENR MMIO32(RCC_BASE + 0x34) |

| AHB2 peripheral enable register. More... | |

| #define | RCC_AHB3ENR MMIO32(RCC_BASE + 0x38) |

| AHB3 peripheral enable register. More... | |

| #define | RCC_APB1ENR MMIO32(RCC_BASE + 0x40) |

| APB1 peripheral enable register. More... | |

| #define | RCC_APB2ENR MMIO32(RCC_BASE + 0x44) |

| APB2 peripheral enable register. More... | |

| #define | RCC_AHB1LPENR MMIO32(RCC_BASE + 0x50) |

| AHB1 peripheral enable in low power register. More... | |

| #define | RCC_AHB2LPENR MMIO32(RCC_BASE + 0x54) |

| AHB2 peripheral enable in low power register. More... | |

| #define | RCC_AHB3LPENR MMIO32(RCC_BASE + 0x58) |

| AHB3 peripheral enable in low power register. More... | |

| #define | RCC_APB1LPENR MMIO32(RCC_BASE + 0x60) |

| APB1 peripheral enable in low power register. More... | |

| #define | RCC_APB2LPENR MMIO32(RCC_BASE + 0x64) |

| APB2 peripheral enable in low power register. More... | |

| #define | RCC_BDCR MMIO32(RCC_BASE + 0x70) |

| Backup Domain control register. More... | |

| #define | RCC_CSR MMIO32(RCC_BASE + 0x74) |

| Clock control and status register. More... | |

| #define | RCC_SSCGR MMIO32(RCC_BASE + 0x80) |

| Spread spectrum clock generation register. More... | |

| #define | RCC_PLLI2SCFGR MMIO32(RCC_BASE + 0x84) |

| PLLI2S configuration register. More... | |

| #define | RCC_PLLSAICFGR MMIO32(RCC_BASE + 0x88) |

| PLLSAI configuration register. More... | |

| #define | RCC_DCKCFGR MMIO32(RCC_BASE + 0x8C) |

| Dedicated clocks configuration register. More... | |

| #define | RCC_CKGATENR MMIO32(RCC_BASE + 0x90) |

| RCC clocks gated enable register. More... | |

| #define | RCC_DCKCFGR2 MMIO32(RCC_BASE + 0x94) |

| RCC Dedicated Clocks Configuration Register 2. More... | |

Detailed Description

Reset / Clock Control Registers.