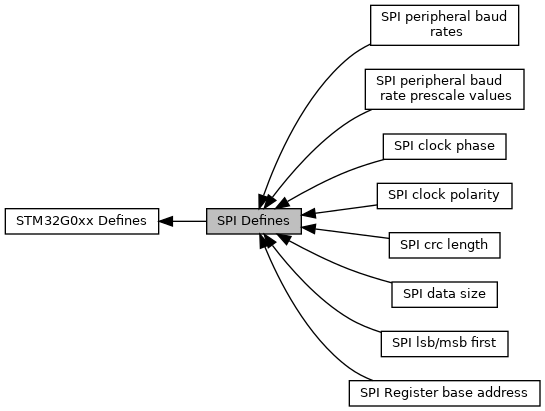

Defined Constants and Types for the STM32G0xx SPI More...

Modules | |

| SPI Register base address | |

| SPI lsb/msb first | |

| SPI peripheral baud rates | |

| SPI peripheral baud rate prescale values | |

| SPI clock polarity | |

| SPI clock phase | |

| SPI crc length | |

| SPI data size | |

Functions | |

| void | spi_enable (uint32_t spi) |

| SPI Enable. More... | |

| void | spi_disable (uint32_t spi) |

| SPI Disable. More... | |

| uint16_t | spi_clean_disable (uint32_t spi) |

| SPI Clean Disable. More... | |

| void | spi_write (uint32_t spi, uint16_t data) |

| SPI Data Write. More... | |

| void | spi_send (uint32_t spi, uint16_t data) |

| SPI Data Write with Blocking. More... | |

| uint16_t | spi_read (uint32_t spi) |

| SPI Data Read. More... | |

| uint16_t | spi_xfer (uint32_t spi, uint16_t data) |

| SPI Data Write and Read Exchange. More... | |

| void | spi_set_bidirectional_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Mode. More... | |

| void | spi_set_unidirectional_mode (uint32_t spi) |

| SPI Set Unidirectional Mode. More... | |

| void | spi_set_bidirectional_receive_only_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Receive Only Mode. More... | |

| void | spi_set_bidirectional_transmit_only_mode (uint32_t spi) |

| SPI Set Bidirectional Simplex Receive Only Mode. More... | |

| void | spi_enable_crc (uint32_t spi) |

| SPI Enable the CRC. More... | |

| void | spi_disable_crc (uint32_t spi) |

| SPI Disable the CRC. More... | |

| void | spi_set_next_tx_from_buffer (uint32_t spi) |

| SPI Next Transmit is a Data Word. More... | |

| void | spi_set_next_tx_from_crc (uint32_t spi) |

| SPI Next Transmit is a CRC Word. More... | |

| void | spi_set_full_duplex_mode (uint32_t spi) |

| SPI Set Full Duplex (3-wire) Mode. More... | |

| void | spi_set_receive_only_mode (uint32_t spi) |

| SPI Set Receive Only Mode for Simplex (2-wire) Unidirectional Transfers. More... | |

| void | spi_disable_software_slave_management (uint32_t spi) |

| SPI Disable Slave Management by Hardware. More... | |

| void | spi_enable_software_slave_management (uint32_t spi) |

| SPI Enable Slave Management by Software. More... | |

| void | spi_set_nss_high (uint32_t spi) |

| SPI Set the Software NSS Signal High. More... | |

| void | spi_set_nss_low (uint32_t spi) |

| SPI Set the Software NSS Signal Low. More... | |

| void | spi_send_lsb_first (uint32_t spi) |

| SPI Set to Send LSB First. More... | |

| void | spi_send_msb_first (uint32_t spi) |

| SPI Set to Send MSB First. More... | |

| void | spi_set_baudrate_prescaler (uint32_t spi, uint8_t baudrate) |

| SPI Set the Baudrate Prescaler. More... | |

| void | spi_set_master_mode (uint32_t spi) |

| SPI Set to Master Mode. More... | |

| void | spi_set_slave_mode (uint32_t spi) |

| SPI Set to Slave Mode. More... | |

| void | spi_set_clock_polarity_1 (uint32_t spi) |

| SPI Set the Clock Polarity to High when Idle. More... | |

| void | spi_set_clock_polarity_0 (uint32_t spi) |

| SPI Set the Clock Polarity to Low when Idle. More... | |

| void | spi_set_clock_phase_1 (uint32_t spi) |

| SPI Set the Clock Phase to Capture on Trailing Edge. More... | |

| void | spi_set_clock_phase_0 (uint32_t spi) |

| SPI Set the Clock Phase to Capture on Leading Edge. More... | |

| void | spi_enable_tx_buffer_empty_interrupt (uint32_t spi) |

| SPI Enable the Transmit Buffer Empty Interrupt. More... | |

| void | spi_disable_tx_buffer_empty_interrupt (uint32_t spi) |

| SPI Disable the Transmit Buffer Empty Interrupt. More... | |

| void | spi_enable_rx_buffer_not_empty_interrupt (uint32_t spi) |

| SPI Enable the Receive Buffer Ready Interrupt. More... | |

| void | spi_disable_rx_buffer_not_empty_interrupt (uint32_t spi) |

| SPI Disable the Receive Buffer Ready Interrupt. More... | |

| void | spi_enable_error_interrupt (uint32_t spi) |

| SPI Enable the Error Interrupt. More... | |

| void | spi_disable_error_interrupt (uint32_t spi) |

| SPI Disable the Error Interrupt. More... | |

| void | spi_enable_ss_output (uint32_t spi) |

| SPI Set the NSS Pin as an Output. More... | |

| void | spi_disable_ss_output (uint32_t spi) |

| SPI Set the NSS Pin as an Input. More... | |

| void | spi_enable_tx_dma (uint32_t spi) |

| SPI Enable Transmit Transfers via DMA. More... | |

| void | spi_disable_tx_dma (uint32_t spi) |

| SPI Disable Transmit Transfers via DMA. More... | |

| void | spi_enable_rx_dma (uint32_t spi) |

| SPI Enable Receive Transfers via DMA. More... | |

| void | spi_disable_rx_dma (uint32_t spi) |

| SPI Disable Receive Transfers via DMA. More... | |

| void | spi_set_standard_mode (uint32_t spi, uint8_t mode) |

| SPI Standard Mode selection. More... | |

| int | spi_init_master (uint32_t spi, uint32_t br, uint32_t cpol, uint32_t cpha, uint32_t lsbfirst) |

| Configure the SPI as Master. More... | |

| void | spi_set_crcl_8bit (uint32_t spi) |

| SPI Set CRC length to 8 bits. More... | |

| void | spi_set_crcl_16bit (uint32_t spi) |

| SPI Set CRC length to 16 bits. More... | |

| void | spi_set_data_size (uint32_t spi, uint16_t data_s) |

| SPI Set data size. More... | |

| void | spi_fifo_reception_threshold_8bit (uint32_t spi) |

| SPI Set reception threshold to 8 bits. More... | |

| void | spi_fifo_reception_threshold_16bit (uint32_t spi) |

| SPI Set reception threshold to 16 bits. More... | |

| void | spi_i2s_mode_spi_mode (uint32_t spi) |

| void | spi_send8 (uint32_t spi, uint8_t data) |

| uint8_t | spi_read8 (uint32_t spi) |

Detailed Description

Defined Constants and Types for the STM32G0xx SPI

- Version

- 1.0.0

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ SPI1_CR1

Definition at line 59 of file spi_common_all.h.

◆ SPI1_CR2

Definition at line 65 of file spi_common_all.h.

◆ SPI1_CRCPR

Definition at line 84 of file spi_common_all.h.

◆ SPI1_DR

Definition at line 77 of file spi_common_all.h.

◆ SPI1_DR8

Definition at line 35 of file spi_common_v2.h.

◆ SPI1_I2SCFGR

| #define SPI1_I2SCFGR SPI_I2SCFGR(SPI1_BASE) |

Definition at line 104 of file spi_common_all.h.

◆ SPI1_I2SPR

Definition at line 110 of file spi_common_all.h.

◆ SPI1_RXCRCR

| #define SPI1_RXCRCR SPI_RXCRCR(SPI1_BASE) |

Definition at line 91 of file spi_common_all.h.

◆ SPI1_SR

Definition at line 71 of file spi_common_all.h.

◆ SPI1_TXCRCR

| #define SPI1_TXCRCR SPI_TXCRCR(SPI1_BASE) |

Definition at line 98 of file spi_common_all.h.

◆ SPI2_CR1

Definition at line 60 of file spi_common_all.h.

◆ SPI2_CR2

Definition at line 66 of file spi_common_all.h.

◆ SPI2_CRCPR

Definition at line 85 of file spi_common_all.h.

◆ SPI2_DR

Definition at line 78 of file spi_common_all.h.

◆ SPI2_DR8

Definition at line 36 of file spi_common_v2.h.

◆ SPI2_I2SCFGR

| #define SPI2_I2SCFGR SPI_I2SCFGR(SPI2_BASE) |

Definition at line 105 of file spi_common_all.h.

◆ SPI2_I2SPR

Definition at line 111 of file spi_common_all.h.

◆ SPI2_RXCRCR

| #define SPI2_RXCRCR SPI_RXCRCR(SPI2_BASE) |

Definition at line 92 of file spi_common_all.h.

◆ SPI2_SR

Definition at line 72 of file spi_common_all.h.

◆ SPI2_TXCRCR

| #define SPI2_TXCRCR SPI_TXCRCR(SPI2_BASE) |

Definition at line 99 of file spi_common_all.h.

◆ SPI3_CR1

Definition at line 61 of file spi_common_all.h.

◆ SPI3_CR2

Definition at line 67 of file spi_common_all.h.

◆ SPI3_CRCPR

Definition at line 86 of file spi_common_all.h.

◆ SPI3_DR

Definition at line 79 of file spi_common_all.h.

◆ SPI3_DR8

Definition at line 37 of file spi_common_v2.h.

◆ SPI3_I2SCFGR

| #define SPI3_I2SCFGR SPI_I2SCFGR(SPI3_BASE) |

Definition at line 106 of file spi_common_all.h.

◆ SPI3_I2SPR

Definition at line 112 of file spi_common_all.h.

◆ SPI3_RXCRCR

| #define SPI3_RXCRCR SPI_RXCRCR(SPI3_BASE) |

Definition at line 93 of file spi_common_all.h.

◆ SPI3_SR

Definition at line 73 of file spi_common_all.h.

◆ SPI3_TXCRCR

| #define SPI3_TXCRCR SPI_TXCRCR(SPI3_BASE) |

Definition at line 100 of file spi_common_all.h.

◆ SPI_CR1

| #define SPI_CR1 | ( | spi_base | ) | MMIO32((spi_base) + 0x00) |

Definition at line 58 of file spi_common_all.h.

◆ SPI_CR1_BIDIMODE

| #define SPI_CR1_BIDIMODE (1 << 15) |

Definition at line 121 of file spi_common_all.h.

◆ SPI_CR1_BIDIMODE_1LINE_BIDIR

| #define SPI_CR1_BIDIMODE_1LINE_BIDIR (1 << 15) |

Definition at line 120 of file spi_common_all.h.

◆ SPI_CR1_BIDIMODE_2LINE_UNIDIR

| #define SPI_CR1_BIDIMODE_2LINE_UNIDIR (0 << 15) |

Definition at line 119 of file spi_common_all.h.

◆ SPI_CR1_BIDIOE

| #define SPI_CR1_BIDIOE (1 << 14) |

Definition at line 124 of file spi_common_all.h.

◆ SPI_CR1_CPHA

| #define SPI_CR1_CPHA (1 << 0) |

Definition at line 207 of file spi_common_all.h.

◆ SPI_CR1_CPOL

| #define SPI_CR1_CPOL (1 << 1) |

Definition at line 196 of file spi_common_all.h.

◆ SPI_CR1_CRCEN

| #define SPI_CR1_CRCEN (1 << 13) |

Definition at line 127 of file spi_common_all.h.

◆ SPI_CR1_CRCL

| #define SPI_CR1_CRCL (1 << 11) |

Definition at line 49 of file spi_common_v2.h.

◆ SPI_CR1_CRCNEXT

| #define SPI_CR1_CRCNEXT (1 << 12) |

Definition at line 130 of file spi_common_all.h.

◆ SPI_CR1_MSTR

| #define SPI_CR1_MSTR (1 << 2) |

Definition at line 185 of file spi_common_all.h.

◆ SPI_CR1_RXONLY

| #define SPI_CR1_RXONLY (1 << 10) |

Definition at line 133 of file spi_common_all.h.

◆ SPI_CR1_SPE

| #define SPI_CR1_SPE (1 << 6) |

Definition at line 152 of file spi_common_all.h.

◆ SPI_CR1_SSI

| #define SPI_CR1_SSI (1 << 8) |

Definition at line 139 of file spi_common_all.h.

◆ SPI_CR1_SSM

| #define SPI_CR1_SSM (1 << 9) |

Definition at line 136 of file spi_common_all.h.

◆ SPI_CR2

| #define SPI_CR2 | ( | spi_base | ) | MMIO32((spi_base) + 0x04) |

Definition at line 64 of file spi_common_all.h.

◆ SPI_CR2_DS_MASK

| #define SPI_CR2_DS_MASK (0xF << 8) |

Definition at line 88 of file spi_common_v2.h.

◆ SPI_CR2_ERRIE

| #define SPI_CR2_ERRIE (1 << 5) |

Definition at line 220 of file spi_common_all.h.

◆ SPI_CR2_FRF

| #define SPI_CR2_FRF (1 << 4) |

Definition at line 64 of file spi_common_v2.h.

◆ SPI_CR2_FRF_MOTOROLA_MODE

| #define SPI_CR2_FRF_MOTOROLA_MODE (0 << 4) |

Definition at line 65 of file spi_common_v2.h.

◆ SPI_CR2_FRF_TI_MODE

| #define SPI_CR2_FRF_TI_MODE (1 << 4) |

Definition at line 66 of file spi_common_v2.h.

◆ SPI_CR2_FRXTH

| #define SPI_CR2_FRXTH (1 << 12) |

Definition at line 60 of file spi_common_v2.h.

◆ SPI_CR2_LDMA_RX

| #define SPI_CR2_LDMA_RX (1 << 13) |

Definition at line 57 of file spi_common_v2.h.

◆ SPI_CR2_LDMA_TX

| #define SPI_CR2_LDMA_TX (1 << 14) |

Definition at line 54 of file spi_common_v2.h.

◆ SPI_CR2_NSSP

| #define SPI_CR2_NSSP (1 << 3) |

Definition at line 91 of file spi_common_v2.h.

◆ SPI_CR2_RXDMAEN

| #define SPI_CR2_RXDMAEN (1 << 0) |

Definition at line 232 of file spi_common_all.h.

◆ SPI_CR2_RXNEIE

| #define SPI_CR2_RXNEIE (1 << 6) |

Definition at line 217 of file spi_common_all.h.

◆ SPI_CR2_SSOE

| #define SPI_CR2_SSOE (1 << 2) |

Definition at line 226 of file spi_common_all.h.

◆ SPI_CR2_TXDMAEN

| #define SPI_CR2_TXDMAEN (1 << 1) |

Definition at line 229 of file spi_common_all.h.

◆ SPI_CR2_TXEIE

| #define SPI_CR2_TXEIE (1 << 7) |

Definition at line 214 of file spi_common_all.h.

◆ SPI_CRCPR

| #define SPI_CRCPR | ( | spi_base | ) | MMIO32((spi_base) + 0x10) |

Definition at line 83 of file spi_common_all.h.

◆ SPI_DR

| #define SPI_DR | ( | spi_base | ) | MMIO32((spi_base) + 0x0c) |

Definition at line 76 of file spi_common_all.h.

◆ SPI_DR8

| #define SPI_DR8 | ( | spi_base | ) | MMIO8((spi_base) + 0x0c) |

Definition at line 34 of file spi_common_v2.h.

◆ SPI_I2SCFGR

| #define SPI_I2SCFGR | ( | spi_base | ) | MMIO32((spi_base) + 0x1c) |

Definition at line 103 of file spi_common_all.h.

◆ SPI_I2SCFGR_CHLEN

| #define SPI_I2SCFGR_CHLEN (1 << 0) |

Definition at line 326 of file spi_common_all.h.

◆ SPI_I2SCFGR_CKPOL

| #define SPI_I2SCFGR_CKPOL (1 << 3) |

Definition at line 317 of file spi_common_all.h.

◆ SPI_I2SCFGR_DATLEN_16BIT

| #define SPI_I2SCFGR_DATLEN_16BIT 0x0 |

Definition at line 321 of file spi_common_all.h.

◆ SPI_I2SCFGR_DATLEN_24BIT

| #define SPI_I2SCFGR_DATLEN_24BIT 0x1 |

Definition at line 322 of file spi_common_all.h.

◆ SPI_I2SCFGR_DATLEN_32BIT

| #define SPI_I2SCFGR_DATLEN_32BIT 0x2 |

Definition at line 323 of file spi_common_all.h.

◆ SPI_I2SCFGR_DATLEN_LSB

| #define SPI_I2SCFGR_DATLEN_LSB 1 |

Definition at line 320 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SCFG_LSB

| #define SPI_I2SCFGR_I2SCFG_LSB 8 |

Definition at line 298 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SCFG_MASTER_RECEIVE

| #define SPI_I2SCFGR_I2SCFG_MASTER_RECEIVE 0x3 |

Definition at line 302 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SCFG_MASTER_TRANSMIT

| #define SPI_I2SCFGR_I2SCFG_MASTER_TRANSMIT 0x2 |

Definition at line 301 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SCFG_SLAVE_RECEIVE

| #define SPI_I2SCFGR_I2SCFG_SLAVE_RECEIVE 0x1 |

Definition at line 300 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SCFG_SLAVE_TRANSMIT

| #define SPI_I2SCFGR_I2SCFG_SLAVE_TRANSMIT 0x0 |

Definition at line 299 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SE

| #define SPI_I2SCFGR_I2SE (1 << 10) |

Definition at line 295 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SMOD

| #define SPI_I2SCFGR_I2SMOD (1 << 11) |

Definition at line 292 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SSTD_I2S_PHILIPS

| #define SPI_I2SCFGR_I2SSTD_I2S_PHILIPS 0x0 |

Definition at line 311 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SSTD_LSB

| #define SPI_I2SCFGR_I2SSTD_LSB 4 |

Definition at line 310 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SSTD_LSB_JUSTIFIED

| #define SPI_I2SCFGR_I2SSTD_LSB_JUSTIFIED 0x2 |

Definition at line 313 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SSTD_MSB_JUSTIFIED

| #define SPI_I2SCFGR_I2SSTD_MSB_JUSTIFIED 0x1 |

Definition at line 312 of file spi_common_all.h.

◆ SPI_I2SCFGR_I2SSTD_PCM

| #define SPI_I2SCFGR_I2SSTD_PCM 0x3 |

Definition at line 314 of file spi_common_all.h.

◆ SPI_I2SCFGR_PCMSYNC

| #define SPI_I2SCFGR_PCMSYNC (1 << 7) |

Definition at line 305 of file spi_common_all.h.

◆ SPI_I2SPR

| #define SPI_I2SPR | ( | spi_base | ) | MMIO32((spi_base) + 0x20) |

Definition at line 109 of file spi_common_all.h.

◆ SPI_I2SPR_MCKOE

| #define SPI_I2SPR_MCKOE (1 << 9) |

Definition at line 335 of file spi_common_all.h.

◆ SPI_I2SPR_ODD

| #define SPI_I2SPR_ODD (1 << 8) |

Definition at line 338 of file spi_common_all.h.

◆ SPI_RXCRCR

| #define SPI_RXCRCR | ( | spi_base | ) | MMIO32((spi_base) + 0x14) |

Definition at line 90 of file spi_common_all.h.

◆ SPI_SR

| #define SPI_SR | ( | spi_base | ) | MMIO32((spi_base) + 0x08) |

Definition at line 70 of file spi_common_all.h.

◆ SPI_SR_BSY

| #define SPI_SR_BSY (1 << 7) |

Definition at line 239 of file spi_common_all.h.

◆ SPI_SR_CHSIDE

| #define SPI_SR_CHSIDE (1 << 2) |

Definition at line 258 of file spi_common_all.h.

◆ SPI_SR_CRCERR

| #define SPI_SR_CRCERR (1 << 4) |

Definition at line 250 of file spi_common_all.h.

◆ SPI_SR_FRE

| #define SPI_SR_FRE (1 << 8) |

Definition at line 108 of file spi_common_v2.h.

◆ SPI_SR_FRLVL_FIFO_EMPTY

| #define SPI_SR_FRLVL_FIFO_EMPTY (0x0 << 9) |

Definition at line 102 of file spi_common_v2.h.

◆ SPI_SR_FRLVL_FIFO_FULL

| #define SPI_SR_FRLVL_FIFO_FULL (0x3 << 9) |

Definition at line 105 of file spi_common_v2.h.

◆ SPI_SR_FRLVL_HALF_FIFO

| #define SPI_SR_FRLVL_HALF_FIFO (0x2 << 9) |

Definition at line 104 of file spi_common_v2.h.

◆ SPI_SR_FRLVL_QUARTER_FIFO

| #define SPI_SR_FRLVL_QUARTER_FIFO (0x1 << 9) |

Definition at line 103 of file spi_common_v2.h.

◆ SPI_SR_FTLVL_FIFO_EMPTY

| #define SPI_SR_FTLVL_FIFO_EMPTY (0x0 << 11) |

Definition at line 96 of file spi_common_v2.h.

◆ SPI_SR_FTLVL_FIFO_FULL

| #define SPI_SR_FTLVL_FIFO_FULL (0x3 << 11) |

Definition at line 99 of file spi_common_v2.h.

◆ SPI_SR_FTLVL_HALF_FIFO

| #define SPI_SR_FTLVL_HALF_FIFO (0x2 << 11) |

Definition at line 98 of file spi_common_v2.h.

◆ SPI_SR_FTLVL_QUARTER_FIFO

| #define SPI_SR_FTLVL_QUARTER_FIFO (0x1 << 11) |

Definition at line 97 of file spi_common_v2.h.

◆ SPI_SR_MODF

| #define SPI_SR_MODF (1 << 5) |

Definition at line 246 of file spi_common_all.h.

◆ SPI_SR_OVR

| #define SPI_SR_OVR (1 << 6) |

Definition at line 242 of file spi_common_all.h.

◆ SPI_SR_RXNE

| #define SPI_SR_RXNE (1 << 0) |

Definition at line 264 of file spi_common_all.h.

◆ SPI_SR_TXE

| #define SPI_SR_TXE (1 << 1) |

Definition at line 261 of file spi_common_all.h.

◆ SPI_SR_UDR

| #define SPI_SR_UDR (1 << 3) |

Definition at line 254 of file spi_common_all.h.

◆ SPI_TXCRCR

| #define SPI_TXCRCR | ( | spi_base | ) | MMIO32((spi_base) + 0x18) |

Definition at line 97 of file spi_common_all.h.

Function Documentation

◆ spi_clean_disable()

| uint16_t spi_clean_disable | ( | uint32_t | spi | ) |

SPI Clean Disable.

Disable the SPI peripheral according to the procedure in section 23.3.8 of the reference manual. This prevents corruption of any ongoing transfers and prevents the BSY flag from becoming unreliable.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- Returns

- data Unsigned int16. 8 or 16 bit data from final read.

Definition at line 104 of file spi_common_all.c.

References SPI_CR1, SPI_DR, SPI_SR, SPI_SR_BSY, SPI_SR_RXNE, and SPI_SR_TXE.

◆ spi_disable()

| void spi_disable | ( | uint32_t | spi | ) |

SPI Disable.

The SPI peripheral is disabled.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 84 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_SPE.

◆ spi_disable_crc()

| void spi_disable_crc | ( | uint32_t | spi | ) |

SPI Disable the CRC.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 276 of file spi_common_all.c.

References SPI_CR1.

◆ spi_disable_error_interrupt()

| void spi_disable_error_interrupt | ( | uint32_t | spi | ) |

SPI Disable the Error Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 570 of file spi_common_all.c.

References SPI_CR2.

◆ spi_disable_rx_buffer_not_empty_interrupt()

| void spi_disable_rx_buffer_not_empty_interrupt | ( | uint32_t | spi | ) |

SPI Disable the Receive Buffer Ready Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 548 of file spi_common_all.c.

References SPI_CR2.

◆ spi_disable_rx_dma()

| void spi_disable_rx_dma | ( | uint32_t | spi | ) |

SPI Disable Receive Transfers via DMA.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 651 of file spi_common_all.c.

References SPI_CR2.

◆ spi_disable_software_slave_management()

| void spi_disable_software_slave_management | ( | uint32_t | spi | ) |

SPI Disable Slave Management by Hardware.

In slave mode the NSS hardware input is used as a select enable for the slave.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 342 of file spi_common_all.c.

References SPI_CR1.

◆ spi_disable_ss_output()

| void spi_disable_ss_output | ( | uint32_t | spi | ) |

SPI Set the NSS Pin as an Input.

In master mode this allows the master to sense the presence of other masters. If NSS is then pulled low the master is placed into slave mode. In slave mode NSS becomes a slave enable.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 599 of file spi_common_all.c.

References SPI_CR2.

◆ spi_disable_tx_buffer_empty_interrupt()

| void spi_disable_tx_buffer_empty_interrupt | ( | uint32_t | spi | ) |

SPI Disable the Transmit Buffer Empty Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 526 of file spi_common_all.c.

References SPI_CR2.

◆ spi_disable_tx_dma()

| void spi_disable_tx_dma | ( | uint32_t | spi | ) |

SPI Disable Transmit Transfers via DMA.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 625 of file spi_common_all.c.

References SPI_CR2.

◆ spi_enable()

| void spi_enable | ( | uint32_t | spi | ) |

SPI Enable.

The SPI peripheral is enabled.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 70 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_SPE.

◆ spi_enable_crc()

| void spi_enable_crc | ( | uint32_t | spi | ) |

SPI Enable the CRC.

The SPI peripheral is set to use a CRC field for transmit and receive.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 265 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_CRCEN.

◆ spi_enable_error_interrupt()

| void spi_enable_error_interrupt | ( | uint32_t | spi | ) |

SPI Enable the Error Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 559 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_ERRIE.

◆ spi_enable_rx_buffer_not_empty_interrupt()

| void spi_enable_rx_buffer_not_empty_interrupt | ( | uint32_t | spi | ) |

SPI Enable the Receive Buffer Ready Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 537 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_RXNEIE.

◆ spi_enable_rx_dma()

| void spi_enable_rx_dma | ( | uint32_t | spi | ) |

SPI Enable Receive Transfers via DMA.

This allows received data streams to proceed unattended using DMA to move data from the receive buffer as data becomes available. The DMA channels provided for each SPI peripheral are given in the Technical Manual DMA section.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 640 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_RXDMAEN.

◆ spi_enable_software_slave_management()

| void spi_enable_software_slave_management | ( | uint32_t | spi | ) |

SPI Enable Slave Management by Software.

In slave mode the NSS hardware input is replaced by an internal software enable/disable of the slave (spi_set_nss_high).

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 356 of file spi_common_all.c.

References SPI_CR1, SPI_CR1_SSM, and SPI_CR2.

◆ spi_enable_ss_output()

| void spi_enable_ss_output | ( | uint32_t | spi | ) |

SPI Set the NSS Pin as an Output.

Normally used in master mode to allows the master to place all devices on the SPI bus into slave mode. Multimaster mode is not possible.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 584 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_SSOE.

◆ spi_enable_tx_buffer_empty_interrupt()

| void spi_enable_tx_buffer_empty_interrupt | ( | uint32_t | spi | ) |

SPI Enable the Transmit Buffer Empty Interrupt.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 515 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_TXEIE.

◆ spi_enable_tx_dma()

| void spi_enable_tx_dma | ( | uint32_t | spi | ) |

SPI Enable Transmit Transfers via DMA.

This allows transmissions to proceed unattended using DMA to move data to the transmit buffer as it becomes available. The DMA channels provided for each SPI peripheral are given in the Technical Manual DMA section.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 614 of file spi_common_all.c.

References SPI_CR2, and SPI_CR2_TXDMAEN.

◆ spi_fifo_reception_threshold_16bit()

| void spi_fifo_reception_threshold_16bit | ( | uint32_t | spi | ) |

SPI Set reception threshold to 16 bits.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 164 of file spi_common_v2.c.

References SPI_CR2.

◆ spi_fifo_reception_threshold_8bit()

| void spi_fifo_reception_threshold_8bit | ( | uint32_t | spi | ) |

SPI Set reception threshold to 8 bits.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 153 of file spi_common_v2.c.

References SPI_CR2, and SPI_CR2_FRXTH.

◆ spi_i2s_mode_spi_mode()

| void spi_i2s_mode_spi_mode | ( | uint32_t | spi | ) |

◆ spi_init_master()

| int spi_init_master | ( | uint32_t | spi, |

| uint32_t | br, | ||

| uint32_t | cpol, | ||

| uint32_t | cpha, | ||

| uint32_t | lsbfirst | ||

| ) |

Configure the SPI as Master.

The SPI peripheral is configured as a master with communication parameters baudrate, frame format lsb/msb first, clock polarity and phase. The SPI enable, CRC enable, CRC next CRC length controls are not affected. These must be controlled separately.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] br Unsigned int32. Baudrate SPI peripheral baud rates. [in] cpol Unsigned int32. Clock polarity SPI clock polarity. [in] cpha Unsigned int32. Clock Phase SPI clock phase. [in] lsbfirst Unsigned int32. Frame format lsb/msb first SPI lsb/msb first.

- Returns

- int. Error code.

Definition at line 76 of file spi_common_v2.c.

References SPI_CR1, SPI_CR1_CRCEN, SPI_CR1_CRCL, SPI_CR1_CRCNEXT, SPI_CR1_MSTR, SPI_CR1_SPE, SPI_CR2, and SPI_CR2_SSOE.

◆ spi_read()

| uint16_t spi_read | ( | uint32_t | spi | ) |

SPI Data Read.

Data is read from the SPI interface after the incoming transfer has finished.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- Returns

- data Unsigned int16. 8 or 16 bit data.

Definition at line 165 of file spi_common_all.c.

References SPI_DR, SPI_SR, and SPI_SR_RXNE.

◆ spi_read8()

| uint8_t spi_read8 | ( | uint32_t | spi | ) |

Definition at line 105 of file spi_common_v2.c.

References SPI_DR8, SPI_SR, and SPI_SR_RXNE.

◆ spi_send()

| void spi_send | ( | uint32_t | spi, |

| uint16_t | data | ||

| ) |

SPI Data Write with Blocking.

Data is written to the SPI interface after the previous write transfer has finished.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] data Unsigned int16. 8 or 16 bit data to be written.

Definition at line 147 of file spi_common_all.c.

References SPI_DR, SPI_SR, and SPI_SR_TXE.

◆ spi_send8()

| void spi_send8 | ( | uint32_t | spi, |

| uint8_t | data | ||

| ) |

Definition at line 97 of file spi_common_v2.c.

References SPI_DR8, SPI_SR, and SPI_SR_TXE.

◆ spi_send_lsb_first()

| void spi_send_lsb_first | ( | uint32_t | spi | ) |

SPI Set to Send LSB First.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 400 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_LSBFIRST.

◆ spi_send_msb_first()

| void spi_send_msb_first | ( | uint32_t | spi | ) |

SPI Set to Send MSB First.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 411 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_baudrate_prescaler()

| void spi_set_baudrate_prescaler | ( | uint32_t | spi, |

| uint8_t | baudrate | ||

| ) |

SPI Set the Baudrate Prescaler.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] baudrate Unsigned int8. Baudrate prescale value SPI peripheral baud rate prescale values.

Definition at line 426 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_bidirectional_mode()

| void spi_set_bidirectional_mode | ( | uint32_t | spi | ) |

SPI Set Bidirectional Simplex Mode.

The SPI peripheral is set for bidirectional transfers in two-wire simplex mode (using a clock wire and a bidirectional data wire).

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 205 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_BIDIMODE.

◆ spi_set_bidirectional_receive_only_mode()

| void spi_set_bidirectional_receive_only_mode | ( | uint32_t | spi | ) |

SPI Set Bidirectional Simplex Receive Only Mode.

The SPI peripheral is set for bidirectional transfers in two-wire simplex mode (using a clock wire and a bidirectional data wire), and is placed in a receive state.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 235 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_BIDIMODE.

◆ spi_set_bidirectional_transmit_only_mode()

| void spi_set_bidirectional_transmit_only_mode | ( | uint32_t | spi | ) |

SPI Set Bidirectional Simplex Receive Only Mode.

The SPI peripheral is set for bidirectional transfers in two-wire simplex mode (using a clock wire and a bidirectional data wire), and is placed in a transmit state.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 251 of file spi_common_all.c.

References SPI_CR1, SPI_CR1_BIDIMODE, and SPI_CR1_BIDIOE.

◆ spi_set_clock_phase_0()

| void spi_set_clock_phase_0 | ( | uint32_t | spi | ) |

SPI Set the Clock Phase to Capture on Leading Edge.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- See also

- spi_set_clock_phase_1

Definition at line 504 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_clock_phase_1()

| void spi_set_clock_phase_1 | ( | uint32_t | spi | ) |

SPI Set the Clock Phase to Capture on Trailing Edge.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- See also

- spi_set_clock_phase_0

Definition at line 492 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_CPHA.

◆ spi_set_clock_polarity_0()

| void spi_set_clock_polarity_0 | ( | uint32_t | spi | ) |

SPI Set the Clock Polarity to Low when Idle.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- See also

- spi_set_clock_polarity_1

Definition at line 480 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_clock_polarity_1()

| void spi_set_clock_polarity_1 | ( | uint32_t | spi | ) |

SPI Set the Clock Polarity to High when Idle.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

- See also

- spi_set_clock_polarity_0

Definition at line 468 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_CPOL.

◆ spi_set_crcl_16bit()

| void spi_set_crcl_16bit | ( | uint32_t | spi | ) |

SPI Set CRC length to 16 bits.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 130 of file spi_common_v2.c.

References SPI_CR1, and SPI_CR1_CRCL.

◆ spi_set_crcl_8bit()

| void spi_set_crcl_8bit | ( | uint32_t | spi | ) |

SPI Set CRC length to 8 bits.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 119 of file spi_common_v2.c.

References SPI_CR1.

◆ spi_set_data_size()

| void spi_set_data_size | ( | uint32_t | spi, |

| uint16_t | data_s | ||

| ) |

SPI Set data size.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] data_s Unsigned int16. data size SPI data size.

Definition at line 141 of file spi_common_v2.c.

References SPI_CR2, and SPI_CR2_DS_MASK.

◆ spi_set_full_duplex_mode()

| void spi_set_full_duplex_mode | ( | uint32_t | spi | ) |

SPI Set Full Duplex (3-wire) Mode.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 317 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_master_mode()

| void spi_set_master_mode | ( | uint32_t | spi | ) |

SPI Set to Master Mode.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 445 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_MSTR.

◆ spi_set_next_tx_from_buffer()

| void spi_set_next_tx_from_buffer | ( | uint32_t | spi | ) |

SPI Next Transmit is a Data Word.

The next transmission to take place is a data word from the transmit buffer. This must be called before transmission to distinguish between sending of a data or CRC word.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 291 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_next_tx_from_crc()

| void spi_set_next_tx_from_crc | ( | uint32_t | spi | ) |

SPI Next Transmit is a CRC Word.

The next transmission to take place is a crc word from the hardware crc unit. This must be called before transmission to distinguish between sending of a data or CRC word.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 306 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_CRCNEXT.

◆ spi_set_nss_high()

| void spi_set_nss_high | ( | uint32_t | spi | ) |

SPI Set the Software NSS Signal High.

In slave mode, and only when software slave management is used, this replaces the NSS signal with a slave select enable signal.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 375 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_SSI.

◆ spi_set_nss_low()

| void spi_set_nss_low | ( | uint32_t | spi | ) |

SPI Set the Software NSS Signal Low.

In slave mode, and only when software slave management is used, this replaces the NSS signal with a slave select disable signal.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 389 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_receive_only_mode()

| void spi_set_receive_only_mode | ( | uint32_t | spi | ) |

SPI Set Receive Only Mode for Simplex (2-wire) Unidirectional Transfers.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 329 of file spi_common_all.c.

References SPI_CR1, and SPI_CR1_RXONLY.

◆ spi_set_slave_mode()

| void spi_set_slave_mode | ( | uint32_t | spi | ) |

SPI Set to Slave Mode.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 456 of file spi_common_all.c.

References SPI_CR1.

◆ spi_set_standard_mode()

| void spi_set_standard_mode | ( | uint32_t | spi, |

| uint8_t | mode | ||

| ) |

SPI Standard Mode selection.

Set SPI standard Modes

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] mode Unsigned int8. Standard SPI mode (0, 1, 2, 3)

- See also

- spi_set_clock_phase_0 spi_set_clock_phase_1

- spi_set_clock_polarity_0 spi_set_clock_polarity_1

Definition at line 671 of file spi_common_all.c.

References SPI_CR1, SPI_CR1_CPHA, and SPI_CR1_CPOL.

◆ spi_set_unidirectional_mode()

| void spi_set_unidirectional_mode | ( | uint32_t | spi | ) |

SPI Set Unidirectional Mode.

The SPI peripheral is set for unidirectional transfers. This is used in full duplex mode or when the SPI is placed in two-wire simplex mode that uses a clock wire and a unidirectional data wire.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address.

Definition at line 220 of file spi_common_all.c.

References SPI_CR1.

◆ spi_write()

| void spi_write | ( | uint32_t | spi, |

| uint16_t | data | ||

| ) |

SPI Data Write.

Data is written to the SPI interface.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] data Unsigned int16. 8 or 16 bit data to be written.

Definition at line 131 of file spi_common_all.c.

References SPI_DR.

Referenced by spi_xfer().

◆ spi_xfer()

| uint16_t spi_xfer | ( | uint32_t | spi, |

| uint16_t | data | ||

| ) |

SPI Data Write and Read Exchange.

Data is written to the SPI interface, then a read is done after the incoming transfer has finished.

- Parameters

-

[in] spi Unsigned int32. SPI peripheral identifier SPI Register base address. [in] data Unsigned int16. 8 or 16 bit data to be written.

- Returns

- data Unsigned int16. 8 or 16 bit data.

Definition at line 185 of file spi_common_all.c.

References SPI_DR, SPI_SR, SPI_SR_RXNE, and spi_write().