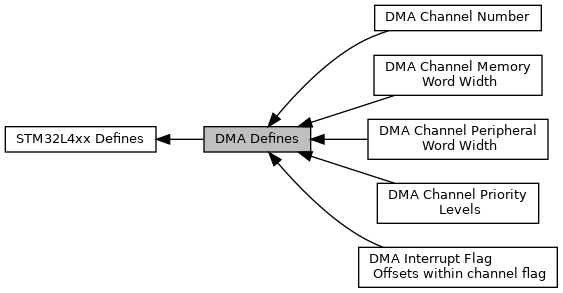

Defined Constants and Types for the STM32L4xx DMA Controller. More...

Modules | |

| DMA Interrupt Flag Offsets within channel flag | |

| group. | |

| DMA Channel Priority Levels | |

| DMA Channel Memory Word Width | |

| DMA Channel Peripheral Word Width | |

| DMA Channel Number | |

Functions | |

| void | dma_set_channel_request (uint32_t dma, uint8_t channel, uint8_t request) |

| DMA Channel Set Request Selection. More... | |

| void | dma_channel_reset (uint32_t dma, uint8_t channel) |

| DMA Channel Reset. More... | |

| void | dma_clear_interrupt_flags (uint32_t dma, uint8_t channel, uint32_t interrupts) |

| DMA Channel Clear Interrupt Flag. More... | |

| bool | dma_get_interrupt_flag (uint32_t dma, uint8_t channel, uint32_t interrupts) |

| DMA Channel Read Interrupt Flag. More... | |

| void | dma_enable_mem2mem_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Memory to Memory Transfers. More... | |

| void | dma_set_priority (uint32_t dma, uint8_t channel, uint32_t prio) |

| DMA Channel Set Priority. More... | |

| void | dma_set_memory_size (uint32_t dma, uint8_t channel, uint32_t mem_size) |

| DMA Channel Set Memory Word Width. More... | |

| void | dma_set_peripheral_size (uint32_t dma, uint8_t channel, uint32_t peripheral_size) |

| DMA Channel Set Peripheral Word Width. More... | |

| void | dma_enable_memory_increment_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Memory Increment after Transfer. More... | |

| void | dma_disable_memory_increment_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Disable Memory Increment after Transfer. More... | |

| void | dma_enable_peripheral_increment_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Peripheral Increment after Transfer. More... | |

| void | dma_disable_peripheral_increment_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Disable Peripheral Increment after Transfer. More... | |

| void | dma_enable_circular_mode (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Memory Circular Mode. More... | |

| void | dma_set_read_from_peripheral (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Transfers from a Peripheral. More... | |

| void | dma_set_read_from_memory (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Transfers from Memory. More... | |

| void | dma_enable_transfer_error_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Interrupt on Transfer Error. More... | |

| void | dma_disable_transfer_error_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Disable Interrupt on Transfer Error. More... | |

| void | dma_enable_half_transfer_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Interrupt on Transfer Half Complete. More... | |

| void | dma_disable_half_transfer_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Disable Interrupt on Transfer Half Complete. More... | |

| void | dma_enable_transfer_complete_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Enable Interrupt on Transfer Complete. More... | |

| void | dma_disable_transfer_complete_interrupt (uint32_t dma, uint8_t channel) |

| DMA Channel Disable Interrupt on Transfer Complete. More... | |

| void | dma_enable_channel (uint32_t dma, uint8_t channel) |

| DMA Channel Enable. More... | |

| void | dma_disable_channel (uint32_t dma, uint8_t channel) |

| DMA Channel Disable. More... | |

| void | dma_set_peripheral_address (uint32_t dma, uint8_t channel, uint32_t address) |

| DMA Channel Set the Peripheral Address. More... | |

| void | dma_set_memory_address (uint32_t dma, uint8_t channel, uint32_t address) |

| DMA Channel Set the Base Memory Address. More... | |

| uint16_t | dma_get_number_of_data (uint32_t dma, uint8_t channel) |

| DMA Channel Get the Transfer Block Size. More... | |

| void | dma_set_number_of_data (uint32_t dma, uint8_t channel, uint16_t number) |

| DMA Channel Set the Transfer Block Size. More... | |

Detailed Description

Defined Constants and Types for the STM32L4xx DMA Controller.

- Version

- 1.0.0

- Date

- 15 December 2017

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ DMA1

| #define DMA1 DMA1_BASE |

Definition at line 45 of file dma_common_l1f013.h.

◆ DMA1_CCR

Definition at line 64 of file dma_common_l1f013.h.

◆ DMA1_CCR1

| #define DMA1_CCR1 DMA1_CCR(DMA_CHANNEL1) |

Definition at line 65 of file dma_common_l1f013.h.

◆ DMA1_CCR2

| #define DMA1_CCR2 DMA1_CCR(DMA_CHANNEL2) |

Definition at line 66 of file dma_common_l1f013.h.

◆ DMA1_CCR3

| #define DMA1_CCR3 DMA1_CCR(DMA_CHANNEL3) |

Definition at line 67 of file dma_common_l1f013.h.

◆ DMA1_CCR4

| #define DMA1_CCR4 DMA1_CCR(DMA_CHANNEL4) |

Definition at line 68 of file dma_common_l1f013.h.

◆ DMA1_CCR5

| #define DMA1_CCR5 DMA1_CCR(DMA_CHANNEL5) |

Definition at line 69 of file dma_common_l1f013.h.

◆ DMA1_CCR6

| #define DMA1_CCR6 DMA1_CCR(DMA_CHANNEL6) |

Definition at line 70 of file dma_common_l1f013.h.

◆ DMA1_CCR7

| #define DMA1_CCR7 DMA1_CCR(DMA_CHANNEL7) |

Definition at line 71 of file dma_common_l1f013.h.

◆ DMA1_CMAR

Definition at line 125 of file dma_common_l1f013.h.

◆ DMA1_CMAR1

| #define DMA1_CMAR1 DMA1_CMAR(DMA_CHANNEL1) |

Definition at line 126 of file dma_common_l1f013.h.

◆ DMA1_CMAR2

| #define DMA1_CMAR2 DMA1_CMAR(DMA_CHANNEL2) |

Definition at line 127 of file dma_common_l1f013.h.

◆ DMA1_CMAR3

| #define DMA1_CMAR3 DMA1_CMAR(DMA_CHANNEL3) |

Definition at line 128 of file dma_common_l1f013.h.

◆ DMA1_CMAR4

| #define DMA1_CMAR4 DMA1_CMAR(DMA_CHANNEL4) |

Definition at line 129 of file dma_common_l1f013.h.

◆ DMA1_CMAR5

| #define DMA1_CMAR5 DMA1_CMAR(DMA_CHANNEL5) |

Definition at line 130 of file dma_common_l1f013.h.

◆ DMA1_CMAR6

| #define DMA1_CMAR6 DMA1_CMAR(DMA_CHANNEL6) |

Definition at line 131 of file dma_common_l1f013.h.

◆ DMA1_CMAR7

| #define DMA1_CMAR7 DMA1_CMAR(DMA_CHANNEL7) |

Definition at line 132 of file dma_common_l1f013.h.

◆ DMA1_CNDTR

Definition at line 84 of file dma_common_l1f013.h.

◆ DMA1_CNDTR1

| #define DMA1_CNDTR1 DMA1_CNDTR(DMA_CHANNEL1) |

Definition at line 85 of file dma_common_l1f013.h.

◆ DMA1_CNDTR2

| #define DMA1_CNDTR2 DMA1_CNDTR(DMA_CHANNEL2) |

Definition at line 86 of file dma_common_l1f013.h.

◆ DMA1_CNDTR3

| #define DMA1_CNDTR3 DMA1_CNDTR(DMA_CHANNEL3) |

Definition at line 87 of file dma_common_l1f013.h.

◆ DMA1_CNDTR4

| #define DMA1_CNDTR4 DMA1_CNDTR(DMA_CHANNEL4) |

Definition at line 88 of file dma_common_l1f013.h.

◆ DMA1_CNDTR5

| #define DMA1_CNDTR5 DMA1_CNDTR(DMA_CHANNEL5) |

Definition at line 89 of file dma_common_l1f013.h.

◆ DMA1_CNDTR6

| #define DMA1_CNDTR6 DMA1_CNDTR(DMA_CHANNEL6) |

Definition at line 90 of file dma_common_l1f013.h.

◆ DMA1_CNDTR7

| #define DMA1_CNDTR7 DMA1_CNDTR(DMA_CHANNEL7) |

Definition at line 91 of file dma_common_l1f013.h.

◆ DMA1_CPAR

Definition at line 104 of file dma_common_l1f013.h.

◆ DMA1_CPAR1

| #define DMA1_CPAR1 DMA1_CPAR(DMA_CHANNEL1) |

Definition at line 105 of file dma_common_l1f013.h.

◆ DMA1_CPAR2

| #define DMA1_CPAR2 DMA1_CPAR(DMA_CHANNEL2) |

Definition at line 106 of file dma_common_l1f013.h.

◆ DMA1_CPAR3

| #define DMA1_CPAR3 DMA1_CPAR(DMA_CHANNEL3) |

Definition at line 107 of file dma_common_l1f013.h.

◆ DMA1_CPAR4

| #define DMA1_CPAR4 DMA1_CPAR(DMA_CHANNEL4) |

Definition at line 108 of file dma_common_l1f013.h.

◆ DMA1_CPAR5

| #define DMA1_CPAR5 DMA1_CPAR(DMA_CHANNEL5) |

Definition at line 109 of file dma_common_l1f013.h.

◆ DMA1_CPAR6

| #define DMA1_CPAR6 DMA1_CPAR(DMA_CHANNEL6) |

Definition at line 110 of file dma_common_l1f013.h.

◆ DMA1_CPAR7

| #define DMA1_CPAR7 DMA1_CPAR(DMA_CHANNEL7) |

Definition at line 111 of file dma_common_l1f013.h.

◆ DMA1_CSELR

Definition at line 34 of file dma_common_csel.h.

◆ DMA1_IFCR

Definition at line 57 of file dma_common_l1f013.h.

◆ DMA1_ISR

Definition at line 52 of file dma_common_l1f013.h.

◆ DMA2

| #define DMA2 DMA2_BASE |

Definition at line 46 of file dma_common_l1f013.h.

◆ DMA2_CCR

Definition at line 73 of file dma_common_l1f013.h.

◆ DMA2_CCR1

| #define DMA2_CCR1 DMA2_CCR(DMA_CHANNEL1) |

Definition at line 74 of file dma_common_l1f013.h.

◆ DMA2_CCR2

| #define DMA2_CCR2 DMA2_CCR(DMA_CHANNEL2) |

Definition at line 75 of file dma_common_l1f013.h.

◆ DMA2_CCR3

| #define DMA2_CCR3 DMA2_CCR(DMA_CHANNEL3) |

Definition at line 76 of file dma_common_l1f013.h.

◆ DMA2_CCR4

| #define DMA2_CCR4 DMA2_CCR(DMA_CHANNEL4) |

Definition at line 77 of file dma_common_l1f013.h.

◆ DMA2_CCR5

| #define DMA2_CCR5 DMA2_CCR(DMA_CHANNEL5) |

Definition at line 78 of file dma_common_l1f013.h.

◆ DMA2_CMAR

Definition at line 134 of file dma_common_l1f013.h.

◆ DMA2_CMAR1

| #define DMA2_CMAR1 DMA2_CMAR(DMA_CHANNEL1) |

Definition at line 135 of file dma_common_l1f013.h.

◆ DMA2_CMAR2

| #define DMA2_CMAR2 DMA2_CMAR(DMA_CHANNEL2) |

Definition at line 136 of file dma_common_l1f013.h.

◆ DMA2_CMAR3

| #define DMA2_CMAR3 DMA2_CMAR(DMA_CHANNEL3) |

Definition at line 137 of file dma_common_l1f013.h.

◆ DMA2_CMAR4

| #define DMA2_CMAR4 DMA2_CMAR(DMA_CHANNEL4) |

Definition at line 138 of file dma_common_l1f013.h.

◆ DMA2_CMAR5

| #define DMA2_CMAR5 DMA2_CMAR(DMA_CHANNEL5) |

Definition at line 139 of file dma_common_l1f013.h.

◆ DMA2_CNDTR

Definition at line 93 of file dma_common_l1f013.h.

◆ DMA2_CNDTR1

| #define DMA2_CNDTR1 DMA2_CNDTR(DMA_CHANNEL1) |

Definition at line 94 of file dma_common_l1f013.h.

◆ DMA2_CNDTR2

| #define DMA2_CNDTR2 DMA2_CNDTR(DMA_CHANNEL2) |

Definition at line 95 of file dma_common_l1f013.h.

◆ DMA2_CNDTR3

| #define DMA2_CNDTR3 DMA2_CNDTR(DMA_CHANNEL3) |

Definition at line 96 of file dma_common_l1f013.h.

◆ DMA2_CNDTR4

| #define DMA2_CNDTR4 DMA2_CNDTR(DMA_CHANNEL4) |

Definition at line 97 of file dma_common_l1f013.h.

◆ DMA2_CNDTR5

| #define DMA2_CNDTR5 DMA2_CNDTR(DMA_CHANNEL5) |

Definition at line 98 of file dma_common_l1f013.h.

◆ DMA2_CPAR

Definition at line 113 of file dma_common_l1f013.h.

◆ DMA2_CPAR1

| #define DMA2_CPAR1 DMA2_CPAR(DMA_CHANNEL1) |

Definition at line 114 of file dma_common_l1f013.h.

◆ DMA2_CPAR2

| #define DMA2_CPAR2 DMA2_CPAR(DMA_CHANNEL2) |

Definition at line 115 of file dma_common_l1f013.h.

◆ DMA2_CPAR3

| #define DMA2_CPAR3 DMA2_CPAR(DMA_CHANNEL3) |

Definition at line 116 of file dma_common_l1f013.h.

◆ DMA2_CPAR4

| #define DMA2_CPAR4 DMA2_CPAR(DMA_CHANNEL4) |

Definition at line 117 of file dma_common_l1f013.h.

◆ DMA2_CPAR5

| #define DMA2_CPAR5 DMA2_CPAR(DMA_CHANNEL5) |

Definition at line 118 of file dma_common_l1f013.h.

◆ DMA2_CSELR

Definition at line 35 of file dma_common_csel.h.

◆ DMA2_IFCR

Definition at line 58 of file dma_common_l1f013.h.

◆ DMA2_ISR

Definition at line 53 of file dma_common_l1f013.h.

◆ DMA_CCR

| #define DMA_CCR | ( | dma_base, | |

| channel | |||

| ) |

Definition at line 61 of file dma_common_l1f013.h.

◆ DMA_CCR_CIRC

| #define DMA_CCR_CIRC (1 << 5) |

Definition at line 338 of file dma_common_l1f013.h.

◆ DMA_CCR_DIR

| #define DMA_CCR_DIR (1 << 4) |

Definition at line 341 of file dma_common_l1f013.h.

◆ DMA_CCR_EN

| #define DMA_CCR_EN (1 << 0) |

Definition at line 353 of file dma_common_l1f013.h.

◆ DMA_CCR_HTIE

| #define DMA_CCR_HTIE (1 << 2) |

Definition at line 347 of file dma_common_l1f013.h.

◆ DMA_CCR_MEM2MEM

| #define DMA_CCR_MEM2MEM (1 << 14) |

Definition at line 292 of file dma_common_l1f013.h.

◆ DMA_CCR_MINC

| #define DMA_CCR_MINC (1 << 7) |

Definition at line 332 of file dma_common_l1f013.h.

◆ DMA_CCR_MSIZE_MASK

| #define DMA_CCR_MSIZE_MASK (0x3 << 10) |

Definition at line 316 of file dma_common_l1f013.h.

◆ DMA_CCR_MSIZE_SHIFT

| #define DMA_CCR_MSIZE_SHIFT 10 |

Definition at line 317 of file dma_common_l1f013.h.

◆ DMA_CCR_PINC

| #define DMA_CCR_PINC (1 << 6) |

Definition at line 335 of file dma_common_l1f013.h.

◆ DMA_CCR_PL_MASK

| #define DMA_CCR_PL_MASK (0x3 << 12) |

Definition at line 304 of file dma_common_l1f013.h.

◆ DMA_CCR_PL_SHIFT

| #define DMA_CCR_PL_SHIFT 12 |

Definition at line 305 of file dma_common_l1f013.h.

◆ DMA_CCR_PSIZE_MASK

| #define DMA_CCR_PSIZE_MASK (0x3 << 8) |

Definition at line 328 of file dma_common_l1f013.h.

◆ DMA_CCR_PSIZE_SHIFT

| #define DMA_CCR_PSIZE_SHIFT 8 |

Definition at line 329 of file dma_common_l1f013.h.

◆ DMA_CCR_TCIE

| #define DMA_CCR_TCIE (1 << 1) |

Definition at line 350 of file dma_common_l1f013.h.

◆ DMA_CCR_TEIE

| #define DMA_CCR_TEIE (1 << 3) |

Definition at line 344 of file dma_common_l1f013.h.

◆ DMA_CMAR

| #define DMA_CMAR | ( | dma_base, | |

| channel | |||

| ) |

Definition at line 122 of file dma_common_l1f013.h.

◆ DMA_CNDTR

| #define DMA_CNDTR | ( | dma_base, | |

| channel | |||

| ) |

Definition at line 81 of file dma_common_l1f013.h.

◆ DMA_CPAR

| #define DMA_CPAR | ( | dma_base, | |

| channel | |||

| ) |

Definition at line 101 of file dma_common_l1f013.h.

◆ DMA_CSELR

| #define DMA_CSELR | ( | dma_base | ) | MMIO32((dma_base) + 0xA8) |

Definition at line 33 of file dma_common_csel.h.

◆ DMA_CSELR_CxS_MASK

| #define DMA_CSELR_CxS_MASK (0x0f) |

Definition at line 40 of file dma_common_csel.h.

◆ DMA_CSELR_CxS_SHIFT

| #define DMA_CSELR_CxS_SHIFT | ( | channel | ) | (4 * ((channel) - 1)) |

Definition at line 39 of file dma_common_csel.h.

◆ DMA_FLAG_OFFSET

| #define DMA_FLAG_OFFSET | ( | channel | ) | (4*((channel) - 1)) |

Definition at line 165 of file dma_common_l1f013.h.

◆ DMA_FLAGS

| #define DMA_FLAGS |

Definition at line 166 of file dma_common_l1f013.h.

◆ DMA_IFCR

| #define DMA_IFCR | ( | dma_base | ) | MMIO32((dma_base) + 0x04) |

Definition at line 56 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF

| #define DMA_IFCR_CGIF | ( | channel | ) |

Definition at line 265 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF1

| #define DMA_IFCR_CGIF1 DMA_IFCR_CGIF(DMA_CHANNEL1) |

Definition at line 268 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF2

| #define DMA_IFCR_CGIF2 DMA_IFCR_CGIF(DMA_CHANNEL2) |

Definition at line 269 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF3

| #define DMA_IFCR_CGIF3 DMA_IFCR_CGIF(DMA_CHANNEL3) |

Definition at line 270 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF4

| #define DMA_IFCR_CGIF4 DMA_IFCR_CGIF(DMA_CHANNEL4) |

Definition at line 271 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF5

| #define DMA_IFCR_CGIF5 DMA_IFCR_CGIF(DMA_CHANNEL5) |

Definition at line 272 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF6

| #define DMA_IFCR_CGIF6 DMA_IFCR_CGIF(DMA_CHANNEL6) |

Definition at line 273 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF7

| #define DMA_IFCR_CGIF7 DMA_IFCR_CGIF(DMA_CHANNEL7) |

Definition at line 274 of file dma_common_l1f013.h.

◆ DMA_IFCR_CGIF_BIT

| #define DMA_IFCR_CGIF_BIT DMA_GIF |

Definition at line 264 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF

| #define DMA_IFCR_CHTIF | ( | channel | ) |

Definition at line 239 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF1

| #define DMA_IFCR_CHTIF1 DMA_IFCR_CHTIF(DMA_CHANNEL1) |

Definition at line 242 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF2

| #define DMA_IFCR_CHTIF2 DMA_IFCR_CHTIF(DMA_CHANNEL2) |

Definition at line 243 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF3

| #define DMA_IFCR_CHTIF3 DMA_IFCR_CHTIF(DMA_CHANNEL3) |

Definition at line 244 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF4

| #define DMA_IFCR_CHTIF4 DMA_IFCR_CHTIF(DMA_CHANNEL4) |

Definition at line 245 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF5

| #define DMA_IFCR_CHTIF5 DMA_IFCR_CHTIF(DMA_CHANNEL5) |

Definition at line 246 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF6

| #define DMA_IFCR_CHTIF6 DMA_IFCR_CHTIF(DMA_CHANNEL6) |

Definition at line 247 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF7

| #define DMA_IFCR_CHTIF7 DMA_IFCR_CHTIF(DMA_CHANNEL7) |

Definition at line 248 of file dma_common_l1f013.h.

◆ DMA_IFCR_CHTIF_BIT

| #define DMA_IFCR_CHTIF_BIT DMA_HTIF |

Definition at line 238 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF

| #define DMA_IFCR_CIF | ( | channel | ) |

Definition at line 278 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF1

| #define DMA_IFCR_CIF1 DMA_IFCR_CIF(DMA_CHANNEL1) |

Definition at line 281 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF2

| #define DMA_IFCR_CIF2 DMA_IFCR_CIF(DMA_CHANNEL2) |

Definition at line 282 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF3

| #define DMA_IFCR_CIF3 DMA_IFCR_CIF(DMA_CHANNEL3) |

Definition at line 283 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF4

| #define DMA_IFCR_CIF4 DMA_IFCR_CIF(DMA_CHANNEL4) |

Definition at line 284 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF5

| #define DMA_IFCR_CIF5 DMA_IFCR_CIF(DMA_CHANNEL5) |

Definition at line 285 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF6

| #define DMA_IFCR_CIF6 DMA_IFCR_CIF(DMA_CHANNEL6) |

Definition at line 286 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF7

| #define DMA_IFCR_CIF7 DMA_IFCR_CIF(DMA_CHANNEL7) |

Definition at line 287 of file dma_common_l1f013.h.

◆ DMA_IFCR_CIF_BIT

| #define DMA_IFCR_CIF_BIT 0xF |

Definition at line 277 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF

| #define DMA_IFCR_CTCIF | ( | channel | ) |

Definition at line 252 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF1

| #define DMA_IFCR_CTCIF1 DMA_IFCR_CTCIF(DMA_CHANNEL1) |

Definition at line 255 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF2

| #define DMA_IFCR_CTCIF2 DMA_IFCR_CTCIF(DMA_CHANNEL2) |

Definition at line 256 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF3

| #define DMA_IFCR_CTCIF3 DMA_IFCR_CTCIF(DMA_CHANNEL3) |

Definition at line 257 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF4

| #define DMA_IFCR_CTCIF4 DMA_IFCR_CTCIF(DMA_CHANNEL4) |

Definition at line 258 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF5

| #define DMA_IFCR_CTCIF5 DMA_IFCR_CTCIF(DMA_CHANNEL5) |

Definition at line 259 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF6

| #define DMA_IFCR_CTCIF6 DMA_IFCR_CTCIF(DMA_CHANNEL6) |

Definition at line 260 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF7

| #define DMA_IFCR_CTCIF7 DMA_IFCR_CTCIF(DMA_CHANNEL7) |

Definition at line 261 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTCIF_BIT

| #define DMA_IFCR_CTCIF_BIT DMA_TCIF |

Definition at line 251 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF

| #define DMA_IFCR_CTEIF | ( | channel | ) |

Definition at line 226 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF1

| #define DMA_IFCR_CTEIF1 DMA_IFCR_CTEIF(DMA_CHANNEL1) |

Definition at line 229 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF2

| #define DMA_IFCR_CTEIF2 DMA_IFCR_CTEIF(DMA_CHANNEL2) |

Definition at line 230 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF3

| #define DMA_IFCR_CTEIF3 DMA_IFCR_CTEIF(DMA_CHANNEL3) |

Definition at line 231 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF4

| #define DMA_IFCR_CTEIF4 DMA_IFCR_CTEIF(DMA_CHANNEL4) |

Definition at line 232 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF5

| #define DMA_IFCR_CTEIF5 DMA_IFCR_CTEIF(DMA_CHANNEL5) |

Definition at line 233 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF6

| #define DMA_IFCR_CTEIF6 DMA_IFCR_CTEIF(DMA_CHANNEL6) |

Definition at line 234 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF7

| #define DMA_IFCR_CTEIF7 DMA_IFCR_CTEIF(DMA_CHANNEL7) |

Definition at line 235 of file dma_common_l1f013.h.

◆ DMA_IFCR_CTEIF_BIT

| #define DMA_IFCR_CTEIF_BIT DMA_TEIF |

Definition at line 225 of file dma_common_l1f013.h.

◆ DMA_ISR

| #define DMA_ISR | ( | dma_base | ) | MMIO32((dma_base) + 0x00) |

Definition at line 51 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF

| #define DMA_ISR_GIF | ( | channel | ) |

Definition at line 211 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF1

| #define DMA_ISR_GIF1 DMA_ISR_GIF(DMA_CHANNEL1) |

Definition at line 214 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF2

| #define DMA_ISR_GIF2 DMA_ISR_GIF(DMA_CHANNEL2) |

Definition at line 215 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF3

| #define DMA_ISR_GIF3 DMA_ISR_GIF(DMA_CHANNEL3) |

Definition at line 216 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF4

| #define DMA_ISR_GIF4 DMA_ISR_GIF(DMA_CHANNEL4) |

Definition at line 217 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF5

| #define DMA_ISR_GIF5 DMA_ISR_GIF(DMA_CHANNEL5) |

Definition at line 218 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF6

| #define DMA_ISR_GIF6 DMA_ISR_GIF(DMA_CHANNEL6) |

Definition at line 219 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF7

| #define DMA_ISR_GIF7 DMA_ISR_GIF(DMA_CHANNEL7) |

Definition at line 220 of file dma_common_l1f013.h.

◆ DMA_ISR_GIF_BIT

| #define DMA_ISR_GIF_BIT DMA_GIF |

Definition at line 210 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF

| #define DMA_ISR_HTIF | ( | channel | ) |

Definition at line 185 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF1

| #define DMA_ISR_HTIF1 DMA_ISR_HTIF(DMA_CHANNEL1) |

Definition at line 188 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF2

| #define DMA_ISR_HTIF2 DMA_ISR_HTIF(DMA_CHANNEL2) |

Definition at line 189 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF3

| #define DMA_ISR_HTIF3 DMA_ISR_HTIF(DMA_CHANNEL3) |

Definition at line 190 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF4

| #define DMA_ISR_HTIF4 DMA_ISR_HTIF(DMA_CHANNEL4) |

Definition at line 191 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF5

| #define DMA_ISR_HTIF5 DMA_ISR_HTIF(DMA_CHANNEL5) |

Definition at line 192 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF6

| #define DMA_ISR_HTIF6 DMA_ISR_HTIF(DMA_CHANNEL6) |

Definition at line 193 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF7

| #define DMA_ISR_HTIF7 DMA_ISR_HTIF(DMA_CHANNEL7) |

Definition at line 194 of file dma_common_l1f013.h.

◆ DMA_ISR_HTIF_BIT

| #define DMA_ISR_HTIF_BIT DMA_HTIF |

Definition at line 184 of file dma_common_l1f013.h.

◆ DMA_ISR_MASK

| #define DMA_ISR_MASK | ( | channel | ) | (DMA_FLAGS << DMA_FLAG_OFFSET(channel)) |

Definition at line 168 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF

| #define DMA_ISR_TCIF | ( | channel | ) |

Definition at line 198 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF1

| #define DMA_ISR_TCIF1 DMA_ISR_TCIF(DMA_CHANNEL1) |

Definition at line 201 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF2

| #define DMA_ISR_TCIF2 DMA_ISR_TCIF(DMA_CHANNEL2) |

Definition at line 202 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF3

| #define DMA_ISR_TCIF3 DMA_ISR_TCIF(DMA_CHANNEL3) |

Definition at line 203 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF4

| #define DMA_ISR_TCIF4 DMA_ISR_TCIF(DMA_CHANNEL4) |

Definition at line 204 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF5

| #define DMA_ISR_TCIF5 DMA_ISR_TCIF(DMA_CHANNEL5) |

Definition at line 205 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF6

| #define DMA_ISR_TCIF6 DMA_ISR_TCIF(DMA_CHANNEL6) |

Definition at line 206 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF7

| #define DMA_ISR_TCIF7 DMA_ISR_TCIF(DMA_CHANNEL7) |

Definition at line 207 of file dma_common_l1f013.h.

◆ DMA_ISR_TCIF_BIT

| #define DMA_ISR_TCIF_BIT DMA_TCIF |

Definition at line 197 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF

| #define DMA_ISR_TEIF | ( | channel | ) |

Definition at line 172 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF1

| #define DMA_ISR_TEIF1 DMA_ISR_TEIF(DMA_CHANNEL1) |

Definition at line 175 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF2

| #define DMA_ISR_TEIF2 DMA_ISR_TEIF(DMA_CHANNEL2) |

Definition at line 176 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF3

| #define DMA_ISR_TEIF3 DMA_ISR_TEIF(DMA_CHANNEL3) |

Definition at line 177 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF4

| #define DMA_ISR_TEIF4 DMA_ISR_TEIF(DMA_CHANNEL4) |

Definition at line 178 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF5

| #define DMA_ISR_TEIF5 DMA_ISR_TEIF(DMA_CHANNEL5) |

Definition at line 179 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF6

| #define DMA_ISR_TEIF6 DMA_ISR_TEIF(DMA_CHANNEL6) |

Definition at line 180 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF7

| #define DMA_ISR_TEIF7 DMA_ISR_TEIF(DMA_CHANNEL7) |

Definition at line 181 of file dma_common_l1f013.h.

◆ DMA_ISR_TEIF_BIT

| #define DMA_ISR_TEIF_BIT DMA_TEIF |

Definition at line 171 of file dma_common_l1f013.h.

Function Documentation

◆ dma_channel_reset()

| void dma_channel_reset | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Reset.

The channel is disabled and configuration registers are cleared.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 54 of file dma_common_l1f013.c.

References DMA_CCR, DMA_CMAR, DMA_CNDTR, DMA_CPAR, DMA_IFCR, and DMA_IFCR_CIF.

◆ dma_clear_interrupt_flags()

| void dma_clear_interrupt_flags | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | interrupts | ||

| ) |

DMA Channel Clear Interrupt Flag.

The interrupt flag for the channel is cleared. More than one interrupt for the same channel may be cleared by using the logical OR of the interrupt flags.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: DMA Channel Number [in] interrupts unsigned int32. Logical OR of interrupt numbers: DMA Interrupt Flag Offsets within channel flag

Definition at line 80 of file dma_common_l1f013.c.

References DMA_FLAG_OFFSET, and DMA_IFCR.

◆ dma_disable_channel()

| void dma_disable_channel | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable.

- Note

- The DMA channel registers retain their values when the channel is disabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 376 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_disable_half_transfer_interrupt()

| void dma_disable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 325 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_disable_memory_increment_mode()

| void dma_disable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable Memory Increment after Transfer.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 201 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_disable_peripheral_increment_mode()

| void dma_disable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable Peripheral Increment after Transfer.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 229 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_disable_transfer_complete_interrupt()

| void dma_disable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 349 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_disable_transfer_error_interrupt()

| void dma_disable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Disable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 301 of file dma_common_l1f013.c.

References DMA_CCR.

◆ dma_enable_channel()

| void dma_enable_channel | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 361 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_EN.

◆ dma_enable_circular_mode()

| void dma_enable_circular_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Memory Circular Mode.

After the number of bytes/words to be transferred has been completed, the original transfer block size, memory and peripheral base addresses are reloaded and the process repeats.

- Note

- This cannot be used with memory to memory mode, which is explicitly disabled here.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 248 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_CIRC.

◆ dma_enable_half_transfer_interrupt()

| void dma_enable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 313 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_HTIE.

◆ dma_enable_mem2mem_mode()

| void dma_enable_mem2mem_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Memory to Memory Transfers.

Memory to memory transfers do not require a trigger to activate each transfer. Transfers begin immediately the channel has been enabled, and proceed without intervention.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 117 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_MEM2MEM.

◆ dma_enable_memory_increment_mode()

| void dma_enable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Memory Increment after Transfer.

Following each transfer the current memory address is incremented by 1, 2 or 4 depending on the data size set in dma_set_memory_size. The value held by the base memory address register is unchanged.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 189 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_MINC.

◆ dma_enable_peripheral_increment_mode()

| void dma_enable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Peripheral Increment after Transfer.

Following each transfer the current peripheral address is incremented by 1, 2 or 4 depending on the data size set in dma_set_peripheral_size. The value held by the base peripheral address register is unchanged.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 217 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_PINC.

◆ dma_enable_transfer_complete_interrupt()

| void dma_enable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 337 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_TCIE.

◆ dma_enable_transfer_error_interrupt()

| void dma_enable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 289 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_TEIE.

◆ dma_get_interrupt_flag()

| bool dma_get_interrupt_flag | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | interrupt | ||

| ) |

DMA Channel Read Interrupt Flag.

The interrupt flag for the channel is returned.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: DMA Channel Number [in] interrupt unsigned int32. Interrupt number: DMA Interrupt Flag Offsets within channel flag

- Returns

- bool interrupt flag is set.

Definition at line 99 of file dma_common_l1f013.c.

References DMA_FLAG_OFFSET, and DMA_ISR.

◆ dma_get_number_of_data()

| uint16_t dma_get_number_of_data | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Get the Transfer Block Size.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

- Returns

- unsigned int16. Number of remaining data words to transfer (65535 maximum).

Definition at line 429 of file dma_common_l1f013.c.

References DMA_CNDTR.

◆ dma_set_channel_request()

| void dma_set_channel_request | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint8_t | request | ||

| ) |

DMA Channel Set Request Selection.

Set DMA request mapping selection for given channel. Refer to datasheet for channel request mapping tables.

- Parameters

-

[in] dma DMA controller base address: DMA1 or DMA2 [in] channel Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] request DMA request mapping.

Definition at line 37 of file dma_common_csel.c.

References DMA_CSELR, DMA_CSELR_CxS_MASK, and DMA_CSELR_CxS_SHIFT.

◆ dma_set_memory_address()

| void dma_set_memory_address | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | address | ||

| ) |

DMA Channel Set the Base Memory Address.

- Note

- The DMA channel must be disabled before setting this address. This function has no effect if the channel is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] address unsigned int32. Memory Initial Address.

Definition at line 413 of file dma_common_l1f013.c.

References DMA_CCR, DMA_CCR_EN, and DMA_CMAR.

◆ dma_set_memory_size()

| void dma_set_memory_size | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | mem_size | ||

| ) |

DMA Channel Set Memory Word Width.

Set the memory word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] mem_size unsigned int32. Memory word width DMA Channel Memory Word Width.

Definition at line 151 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_MSIZE_MASK.

◆ dma_set_number_of_data()

| void dma_set_number_of_data | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint16_t | number | ||

| ) |

DMA Channel Set the Transfer Block Size.

- Note

- The DMA channel must be disabled before setting this count value. The count is not changed if the channel is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] number unsigned int16. Number of data words to transfer (65535 maximum).

Definition at line 446 of file dma_common_l1f013.c.

References DMA_CNDTR.

◆ dma_set_peripheral_address()

| void dma_set_peripheral_address | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | address | ||

| ) |

DMA Channel Set the Peripheral Address.

Set the address of the peripheral register to or from which data is to be transferred. Refer to the documentation for the specific peripheral.

- Note

- The DMA channel must be disabled before setting this address. This function has no effect if the channel is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] address unsigned int32. Peripheral Address.

Definition at line 395 of file dma_common_l1f013.c.

References DMA_CCR, DMA_CCR_EN, and DMA_CPAR.

◆ dma_set_peripheral_size()

| void dma_set_peripheral_size | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | peripheral_size | ||

| ) |

DMA Channel Set Peripheral Word Width.

Set the peripheral word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match, or if the peripheral does not support byte or half-word writes.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] peripheral_size unsigned int32. Peripheral word width DMA Channel Peripheral Word Width.

Definition at line 171 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_PSIZE_MASK.

◆ dma_set_priority()

| void dma_set_priority | ( | uint32_t | dma, |

| uint8_t | channel, | ||

| uint32_t | prio | ||

| ) |

DMA Channel Set Priority.

Channel Priority has four levels: low to very high. This has precedence over the hardware priority.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2 [in] prio unsigned int32. Priority level DMA Channel Priority Levels.

Definition at line 134 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_PL_MASK.

◆ dma_set_read_from_memory()

| void dma_set_read_from_memory | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Transfers from Memory.

The data direction is set to read from memory.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 277 of file dma_common_l1f013.c.

References DMA_CCR, and DMA_CCR_DIR.

◆ dma_set_read_from_peripheral()

| void dma_set_read_from_peripheral | ( | uint32_t | dma, |

| uint8_t | channel | ||

| ) |

DMA Channel Enable Transfers from a Peripheral.

The data direction is set to read from a peripheral.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] channel unsigned int8. Channel number: 1-7 for DMA1 or 1-5 for DMA2

Definition at line 263 of file dma_common_l1f013.c.

References DMA_CCR.