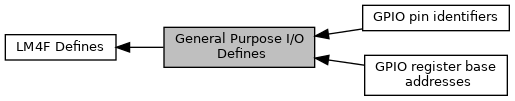

Defined Constants and Types for the LM4F General Purpose I/O More...

Modules | |

| GPIO register base addresses | |

| GPIO pin identifiers | |

Macros | |

| #define | GPIO_DATA(port) (&MMIO32((port) + 0x000)) |

| #define | GPIO_DIR(port) MMIO32((port) + 0x400) |

| #define | GPIO_IS(port) MMIO32((port) + 0x404) |

| #define | GPIO_IBE(port) MMIO32((port) + 0x408) |

| #define | GPIO_IEV(port) MMIO32((port) + 0x40c) |

| #define | GPIO_IM(port) MMIO32((port) + 0x410) |

| #define | GPIO_RIS(port) MMIO32((port) + 0x414) |

| #define | GPIO_MIS(port) MMIO32((port) + 0x418) |

| #define | GPIO_ICR(port) MMIO32((port) + 0x41c) |

| #define | GPIO_AFSEL(port) MMIO32((port) + 0x420) |

| #define | GPIO_DR2R(port) MMIO32((port) + 0x500) |

| #define | GPIO_DR4R(port) MMIO32((port) + 0x504) |

| #define | GPIO_DR8R(port) MMIO32((port) + 0x508) |

| #define | GPIO_ODR(port) MMIO32((port) + 0x50c) |

| #define | GPIO_PUR(port) MMIO32((port) + 0x510) |

| #define | GPIO_PDR(port) MMIO32((port) + 0x514) |

| #define | GPIO_SLR(port) MMIO32((port) + 0x518) |

| #define | GPIO_DEN(port) MMIO32((port) + 0x51c) |

| #define | GPIO_LOCK(port) MMIO32((port) + 0x520) |

| #define | GPIO_CR(port) MMIO32((port) + 0x524) |

| #define | GPIO_AMSEL(port) MMIO32((port) + 0x528) |

| #define | GPIO_PCTL(port) MMIO32((port) + 0x52C) |

| #define | GPIO_ADCCTL(port) MMIO32((port) + 0x530) |

| #define | GPIO_DMACTL(port) MMIO32((port) + 0x534) |

| #define | GPIO_PERIPH_ID4(port) MMIO32((port) + 0xFD0) |

| #define | GPIO_PERIPH_ID5(port) MMIO32((port) + 0xFD4) |

| #define | GPIO_PERIPH_ID6(port) MMIO32((port) + 0xFD8) |

| #define | GPIO_PERIPH_ID7(port) MMIO32((port) + 0xFDC) |

| #define | GPIO_PERIPH_ID0(port) MMIO32((port) + 0xFE0) |

| #define | GPIO_PERIPH_ID1(port) MMIO32((port) + 0xFE4) |

| #define | GPIO_PERIPH_ID2(port) MMIO32((port) + 0xFE8) |

| #define | GPIO_PERIPH_ID3(port) MMIO32((port) + 0xFEC) |

| #define | GPIO_PCELL_ID0(port) MMIO32((port) + 0xFF0) |

| #define | GPIO_PCELL_ID1(port) MMIO32((port) + 0xFF4) |

| #define | GPIO_PCELL_ID2(port) MMIO32((port) + 0xFF8) |

| #define | GPIO_PCELL_ID3(port) MMIO32((port) + 0xFFC) |

Enumerations | |

| enum | gpio_mode { GPIO_MODE_OUTPUT , GPIO_MODE_INPUT , GPIO_MODE_ANALOG } |

| enum | gpio_pullup { GPIO_PUPD_NONE , GPIO_PUPD_PULLUP , GPIO_PUPD_PULLDOWN } |

| enum | gpio_output_type { GPIO_OTYPE_PP , GPIO_OTYPE_OD } |

| enum | gpio_drive_strength { GPIO_DRIVE_2MA , GPIO_DRIVE_4MA , GPIO_DRIVE_8MA , GPIO_DRIVE_8MA_SLEW_CTL } |

| enum | gpio_trigger { GPIO_TRIG_LVL_LOW , GPIO_TRIG_LVL_HIGH , GPIO_TRIG_EDGE_FALL , GPIO_TRIG_EDGE_RISE , GPIO_TRIG_EDGE_BOTH } |

Functions | |

| void | gpio_enable_ahb_aperture (void) |

| Enable access to GPIO registers via the AHB aperture. More... | |

| void | gpio_mode_setup (uint32_t gpioport, enum gpio_mode mode, enum gpio_pullup pullup, uint8_t gpios) |

| Configure a group of pins. More... | |

| void | gpio_set_output_config (uint32_t gpioport, enum gpio_output_type otype, enum gpio_drive_strength drive, uint8_t gpios) |

| Configure output parameters of a group of pins. More... | |

| void | gpio_set_af (uint32_t gpioport, uint8_t alt_func_num, uint8_t gpios) |

| Multiplex group of pins to the given alternate function. More... | |

| void | gpio_toggle (uint32_t gpioport, uint8_t gpios) |

| Toggle a Group of Pins. More... | |

| void | gpio_unlock_commit (uint32_t gpioport, uint8_t gpios) |

| Unlock the commit control of a special function pin. More... | |

| void | gpio_configure_trigger (uint32_t gpioport, enum gpio_trigger trigger, uint8_t gpios) |

| Configure the interrupt trigger on the given GPIO pins. More... | |

| void | gpio_enable_interrupts (uint32_t gpioport, uint8_t gpios) |

| Enable interrupts on specified GPIO pins. More... | |

| void | gpio_disable_interrupts (uint32_t gpioport, uint8_t gpios) |

| Disable interrupts on specified GPIO pins. More... | |

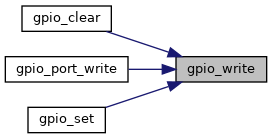

| static void | gpio_write (uint32_t gpioport, uint8_t gpios, uint8_t data) |

| Set level of a Group of Pins (atomic) More... | |

| static void | gpio_set (uint32_t gpioport, uint8_t gpios) |

| Set a Group of Pins (atomic) More... | |

| static void | gpio_clear (uint32_t gpioport, uint8_t gpios) |

| Clear a Group of Pins (atomic) More... | |

| static uint8_t | gpio_port_read (uint32_t gpioport) |

| Read level of all pins from a port (atomic) More... | |

| static void | gpio_port_write (uint32_t gpioport, uint8_t data) |

| Set level of of all pins from a port (atomic) More... | |

| static void | gpio_clear_interrupt_flag (uint32_t gpioport, uint8_t gpios) |

| Mark interrupt as serviced. More... | |

Detailed Description

Defined Constants and Types for the LM4F General Purpose I/O

- Version

- 1.0.0

- Date

- 16 March 2013

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ GPIO_ADCCTL

◆ GPIO_AFSEL

◆ GPIO_AMSEL

◆ GPIO_CR

◆ GPIO_DATA

◆ GPIO_DEN

◆ GPIO_DIR

◆ GPIO_DMACTL

◆ GPIO_DR2R

◆ GPIO_DR4R

◆ GPIO_DR8R

◆ GPIO_IBE

◆ GPIO_ICR

◆ GPIO_IEV

◆ GPIO_IM

◆ GPIO_IS

◆ GPIO_LOCK

◆ GPIO_MIS

◆ GPIO_ODR

◆ GPIO_PCELL_ID0

◆ GPIO_PCELL_ID1

◆ GPIO_PCELL_ID2

◆ GPIO_PCELL_ID3

◆ GPIO_PCTL

◆ GPIO_PDR

◆ GPIO_PERIPH_ID0

◆ GPIO_PERIPH_ID1

◆ GPIO_PERIPH_ID2

◆ GPIO_PERIPH_ID3

◆ GPIO_PERIPH_ID4

◆ GPIO_PERIPH_ID5

◆ GPIO_PERIPH_ID6

◆ GPIO_PERIPH_ID7

◆ GPIO_PUR

◆ GPIO_RIS

◆ GPIO_SLR

Enumeration Type Documentation

◆ gpio_drive_strength

| enum gpio_drive_strength |

◆ gpio_mode

| enum gpio_mode |

◆ gpio_output_type

| enum gpio_output_type |

◆ gpio_pullup

| enum gpio_pullup |

◆ gpio_trigger

| enum gpio_trigger |

Function Documentation

◆ gpio_clear()

|

inlinestatic |

Clear a Group of Pins (atomic)

Clear one or more pins of the given GPIO port. This is an atomic operation.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together.

Definition at line 298 of file gpio.h.

References gpio_write().

◆ gpio_clear_interrupt_flag()

|

inlinestatic |

Mark interrupt as serviced.

After an interrupt is services, its flag must be cleared. If the flag is not cleared, then execution will jump back to the start of the ISR after the ISR returns.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together.

Definition at line 369 of file gpio.h.

References GPIO_ICR.

◆ gpio_configure_trigger()

| void gpio_configure_trigger | ( | uint32_t | gpioport, |

| enum gpio_trigger | trigger, | ||

| uint8_t | gpios | ||

| ) |

Configure the interrupt trigger on the given GPIO pins.

Sets the Pin direction, analog/digital mode, and pull-up configuration of or a set of GPIO pins on a given GPIO port.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] trigger Trigger configuration (gpio_trigger)

- GPIO_TRIG_LVL_LOW – Trigger on low level

- GPIO_TRIG_LVL_HIGH – Trigger on high level

- GPIO_TRIG_EDGE_FALL – Trigger on falling edges

- GPIO_TRIG_EDGE_RISE – Trigger on rising edges

- GPIO_TRIG_EDGE_BOTH – Trigger on all edges

[in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together - GPIO_TRIG_LVL_LOW – Trigger on low level

Definition at line 527 of file gpio.c.

References GPIO_IBE, GPIO_IEV, GPIO_IS, GPIO_TRIG_EDGE_BOTH, GPIO_TRIG_EDGE_FALL, GPIO_TRIG_EDGE_RISE, GPIO_TRIG_LVL_HIGH, and GPIO_TRIG_LVL_LOW.

◆ gpio_disable_interrupts()

| void gpio_disable_interrupts | ( | uint32_t | gpioport, |

| uint8_t | gpios | ||

| ) |

Disable interrupts on specified GPIO pins.

Disable interrupts on the specified GPIO pins

Note that the NVIC must be enabled and properly configured for the interrupt to be routed to the CPU.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Pins whose interrupts to disable. Any combination of pins may be specified by OR'ing them together.

Definition at line 590 of file gpio.c.

References GPIO_IM.

◆ gpio_enable_ahb_aperture()

| void gpio_enable_ahb_aperture | ( | void | ) |

Enable access to GPIO registers via the AHB aperture.

All GPIO registers are accessed in libopencm3 via the AHB aperture. It provides faster control over the older APB aperture. This aperture must be enabled before calling any other gpio_*() function.

Definition at line 186 of file gpio.c.

References SYSCTL_GPIOHBCTL.

◆ gpio_enable_interrupts()

| void gpio_enable_interrupts | ( | uint32_t | gpioport, |

| uint8_t | gpios | ||

| ) |

Enable interrupts on specified GPIO pins.

Enable interrupts on the specified GPIO pins

Note that the NVIC must be enabled and properly configured for the interrupt to be routed to the CPU.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Pins whose interrupts to enable. Any combination of pins may be specified by OR'ing them together.

Definition at line 572 of file gpio.c.

References GPIO_IM.

◆ gpio_mode_setup()

| void gpio_mode_setup | ( | uint32_t | gpioport, |

| enum gpio_mode | mode, | ||

| enum gpio_pullup | pullup, | ||

| uint8_t | gpios | ||

| ) |

Configure a group of pins.

Sets the Pin direction, analog/digital mode, and pull-up configuration of or a set of GPIO pins on a given GPIO port.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] mode Pin mode (gpio_mode)

- GPIO_MODE_OUTPUT – Configure pin as output

- GPIO_MODE_INPUT – Configure pin as input

- GPIO_MODE_ANALOG – Configure pin as analog function

[in] pullup Pin pullup/pulldown configuration (gpio_pullup)

- GPIO_PUPD_NONE – Do not pull the pin high or low

- GPIO_PUPD_PULLUP – Pull the pin high

- GPIO_PUPD_PULLDOWN – Pull the pin low

[in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together - GPIO_MODE_OUTPUT – Configure pin as output

Definition at line 209 of file gpio.c.

References GPIO_AMSEL, GPIO_DEN, GPIO_DIR, GPIO_MODE_ANALOG, GPIO_MODE_INPUT, GPIO_MODE_OUTPUT, GPIO_PDR, GPIO_PUPD_NONE, GPIO_PUPD_PULLDOWN, GPIO_PUPD_PULLUP, and GPIO_PUR.

◆ gpio_port_read()

|

inlinestatic |

Read level of all pins from a port (atomic)

Read the current value of the given GPIO port. This is an atomic operation.

This is functionally identical to gpio_read (gpioport, GPIO_ALL).

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses

- Returns

- The level of all the pins on the GPIO port.

Definition at line 314 of file gpio.h.

References GPIO_ALL, and gpio_read().

◆ gpio_port_write()

|

inlinestatic |

Set level of of all pins from a port (atomic)

Set the level of all pins on the given GPIO port. This is an atomic operation.

This is functionally identical to gpio_write (gpioport, GPIO_ALL, data).

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together. [in] data Level to set pin to. Bit 0 of data corresponds to GPIO0, bit 1 to GPIO1. and so on.

Definition at line 333 of file gpio.h.

References GPIO_ALL, and gpio_write().

◆ gpio_set()

|

inlinestatic |

Set a Group of Pins (atomic)

Set one or more pins of the given GPIO port. This is an atomic operation.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together.

Definition at line 284 of file gpio.h.

References gpio_write().

◆ gpio_set_af()

| void gpio_set_af | ( | uint32_t | gpioport, |

| uint8_t | alt_func_num, | ||

| uint8_t | gpios | ||

| ) |

Multiplex group of pins to the given alternate function.

Mux the pin or group of pins to the given alternate function. Note that a number of pins may be set but only with a single AF number. This is useful when one or more of a peripheral's pins are assigned to the same alternate function.

Because AF0 is not used on the LM4F, passing 0 as the alt_func_num parameter will disable the alternate function of the given pins.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] alt_func_num Pin alternate function number or 0 to disable the alternate function multiplexing. [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together

Definition at line 321 of file gpio.c.

References GPIO_AFSEL, GPIO_DEN, GPIO_PCTL, and PCTL_AF.

◆ gpio_set_output_config()

| void gpio_set_output_config | ( | uint32_t | gpioport, |

| enum gpio_output_type | otype, | ||

| enum gpio_drive_strength | drive, | ||

| uint8_t | gpios | ||

| ) |

Configure output parameters of a group of pins.

Sets the output configuration and drive strength, of or a set of GPIO pins for a set of GPIO pins in output mode.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] otype Output driver configuration (gpio_output_type)

- GPIO_OTYPE_PP – Configure pin driver as push-pull

- GPIO_OTYPE_OD – Configure pin driver as open drain

[in] drive Pin drive strength (gpio_drive_strength)

- GPIO_DRIVE_2MA – 2mA drive

- GPIO_DRIVE_4MA – 4mA drive

- GPIO_DRIVE_8MA – 8mA drive

- GPIO_DRIVE_8MA_SLEW_CTL – 8mA drive with slew rate control

[in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together - GPIO_OTYPE_PP – Configure pin driver as push-pull

Definition at line 270 of file gpio.c.

References GPIO_DR2R, GPIO_DR4R, GPIO_DR8R, GPIO_DRIVE_2MA, GPIO_DRIVE_4MA, GPIO_DRIVE_8MA, GPIO_DRIVE_8MA_SLEW_CTL, GPIO_ODR, GPIO_OTYPE_OD, and GPIO_SLR.

◆ gpio_toggle()

| void gpio_toggle | ( | uint32_t | gpioport, |

| uint8_t | gpios | ||

| ) |

Toggle a Group of Pins.

Toggle one or more pins of the given GPIO port.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios Pin identifiers. GPIO pin identifiers

◆ gpio_unlock_commit()

| void gpio_unlock_commit | ( | uint32_t | gpioport, |

| uint8_t | gpios | ||

| ) |

Unlock the commit control of a special function pin.

Unlocks the commit control of the given pin or group of pins. If a pin is a JTAG/SWD or NMI, the pin may then be reconfigured as a GPIO pin. If the pin is not locked by default, this has no effect.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together.

Definition at line 365 of file gpio.c.

References GPIO_CR, GPIO_LOCK, and GPIO_LOCK_UNLOCK_CODE.

◆ gpio_write()

|

inlinestatic |

Set level of a Group of Pins (atomic)

Sets the level of the given pins. Bit 0 of the data parameter corresponds to GPIO0, bit 1 to GPIO1. and so on. Maskedpins (corresponding bit of gpios parameter set to zero) are returned not affected.

This is an atomic operation.

- Parameters

-

[in] gpioport GPIO block register address base GPIO register base addresses [in] gpios GPIO pin identifiers. Any combination of pins may be specified by OR'ing then together. [in] data Level to set pin to. Bit 0 of data corresponds to GPIO0, bit 1 to GPIO1. and so on.

Definition at line 269 of file gpio.h.

References GPIO_DATA.

Referenced by gpio_clear(), gpio_port_write(), and gpio_set().