libopencm3 LM4F Clock control API More...

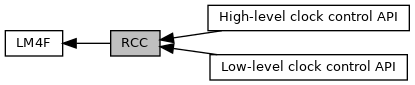

Collaboration diagram for RCC:

Modules | |

| Low-level clock control API | |

| High-level clock control API | |

Detailed Description

libopencm3 LM4F Clock control API

The LM4F clock API provides functionality for manipulating the system clock, oscillator, and PLL. Functions are provided for fine-grained control of clock control registers, while also providing higher level functionality to easily configure the main system clock source.

The following code snippet uses fine-grained mechanisms to configures the chip to run off an external 16MHz crystal, and use the PLL to derive a clock frequency of 80MHz.

// A divisor of 5 gives us a clock of 400/5 = 80MHz

#define PLLDIV_80MHZ 5

// Enable the main oscillator

// Make RCC2 override RCC

// Set XTAL value to 16MHz

// Set the oscillator source as the main oscillator

// Enable the PLL

rcc_pll_on();

// Change the clock divisor

rcc_set_pll_divisor(PLLDIV_80MHZ);

// We cannot use the PLL as a clock source until it locks

// Disable PLL bypass to derive the system clock from the PLL clock

// Keep track of frequency

lm4f_rcc_sysclk_freq = 80E6;

void rcc_set_pll_divisor(uint8_t div400)

Set the PLL clock divisor (from 400MHz)

Definition: rcc.c:273

void rcc_configure_xtal(enum xtal_t xtal)

Configure the crystal type connected to the device.

Definition: rcc.c:119

void rcc_set_osc_source(enum osc_src src)

Set the oscillator source to be used by the system clock.

Definition: rcc.c:216

void rcc_enable_rcc2(void)

Enable the use of SYSCTL_RCC2 register for clock control.

Definition: rcc.c:177

The same can be achieved by a simple call to high-level routines:

// A divisor of 5 gives us a clock of 400/5 = 80MHz

#define PLLDIV_80MHZ 5

void rcc_sysclk_config(enum osc_src src, enum xtal_t xtal, uint8_t pll_div400)

Configure the system clock source.

Definition: rcc.c:443