Functions | |

| void | rcc_configure_xtal (enum xtal_t xtal) |

| Configure the crystal type connected to the device. More... | |

| void | rcc_disable_main_osc (void) |

| Disable the main oscillator. More... | |

| void | rcc_disable_interal_osc (void) |

| Disable the internal oscillator. More... | |

| void | rcc_enable_main_osc (void) |

| Enable the main oscillator. More... | |

| void | rcc_enable_interal_osc (void) |

| Enable the internal oscillator. More... | |

| void | rcc_enable_rcc2 (void) |

| Enable the use of SYSCTL_RCC2 register for clock control. More... | |

| void | rcc_pll_off (void) |

| Power down the main PLL. More... | |

| void | rcc_pll_on (void) |

| Power up the main PLL. More... | |

| void | rcc_set_osc_source (enum osc_src src) |

| Set the oscillator source to be used by the system clock. More... | |

| void | rcc_pll_bypass_disable (void) |

| Disable the PLL bypass and use the PLL clock. More... | |

| void | rcc_pll_bypass_enable (void) |

| Enable the PLL bypass and use the oscillator clock. More... | |

| void | rcc_set_pll_divisor (uint8_t div400) |

| Set the PLL clock divisor (from 400MHz) More... | |

| void | rcc_set_pwm_divisor (enum pwm_clkdiv div) |

| Set the PWM unit clock divisor. More... | |

| void | rcc_usb_pll_off (void) |

| Power down the USB PLL. More... | |

| void | rcc_usb_pll_on (void) |

| Power up the USB PLL. More... | |

| void | rcc_wait_for_pll_ready (void) |

| Wait for main PLL to lock. More... | |

Variables | |

| uint32_t | lm4f_rcc_sysclk_freq = 16000000 |

| System clock frequency. More... | |

Detailed Description

Function Documentation

◆ rcc_configure_xtal()

| void rcc_configure_xtal | ( | enum xtal_t | xtal | ) |

Configure the crystal type connected to the device.

Configure the crystal type connected between the OSCO and OSCI pins by writing the appropriate value to the XTAL field in SYSCTL_RCC. The PLL parameters are automatically adjusted in hardware to provide a PLL clock of 400MHz.

- Parameters

-

[in] xtal predefined crystal type

- See also

- xtal_t

Definition at line 119 of file rcc.c.

References SYSCTL_RCC, and SYSCTL_RCC_XTAL_MASK.

Referenced by rcc_sysclk_config().

◆ rcc_disable_interal_osc()

| void rcc_disable_interal_osc | ( | void | ) |

Disable the internal oscillator.

Sets the IOSCDIS bit in SYSCTL_RCC, disabling the internal oscillator.

Definition at line 144 of file rcc.c.

References SYSCTL_RCC, and SYSCTL_RCC_IOSCDIS.

◆ rcc_disable_main_osc()

| void rcc_disable_main_osc | ( | void | ) |

Disable the main oscillator.

Sets the IOSCDIS bit in SYSCTL_RCC, disabling the main oscillator.

Definition at line 134 of file rcc.c.

References SYSCTL_RCC, and SYSCTL_RCC_MOSCDIS.

◆ rcc_enable_interal_osc()

| void rcc_enable_interal_osc | ( | void | ) |

Enable the internal oscillator.

Clears the IOSCDIS bit in SYSCTL_RCC, enabling the internal oscillator.

Definition at line 164 of file rcc.c.

References SYSCTL_RCC.

◆ rcc_enable_main_osc()

| void rcc_enable_main_osc | ( | void | ) |

Enable the main oscillator.

Clears the MOSCDIS bit in SYSCTL_RCC, enabling the main oscillator.

Definition at line 154 of file rcc.c.

References SYSCTL_RCC.

Referenced by rcc_sysclk_config().

◆ rcc_enable_rcc2()

| void rcc_enable_rcc2 | ( | void | ) |

Enable the use of SYSCTL_RCC2 register for clock control.

Enables the USERCC2 bit in SYSCTTL_RCC2. Settings in SYSCTL_RCC2 will override settings in SYSCTL_RCC. This function must be called before other calls to manipulate the clock, as libopencm3 uses the SYSCTL_RCC2 register.

Definition at line 177 of file rcc.c.

References SYSCTL_RCC2, and SYSCTL_RCC2_USERCC2.

Referenced by rcc_sysclk_config().

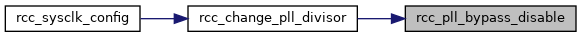

◆ rcc_pll_bypass_disable()

| void rcc_pll_bypass_disable | ( | void | ) |

Disable the PLL bypass and use the PLL clock.

Clear BYPASS2 in SYSCTL_RCC2. The system clock is derived from the PLL clock divided by the divisor specified in SYSDIV2.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 235 of file rcc.c.

References SYSCTL_RCC2.

Referenced by rcc_change_pll_divisor().

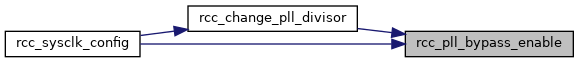

◆ rcc_pll_bypass_enable()

| void rcc_pll_bypass_enable | ( | void | ) |

Enable the PLL bypass and use the oscillator clock.

Set BYPASS2 in SYSCTL_RCC2. The system clock is derived from the oscillator clock divided by the divisor specified in SYSDIV2.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 249 of file rcc.c.

References SYSCTL_RCC2, and SYSCTL_RCC2_BYPASS2.

Referenced by rcc_change_pll_divisor(), and rcc_sysclk_config().

◆ rcc_pll_off()

| void rcc_pll_off | ( | void | ) |

Power down the main PLL.

Sets the SYSCTL_RCC2_PWRDN2 in SYSCTL_RCC2 to power down the PLL.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 190 of file rcc.c.

References SYSCTL_RCC2, and SYSCTL_RCC2_PWRDN2.

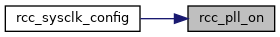

◆ rcc_pll_on()

| void rcc_pll_on | ( | void | ) |

Power up the main PLL.

Clears the PWRDN2 in SYSCTL_RCC2 to power on the PLL.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 203 of file rcc.c.

References SYSCTL_RCC2.

Referenced by rcc_sysclk_config().

◆ rcc_set_osc_source()

| void rcc_set_osc_source | ( | enum osc_src | src | ) |

Set the oscillator source to be used by the system clock.

Set the clock source for the system clock.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 216 of file rcc.c.

References SYSCTL_RCC2, and SYSCTL_RCC2_OSCSRC2_MASK.

Referenced by rcc_sysclk_config().

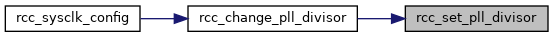

◆ rcc_set_pll_divisor()

| void rcc_set_pll_divisor | ( | uint8_t | div400 | ) |

Set the PLL clock divisor (from 400MHz)

Set the binary divisor used to predivide the system clock down for use as the timing reference for the PWM module. The divisor is expected to be a divisor from 400MHz, not 200MHz. The DIV400 is also set.

Specifies the divisor that used to generate the system clock from either the PLL output or the oscillator source (depending on the BYPASS2 bit in SYSCTL_RCC2). SYSDIV2 is used for the divisor when both the USESYSDIV bit in SYSCTL_RCC is set.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

- Parameters

-

[in] div clock divisor to apply to the 400MHz PLL clock. It is the caller's responsibility to ensure that the divisor will not create a system clock that is out of spec.

Definition at line 273 of file rcc.c.

References SYSCTL_RCC, SYSCTL_RCC2, SYSCTL_RCC2_DIV400, SYSCTL_RCC2_SYSDIV400_MASK, and SYSCTL_RCC_USESYSDIV.

Referenced by rcc_change_pll_divisor().

◆ rcc_set_pwm_divisor()

| void rcc_set_pwm_divisor | ( | enum pwm_clkdiv | div | ) |

Set the PWM unit clock divisor.

Set the binary divisor used to predivide the system clock down for use as the timing reference for the PWM module.

- Parameters

-

[in] div clock divisor to use

- See also

- pwm_clkdiv_t

Definition at line 294 of file rcc.c.

References SYSCTL_RCC, and SYSCTL_RCC_PWMDIV_MASK.

◆ rcc_usb_pll_off()

| void rcc_usb_pll_off | ( | void | ) |

Power down the USB PLL.

Sets the USBPWRDN in SYSCTL_RCC2 to power down the USB PLL.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 312 of file rcc.c.

References SYSCTL_RCC2, and SYSCTL_RCC2_USBPWRDN.

◆ rcc_usb_pll_on()

| void rcc_usb_pll_on | ( | void | ) |

Power up the USB PLL.

Clears the USBPWRDN in SYSCTL_RCC2 to power on the USB PLL.

USERCC2 must have been set by a call to rcc_enable_rcc2() before calling this function.

Definition at line 325 of file rcc.c.

References SYSCTL_RCC2.

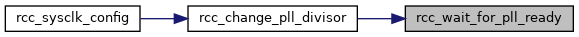

◆ rcc_wait_for_pll_ready()

| void rcc_wait_for_pll_ready | ( | void | ) |

Wait for main PLL to lock.

Waits until the LOCK bit in SYSCTL_PLLSTAT is set. This guarantees that the PLL is locked, and ready to use.

Definition at line 336 of file rcc.c.

References SYSCTL_PLLSTAT, and SYSCTL_PLLSTAT_LOCK.

Referenced by rcc_change_pll_divisor().

Variable Documentation

◆ lm4f_rcc_sysclk_freq

| uint32_t lm4f_rcc_sysclk_freq = 16000000 |

System clock frequency.

This variable is provided to keep track of the system clock frequency. It should be updated every time the system clock is changed via the fine-grained mechanisms. The initial value is 16MHz, which corresponds to the clock of the internal 16MHz oscillator.

High-level routines update the system clock automatically. For read access, it is recommended to access this variable via

If write access is desired (i.e. when changing the system clock via the fine-grained mechanisms), then include the following line in your code:

Definition at line 106 of file rcc.c.

Referenced by rcc_change_pll_divisor(), rcc_get_system_clock_frequency(), and rcc_sysclk_config().