systemcontrol.h File Reference

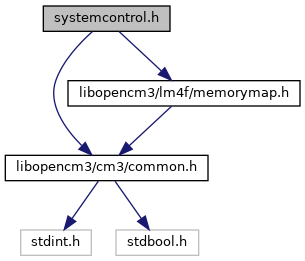

Include dependency graph for systemcontrol.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Enumerations | |

| enum | lm4f_clken { RCC_WD0 = SYSCTL_RCGCWD_OFFSET << 5 , RCC_WD1 , RCC_TIMER0 = SYSCTL_RCGCTIMER_OFFSET << 5 , RCC_TIMER1 , RCC_TIMER2 , RCC_TIMER3 , RCC_TIMER4 , RCC_TIMER5 , RCC_GPIOA = SYSCTL_RCGCGPIO_OFFSET << 5 , RCC_GPIOB , RCC_GPIOC , RCC_GPIOD , RCC_GPIOE , RCC_GPIOF , RCC_GPIOG , RCC_GPIOH , RCC_GPIOJ , RCC_GPIOK , RCC_GPIOL , RCC_GPIOM , RCC_GPION , RCC_GPIOP , RCC_GPIOQ , RCC_DMA = SYSCTL_RCGCDMA_OFFSET << 5 , RCC_HIB = SYSCTL_RCGCGPIO_OFFSET << 5 , RCC_UART0 = SYSCTL_RCGCUART_OFFSET << 5 , RCC_UART1 , RCC_UART2 , RCC_UART3 , RCC_UART4 , RCC_UART5 , RCC_UART6 , RCC_UART7 , RCC_SSI0 = SYSCTL_RCGCSSI_OFFSET << 5 , RCC_SSI1 , RCC_SSI2 , RCC_SSI3 , RCC_I2C0 = SYSCTL_RCGCI2C_OFFSET << 5 , RCC_I2C1 , RCC_I2C2 , RCC_I2C3 , RCC_I2C4 , RCC_I2C5 , RCC_USB0 = SYSCTL_RCGCUSB_OFFSET << 5 , RCC_CAN0 = SYSCTL_RCGCCAN_OFFSET << 5 , RCC_CAN1 , RCC_ADC0 = SYSCTL_RCGCADC_OFFSET << 5 , RCC_ADC1 , RCC_ACMP0 = SYSCTL_RCGCACMP_OFFSET << 5 , RCC_PWM0 = SYSCTL_RCGCPWM_OFFSET << 5 , RCC_PWM1 , RCC_QEI0 = SYSCTL_RCGCQEI_OFFSET << 5 , RCC_QEI1 , RCC_EEPROM0 = SYSCTL_RCGCEEPROM_OFFSET << 5 , RCC_WTIMER0 = SYSCTL_RCGCWTIMER_OFFSET << 5 , RCC_WTIMER1 , RCC_WTIMER2 , RCC_WTIMER3 , RCC_WTIMER4 , RCC_WTIMER5 , SCC_WD0 = SYSCTL_SCGCWD_OFFSET << 5 , SCC_WD1 , SCC_TIMER0 = SYSCTL_SCGCTIMER_OFFSET << 5 , SCC_TIMER1 , SCC_TIMER2 , SCC_TIMER3 , SCC_TIMER4 , SCC_TIMER5 , SCC_GPIOA = SYSCTL_SCGCGPIO_OFFSET << 5 , SCC_GPIOB , SCC_GPIOC , SCC_GPIOD , SCC_GPIOE , SCC_GPIOF , SCC_GPIOG , SCC_GPIOH , SCC_GPIOJ , SCC_GPIOK , SCC_GPIOL , SCC_GPIOM , SCC_GPION , SCC_GPIOP , SCC_GPIOQ , SCC_DMA = SYSCTL_SCGCDMA_OFFSET << 5 , SCC_HIB = SYSCTL_SCGCGPIO_OFFSET << 5 , SCC_UART0 = SYSCTL_SCGCUART_OFFSET << 5 , SCC_UART1 , SCC_UART2 , SCC_UART3 , SCC_UART4 , SCC_UART5 , SCC_UART6 , SCC_UART7 , SCC_SSI0 = SYSCTL_SCGCSSI_OFFSET << 5 , SCC_SSI1 , SCC_SSI2 , SCC_SSI3 , SCC_I2C0 = SYSCTL_SCGCI2C_OFFSET << 5 , SCC_I2C1 , SCC_I2C2 , SCC_I2C3 , SCC_I2C4 , SCC_I2C5 , SCC_USB0 = SYSCTL_SCGCUSB_OFFSET << 5 , SCC_CAN0 = SYSCTL_SCGCCAN_OFFSET << 5 , SCC_CAN1 , SCC_ADC0 = SYSCTL_SCGCADC_OFFSET << 5 , SCC_ADC1 , SCC_ACMP0 = SYSCTL_SCGCACMP_OFFSET << 5 , SCC_PWM0 = SYSCTL_SCGCPWM_OFFSET << 5 , SCC_PWM1 , SCC_QEI0 = SYSCTL_SCGCQEI_OFFSET << 5 , SCC_QEI1 , SCC_EEPROM0 = SYSCTL_SCGCEEPROM_OFFSET << 5 , SCC_WTIMER0 = SYSCTL_SCGCWTIMER_OFFSET << 5 , SCC_WTIMER1 , SCC_WTIMER2 , SCC_WTIMER3 , SCC_WTIMER4 , SCC_WTIMER5 , DCC_WD0 = SYSCTL_DCGCWD_OFFSET << 5 , DCC_WD1 , DCC_TIMER0 = SYSCTL_DCGCTIMER_OFFSET << 5 , DCC_TIMER1 , DCC_TIMER2 , DCC_TIMER3 , DCC_TIMER4 , DCC_TIMER5 , DCC_GPIOA = SYSCTL_DCGCGPIO_OFFSET << 5 , DCC_GPIOB , DCC_GPIOC , DCC_GPIOD , DCC_GPIOE , DCC_GPIOF , DCC_GPIOG , DCC_GPIOH , DCC_GPIOJ , DCC_GPIOK , DCC_GPIOL , DCC_GPIOM , DCC_GPION , DCC_GPIOP , DCC_GPIOQ , DCC_DMA = SYSCTL_DCGCDMA_OFFSET << 5 , DCC_HIB = SYSCTL_DCGCGPIO_OFFSET << 5 , DCC_UART0 = SYSCTL_DCGCUART_OFFSET << 5 , DCC_UART1 , DCC_UART2 , DCC_UART3 , DCC_UART4 , DCC_UART5 , DCC_UART6 , DCC_UART7 , DCC_SSI0 = SYSCTL_DCGCSSI_OFFSET << 5 , DCC_SSI1 , DCC_SSI2 , DCC_SSI3 , DCC_I2C0 = SYSCTL_DCGCI2C_OFFSET << 5 , DCC_I2C1 , DCC_I2C2 , DCC_I2C3 , DCC_I2C4 , DCC_I2C5 , DCC_USB0 = SYSCTL_DCGCUSB_OFFSET << 5 , DCC_CAN0 = SYSCTL_DCGCCAN_OFFSET << 5 , DCC_CAN1 , DCC_ADC0 = SYSCTL_DCGCADC_OFFSET << 5 , DCC_ADC1 , DCC_ACMP0 = SYSCTL_DCGCACMP_OFFSET << 5 , DCC_PWM0 = SYSCTL_DCGCPWM_OFFSET << 5 , DCC_PWM1 , DCC_QEI0 = SYSCTL_DCGCQEI_OFFSET << 5 , DCC_QEI1 , DCC_EEPROM0 = SYSCTL_DCGCEEPROM_OFFSET << 5 , DCC_WTIMER0 = SYSCTL_DCGCWTIMER_OFFSET << 5 , DCC_WTIMER1 , DCC_WTIMER2 , DCC_WTIMER3 , DCC_WTIMER4 , DCC_WTIMER5 } |

| Clock enable definitions. More... | |

Functions | |

| void | periph_clock_enable (enum lm4f_clken periph) |

| Enable the clock source for the peripheral. More... | |

| void | periph_clock_disable (enum lm4f_clken periph) |

| Disable the clock source for the peripheral. More... | |