uart.h File Reference

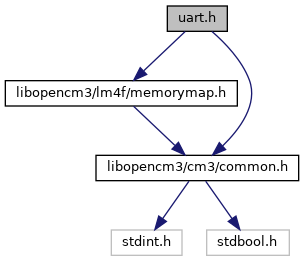

Include dependency graph for uart.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | UART0 UART0_BASE |

| #define | UART1 UART1_BASE |

| #define | UART2 UART2_BASE |

| #define | UART3 UART3_BASE |

| #define | UART4 UART4_BASE |

| #define | UART5 UART5_BASE |

| #define | UART6 UART6_BASE |

| #define | UART7 UART7_BASE |

| #define | UART_DR(uart_base) MMIO32((uart_base) + 0x00) |

| #define | UART_RSR(uart_base) MMIO32((uart_base) + 0x04) |

| #define | UART_ECR(uart_base) MMIO32((uart_base) + 0x04) |

| #define | UART_FR(uart_base) MMIO32((uart_base) + 0x18) |

| #define | UART_ILPR(uart_base) MMIO32((uart_base) + 0x20) |

| #define | UART_IBRD(uart_base) MMIO32((uart_base) + 0x24) |

| #define | UART_FBRD(uart_base) MMIO32((uart_base) + 0x28) |

| #define | UART_LCRH(uart_base) MMIO32((uart_base) + 0x2C) |

| #define | UART_CTL(uart_base) MMIO32((uart_base) + 0x30) |

| #define | UART_IFLS(uart_base) MMIO32((uart_base) + 0x34) |

| #define | UART_IM(uart_base) MMIO32((uart_base) + 0x38) |

| #define | UART_RIS(uart_base) MMIO32((uart_base) + 0x3C) |

| #define | UART_MIS(uart_base) MMIO32((uart_base) + 0x40) |

| #define | UART_ICR(uart_base) MMIO32((uart_base) + 0x44) |

| #define | UART_DMACTL(uart_base) MMIO32((uart_base) + 0x48) |

| #define | UART_LCTL(uart_base) MMIO32((uart_base) + 0x90) |

| #define | UART_LSS(uart_base) MMIO32((uart_base) + 0x94) |

| #define | UART_LTIM(uart_base) MMIO32((uart_base) + 0x98) |

| #define | UART_9BITADDR(uart_base) MMIO32((uart_base) + 0xA4) |

| #define | UART_9BITAMASK(uart_base) MMIO32((uart_base) + 0xA8) |

| #define | UART_PP(uart_base) MMIO32((uart_base) + 0xFC0) |

| #define | UART_CC(uart_base) MMIO32((uart_base) + 0xFC8) |

| #define | UART_PERIPH_ID4(uart_base) MMIO32((uart_base) + 0xFD0) |

| #define | UART_PERIPH_ID5(uart_base) MMIO32((uart_base) + 0xFD4) |

| #define | UART_PERIPH_ID6(uart_base) MMIO32((uart_base) + 0xFD8) |

| #define | UART_PERIPH_ID7(uart_base) MMIO32((uart_base) + 0xFDC) |

| #define | UART_PERIPH_ID0(uart_base) MMIO32((uart_base) + 0xFE0) |

| #define | UART_PERIPH_ID1(uart_base) MMIO32((uart_base) + 0xFE4) |

| #define | UART_PERIPH_ID2(uart_base) MMIO32((uart_base) + 0xFE8) |

| #define | UART_PERIPH_ID3(uart_base) MMIO32((uart_base) + 0xFEC) |

| #define | UART_PCELL_ID0(uart_base) MMIO32((uart_base) + 0xFF0) |

| #define | UART_PCELL_ID1(uart_base) MMIO32((uart_base) + 0xFF4) |

| #define | UART_PCELL_ID2(uart_base) MMIO32((uart_base) + 0xFF8) |

| #define | UART_PCELL_ID3(uart_base) MMIO32((uart_base) + 0xFFC) |

| #define | UART_DR_OE (1 << 11) |

| Overrun Error. More... | |

| #define | UART_DR_BE (1 << 10) |

| Break Error. More... | |

| #define | UART_DR_PE (1 << 9) |

| Parity Error. More... | |

| #define | UART_DR_FE (1 << 8) |

| Framing Error. More... | |

| #define | UART_DR_DATA_MASK (0xFF << 0) |

| Data transmitted or received. More... | |

| #define | UART_RSR_OE (1 << 3) |

| Overrun Error. More... | |

| #define | UART_RSR_BE (1 << 2) |

| Break Error. More... | |

| #define | UART_RSR_PE (1 << 1) |

| Parity Error. More... | |

| #define | UART_RSR_FE (1 << 0) |

| Framing Error. More... | |

| #define | UART_FR_TXFE (1 << 7) |

| Tx FIFO empty. More... | |

| #define | UART_FR_RXFF (1 << 6) |

| Rx FIFO full. More... | |

| #define | UART_FR_TXFF (1 << 5) |

| Tx FIFO full. More... | |

| #define | UART_FR_RXFE (1 << 4) |

| Rx FIFO empty. More... | |

| #define | UART_FR_BUSY (1 << 3) |

| UART Busy. More... | |

| #define | UART_FR_CTS (1 << 0) |

| Clear To Send. More... | |

| #define | UART_LCRH_SPS (1 << 7) |

| Stick parity select. More... | |

| #define | UART_LCRH_WLEN_MASK (3 << 5) |

| Word length. More... | |

| #define | UART_LCRH_WLEN_5 (0 << 5) |

| #define | UART_LCRH_WLEN_6 (1 << 5) |

| #define | UART_LCRH_WLEN_7 (2 << 5) |

| #define | UART_LCRH_WLEN_8 (3 << 5) |

| #define | UART_LCRH_FEN (1 << 4) |

| Enable FIFOs. More... | |

| #define | UART_LCRH_STP2 (1 << 3) |

| Two stop bits select. More... | |

| #define | UART_LCRH_EPS (1 << 2) |

| Even parity select. More... | |

| #define | UART_LCRH_PEN (1 << 1) |

| Parity enable. More... | |

| #define | UART_LCRH_BRK (1 << 0) |

| Send break. More... | |

| #define | UART_CTL_CTSEN (1 << 15) |

| Enable Clear To Send. More... | |

| #define | UART_CTL_RTSEN (1 << 14) |

| Enable Request To Send. More... | |

| #define | UART_CTL_RTS (1 << 11) |

| Request To Send. More... | |

| #define | UART_CTL_DTR (1 << 10) |

| Data terminal ready. More... | |

| #define | UART_CTL_RXE (1 << 9) |

| Rx Enable. More... | |

| #define | UART_CTL_TXE (1 << 8) |

| Tx Enable. More... | |

| #define | UART_CTL_LBE (1 << 7) |

| Loop back enable. More... | |

| #define | UART_CTL_LIN (1 << 6) |

| LIN mode enable. More... | |

| #define | UART_CTL_HSE (1 << 5) |

| High speed Enable. More... | |

| #define | UART_CTL_EOT (1 << 4) |

| End of transmission. More... | |

| #define | UART_CTL_SMART (1 << 3) |

| ISO 7816 Smart Card support. More... | |

| #define | UART_CTL_SIRLIP (1 << 2) |

| SIR low-power mode. More... | |

| #define | UART_CTL_SIREN (1 << 1) |

| SIR enable. More... | |

| #define | UART_CTL_UARTEN (1 << 0) |

| UART enable. More... | |

| #define | UART_IFLS_RXIFLSEL_MASK (7 << 3) |

| UART Rx interrupt FIFO level select. More... | |

| #define | UART_IFLS_RXIFLSEL_1_8 (0 << 3) |

| #define | UART_IFLS_RXIFLSEL_1_4 (1 << 3) |

| #define | UART_IFLS_RXIFLSEL_1_2 (2 << 3) |

| #define | UART_IFLS_RXIFLSEL_3_4 (3 << 3) |

| #define | UART_IFLS_RXIFLSEL_7_8 (4 << 3) |

| #define | UART_IFLS_TXIFLSEL_MASK (7 << 0) |

| UART Tx interrupt FIFO level select. More... | |

| #define | UART_IFLS_TXIFLSEL_7_8 (0 << 0) |

| #define | UART_IFLS_TXIFLSEL_3_4 (1 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_2 (2 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_4 (3 << 0) |

| #define | UART_IFLS_TXIFLSEL_1_8 (4 << 0) |

| #define | UART_IM_LME5IM (1 << 15) |

| LIN mode edge 5 interrupt mask. More... | |

| #define | UART_IM_LME1IM (1 << 14) |

| LIN mode edge 1 interrupt mask. More... | |

| #define | UART_IM_LMSBIM (1 << 13) |

| LIN mode sync break interrupt mask. More... | |

| #define | UART_IM_9BITIM (1 << 12) |

| 9-bit mode interrupt mask More... | |

| #define | UART_IM_OEIM (1 << 10) |

| Overrun error interrupt mask. More... | |

| #define | UART_IM_BEIM (1 << 9) |

| Break error interrupt mask. More... | |

| #define | UART_IM_PEIM (1 << 8) |

| Parity error interrupt mask. More... | |

| #define | UART_IM_FEIM (1 << 7) |

| Framing error interrupt mask. More... | |

| #define | UART_IM_RTIM (1 << 6) |

| Receive time-out interrupt mask. More... | |

| #define | UART_IM_TXIM (1 << 5) |

| Transmit interrupt mask. More... | |

| #define | UART_IM_RXIM (1 << 4) |

| Receive interrupt mask. More... | |

| #define | UART_IM_DSRIM (1 << 3) |

| Data Set Ready modem interrupt mask. More... | |

| #define | UART_IM_DCDIM (1 << 2) |

| Data Carrier Detect modem interrupt mask. More... | |

| #define | UART_IM_CTSIM (1 << 1) |

| Clear To Send modem interrupt mask. More... | |

| #define | UART_IM_RIIM (1 << 0) |

| Ring Indicator modem interrupt mask. More... | |

| #define | UART_DMACTL_DMAERR (1 << 2) |

| DMA on error. More... | |

| #define | UART_DMACTL_TXDMAE (1 << 1) |

| Transmit DMA enable. More... | |

| #define | UART_DMACTL_RXDMAE (1 << 0) |

| Receive DMA enable. More... | |

| #define | UART_LCTL_BLEN_MASK (3 << 4) |

| Sync break length. More... | |

| #define | UART_LCTL_BLEN_16T (3 << 4) |

| #define | UART_LCTL_BLEN_15T (2 << 4) |

| #define | UART_LCTL_BLEN_14T (1 << 4) |

| #define | UART_LCTL_BLEN_13T (0 << 4) |

| #define | UART_LCTL_MASTER (1 << 0) |

| LIN master enable. More... | |

| #define | UART_UART_9BITADDR_9BITEN (1 << 15) |

| Enable 9-bit mode. More... | |

| #define | UART_UART_9BITADDR_ADDR_MASK (0xFF << 0) |

| Self-address for 9-bit mode. More... | |

| #define | UART_UART_PP_NB (1 << 1) |

| 9-bit support More... | |

| #define | UART_UART_PP_SC (1 << 0) |

| Smart Card support. More... | |

| #define | UART_CC_CS_MASK (0xF << 0) |

| UART baud clock source. More... | |

| #define | UART_CC_CS_SYSCLK (0x0 << 0) |

| #define | UART_CC_CS_PIOSC (0x5 << 0) |

Enumerations | |

| enum | uart_parity { UART_PARITY_NONE , UART_PARITY_ODD , UART_PARITY_EVEN , UART_PARITY_STICK_0 , UART_PARITY_STICK_1 } |

| enum | uart_flowctl { UART_FLOWCTL_NONE , UART_FLOWCTL_RTS , UART_FLOWCTL_CTS , UART_FLOWCTL_RTS_CTS } |

| enum | uart_interrupt_flag { UART_INT_LME5 = UART_IM_LME5IM , UART_INT_LME1 = UART_IM_LME1IM , UART_INT_LMSB = UART_IM_LMSBIM , UART_INT_9BIT = UART_IM_9BITIM , UART_INT_OE = UART_IM_OEIM , UART_INT_BE = UART_IM_BEIM , UART_INT_PE = UART_IM_PEIM , UART_INT_FE = UART_IM_FEIM , UART_INT_RT = UART_IM_RTIM , UART_INT_TX = UART_IM_TXIM , UART_INT_RX = UART_IM_RXIM , UART_INT_DSR = UART_IM_DSRIM , UART_INT_DCD = UART_IM_DCDIM , UART_INT_CTS = UART_IM_CTSIM , UART_INT_RI = UART_IM_RIIM } |

| UART interrupt masks. More... | |

| enum | uart_fifo_rx_trigger_level { UART_FIFO_RX_TRIG_1_8 = UART_IFLS_RXIFLSEL_1_8 , UART_FIFO_RX_TRIG_1_4 = UART_IFLS_RXIFLSEL_1_4 , UART_FIFO_RX_TRIG_1_2 = UART_IFLS_RXIFLSEL_1_2 , UART_FIFO_RX_TRIG_3_4 = UART_IFLS_RXIFLSEL_3_4 , UART_FIFO_RX_TRIG_7_8 = UART_IFLS_RXIFLSEL_7_8 } |

| UART RX FIFO interrupt trigger levels. More... | |

| enum | uart_fifo_tx_trigger_level { UART_FIFO_TX_TRIG_7_8 = UART_IFLS_TXIFLSEL_7_8 , UART_FIFO_TX_TRIG_3_4 = UART_IFLS_TXIFLSEL_3_4 , UART_FIFO_TX_TRIG_1_2 = UART_IFLS_TXIFLSEL_1_2 , UART_FIFO_TX_TRIG_1_4 = UART_IFLS_TXIFLSEL_1_4 , UART_FIFO_TX_TRIG_1_8 = UART_IFLS_TXIFLSEL_1_8 } |

| UART TX FIFO interrupt trigger levels. More... | |

Functions | |

| void | uart_set_baudrate (uint32_t uart, uint32_t baud) |

| Set UART baudrate. More... | |

| void | uart_set_databits (uint32_t uart, uint8_t databits) |

| Set UART databits. More... | |

| void | uart_set_stopbits (uint32_t uart, uint8_t stopbits) |

| Set UART stopbits. More... | |

| void | uart_set_parity (uint32_t uart, enum uart_parity parity) |

| Set UART parity. More... | |

| void | uart_set_mode (uint32_t uart, uint32_t mode) |

| void | uart_set_flow_control (uint32_t uart, enum uart_flowctl flow) |

| Set the flow control scheme. More... | |

| void | uart_enable (uint32_t uart) |

| Enable the UART. More... | |

| void | uart_disable (uint32_t uart) |

| Disable the UART. More... | |

| void | uart_clock_from_piosc (uint32_t uart) |

| Clock the UART module from the internal oscillator. More... | |

| void | uart_clock_from_sysclk (uint32_t uart) |

| Clock the UART module from the system clock. More... | |

| void | uart_send (uint32_t uart, uint16_t data) |

| UART Send a Data Word. More... | |

| uint16_t | uart_recv (uint32_t uart) |

| UART Read a Received Data Word. More... | |

| void | uart_wait_send_ready (uint32_t uart) |

| UART Wait for Transmit Data Buffer Not Full. More... | |

| void | uart_wait_recv_ready (uint32_t uart) |

| UART Wait for Received Data Available. More... | |

| void | uart_send_blocking (uint32_t uart, uint16_t data) |

| UART Send Data Word with Blocking. More... | |

| uint16_t | uart_recv_blocking (uint32_t uart) |

| UART Read a Received Data Word with Blocking. More... | |

| void | uart_enable_rx_dma (uint32_t uart) |

| Enable the UART Receive DMA. More... | |

| void | uart_disable_rx_dma (uint32_t uart) |

| Disable the UART Receive DMA. More... | |

| void | uart_enable_tx_dma (uint32_t uart) |

| Enable the UART Transmit DMA. More... | |

| void | uart_disable_tx_dma (uint32_t uart) |

| Disable the UART Transmit DMA. More... | |

| void | uart_enable_fifo (uint32_t uart) |

| Enable FIFO for the UART. More... | |

| void | uart_disable_fifo (uint32_t uart) |

| Disable FIFO for the UART. More... | |

| void | uart_set_fifo_trigger_levels (uint32_t uart, enum uart_fifo_rx_trigger_level rx_level, enum uart_fifo_tx_trigger_level tx_level) |

| Set the FIFO trigger levels. More... | |

| void | uart_enable_interrupts (uint32_t uart, enum uart_interrupt_flag ints) |

| Enable Specific UART Interrupts. More... | |

| void | uart_disable_interrupts (uint32_t uart, enum uart_interrupt_flag ints) |

| Enable Specific UART Interrupts. More... | |

| void | uart_enable_rx_interrupt (uint32_t uart) |

| Enable the UART Receive Interrupt. More... | |

| void | uart_disable_rx_interrupt (uint32_t uart) |

| Disable the UART Receive Interrupt. More... | |

| void | uart_enable_tx_interrupt (uint32_t uart) |

| Enable the UART Transmit Interrupt. More... | |

| void | uart_disable_tx_interrupt (uint32_t uart) |

| Disable the UART Transmit Interrupt. More... | |

| void | uart_clear_interrupt_flag (uint32_t uart, enum uart_interrupt_flag ints) |

| Mark interrupt as serviced. More... | |

| static bool | uart_is_tx_fifo_full (uint32_t uart) |

| Determine if the TX fifo is full. More... | |

| static bool | uart_is_tx_fifo_empty (uint32_t uart) |

| Determine if the TX fifo is empty. More... | |

| static bool | uart_is_rx_fifo_full (uint32_t uart) |

| Determine if the RX fifo is full. More... | |

| static bool | uart_is_rx_fifo_empty (uint32_t uart) |

| Determine if the RX fifo is empty. More... | |

| static bool | uart_is_interrupt_source (uint32_t uart, enum uart_interrupt_flag source) |

| Determine if interrupt is generated by the given source. More... | |