ssp.h File Reference

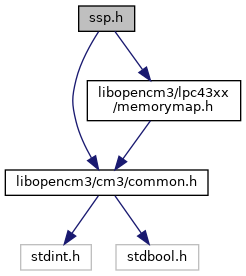

Include dependency graph for ssp.h:

Go to the source code of this file.

Macros | |

| #define | SSP0 SSP0_BASE |

| #define | SSP1 SSP1_BASE |

| #define | SSP_CR0(port) MMIO32((port) + 0x000) |

| #define | SSP0_CR0 SSP_CR0(SSP0) |

| #define | SSP1_CR0 SSP_CR0(SSP1) |

| #define | SSP_CR1(port) MMIO32((port) + 0x004) |

| #define | SSP0_CR1 SSP_CR1(SSP0) |

| #define | SSP1_CR1 SSP_CR1(SSP1) |

| #define | SSP_DR(port) MMIO32((port) + 0x008) |

| #define | SSP0_DR SSP_DR(SSP0) |

| #define | SSP1_DR SSP_DR(SSP1) |

| #define | SSP_SR(port) MMIO32((port) + 0x00C) |

| #define | SSP0_SR SSP_SR(SSP0) |

| #define | SSP1_SR SSP_SR(SSP1) |

| #define | SSP_SR_TFE BIT0 |

| #define | SSP_SR_TNF BIT1 |

| #define | SSP_SR_RNE BIT2 |

| #define | SSP_SR_RFF BIT3 |

| #define | SSP_SR_BSY BIT4 |

| #define | SSP_CPSR(port) MMIO32((port) + 0x010) |

| #define | SSP0_CPSR SSP_CPSR(SSP0) |

| #define | SSP1_CPSR SSP_CPSR(SSP1) |

| #define | SSP_IMSC(port) MMIO32((port) + 0x014) |

| #define | SSP0_IMSC SSP_IMSC(SSP0) |

| #define | SSP1_IMSC SSP_IMSC(SSP1) |

| #define | SSP_RIS(port) MMIO32((port) + 0x018) |

| #define | SSP0_RIS SSP_RIS(SSP0) |

| #define | SSP1_RIS SSP_RIS(SSP1) |

| #define | SSP_MIS(port) MMIO32((port) + 0x01C) |

| #define | SSP0_MIS SSP_MIS(SSP0) |

| #define | SSP1_MIS SSP_MIS(SSP1) |

| #define | SSP_ICR(port) MMIO32((port) + 0x020) |

| #define | SSP0_ICR SSP_ICR(SSP0) |

| #define | SSP1_ICR SSP_ICR(SSP1) |

| #define | SSP_DMACR(port) MMIO32((port) + 0x024) |

| #define | SSP0_DMACR SSP_DMACR(SSP0) |

| #define | SSP1_DMACR SSP_DMACR(SSP1) |

| #define | SSP_DMACR_RXDMAE 0x1 |

| #define | SSP_DMACR_TXDMAE 0x2 |

| #define | SSP_ENABLE BIT1 |

Enumerations | |

| enum | ssp_num_t { SSP0_NUM = 0x0 , SSP1_NUM = 0x1 } |

| enum | ssp_datasize_t { SSP_DATA_4BITS = 0x3 , SSP_DATA_5BITS = 0x4 , SSP_DATA_6BITS = 0x5 , SSP_DATA_7BITS = 0x6 , SSP_DATA_8BITS = 0x7 , SSP_DATA_9BITS = 0x8 , SSP_DATA_10BITS = 0x9 , SSP_DATA_11BITS = 0xA , SSP_DATA_12BITS = 0xB , SSP_DATA_13BITS = 0xC , SSP_DATA_14BITS = 0xD , SSP_DATA_15BITS = 0xE , SSP_DATA_16BITS = 0xF } |

| enum | ssp_frame_format_t { SSP_FRAME_SPI = 0x00 , SSP_FRAME_TI = BIT4 , SSP_FRAM_MICROWIRE = BIT5 } |

| enum | ssp_cpol_cpha_t { SSP_CPOL_0_CPHA_0 = 0x0 , SSP_CPOL_1_CPHA_0 = BIT6 , SSP_CPOL_0_CPHA_1 = BIT7 , SSP_CPOL_1_CPHA_1 = (BIT6|BIT7) } |

| enum | ssp_mode_t { SSP_MODE_NORMAL = 0x0 , SSP_MODE_LOOPBACK = BIT0 } |

| enum | ssp_master_slave_t { SSP_MASTER = 0x0 , SSP_SLAVE = BIT2 } |

| enum | ssp_slave_option_t { SSP_SLAVE_OUT_ENABLE = 0x0 , SSP_SLAVE_OUT_DISABLE = BIT3 } |

Functions | |

| void | ssp_disable (ssp_num_t ssp_num) |

| void | ssp_init (ssp_num_t ssp_num, ssp_datasize_t data_size, ssp_frame_format_t frame_format, ssp_cpol_cpha_t cpol_cpha_format, uint8_t serial_clock_rate, uint8_t clk_prescale, ssp_mode_t mode, ssp_master_slave_t master_slave, ssp_slave_option_t slave_option) |

| uint16_t | ssp_transfer (ssp_num_t ssp_num, uint16_t data) |