uart.h File Reference

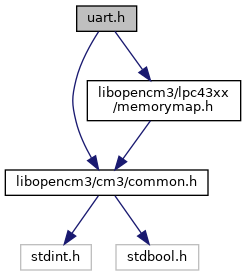

Include dependency graph for uart.h:

Go to the source code of this file.

Macros | |

| #define | UART0 USART0_BASE /* APB0 */ |

| #define | UART1 UART1_BASE /* APB0 */ |

| #define | UART2 USART2_BASE /* APB2 */ |

| #define | UART3 USART3_BASE /* APB2 */ |

| #define | UART_RBR(port) MMIO32((port) + 0x000) /* 8bits */ |

| #define | UART_THR(port) MMIO32((port) + 0x000) /* 8bits */ |

| #define | UART_DLL(port) MMIO32((port) + 0x000) /* 8bits */ |

| #define | UART_DLM(port) MMIO32((port) + 0x004) /* 8bits */ |

| #define | UART_IER(port) MMIO32((port) + 0x004) |

| #define | UART_IIR(port) MMIO32((port) + 0x008) |

| #define | UART_FCR(port) MMIO32((port) + 0x008) |

| #define | UART_LCR(port) MMIO32((port) + 0x00C) |

| #define | UART_LSR(port) MMIO32((port) + 0x014) |

| #define | UART_ACR(port) MMIO32((port) + 0x020) |

| #define | UART_ICR(port) MMIO32((port) + 0x024) |

| #define | UART_FDR(port) MMIO32((port) + 0x028) |

| #define | UART_OSR(port) MMIO32((port) + 0x02C) |

| #define | UART_HDEN(port) MMIO32((port) + 0x040) |

| #define | UART_SCICTRL(port) MMIO32((port) + 0x048) |

| #define | UART_RS485CTRL(port) MMIO32((port) + 0x04C) |

| #define | UART_RS485ADRMATCH(port) MMIO32((port) + 0x050) |

| #define | UART_RS485DLY(port) MMIO32((port) + 0x054) |

| #define | UART_SYNCCTRL(port) MMIO32((port) + 0x058) |

| #define | UART_TER(port) MMIO32((port) + 0x05C) |

| #define | UART_RBR_MASKBIT ((uint8_t)0xFF) |

| #define | UART_THR_MASKBIT ((uint8_t)0xFF) |

| #define | UART_LOAD_DLL(div) ((div) & 0xFF) |

| #define | UART_DLL_MASKBIT ((uint8_t)0xFF) |

| #define | UART_DLM_MASKBIT ((uint8_t)0xFF) |

| #define | UART_LOAD_DLM(div) (((div) >> 8) & 0xFF) |

| #define | UART_IER_RBRINT_EN (1 << 0) |

| #define | UART_IER_THREINT_EN (1 << 1) |

| #define | UART_IER_RLSINT_EN (1 << 2) |

| #define | UART1_IER_MSINT_EN (1 << 3) |

| #define | UART1_IER_CTSINT_EN (1 << 7) |

| #define | UART_IER_ABEOINT_EN (1 << 8) |

| #define | UART_IER_ABTOINT_EN (1 << 9) |

| #define | UART_IER_BITMASK ((uint32_t)(0x307)) |

| #define | UART1_IER_BITMASK ((uint32_t)(0x38F)) |

| #define | UART_IIR_INTSTAT_PEND (1 << 0) |

| #define | UART1_IIR_INTID_MODEM (0 << 1) |

| #define | UART_IIR_INTID_THRE (1 << 1) |

| #define | UART_IIR_INTID_RDA (2 << 1) |

| #define | UART_IIR_INTID_RLS (3 << 1) |

| #define | UART_IIR_INTID_CTI (6 << 1) |

| #define | UART_IIR_INTID_MASK (7 << 1) |

| #define | UART_IIR_FIFO_EN (3 << 6) |

| #define | UART_IIR_ABEO_INT (1 << 8) |

| #define | UART_IIR_ABTO_INT (1 << 9) |

| #define | UART_IIR_BITMASK ((uint32_t)(0x3CF)) |

| #define | UART_FCR_FIFO_EN (1 << 0) |

| #define | UART_FCR_RX_RS (1 << 1) |

| #define | UART_FCR_TX_RS (1 << 2) |

| #define | UART_FCR_DMAMODE_SEL (1 << 3) |

| #define | UART_FCR_TRG_LEV0 (0 << 6) |

| #define | UART_FCR_TRG_LEV1 (1 << 6) |

| #define | UART_FCR_TRG_LEV2 (2 << 6) |

| #define | UART_FCR_TRG_LEV3 (3 << 6) |

| #define | UART_FCR_BITMASK ((uint8_t)(0xCF)) |

| #define | UART_TX_FIFO_SIZE (16) |

| #define | UART_LCR_WLEN5 (0 << 0) |

| #define | UART_LCR_WLEN6 (1 << 0) |

| #define | UART_LCR_WLEN7 (2 << 0) |

| #define | UART_LCR_WLEN8 (3 << 0) |

| #define | UART_LCR_ONE_STOPBIT (0 << 2) |

| #define | UART_LCR_TWO_STOPBIT (1 << 2) |

| #define | UART_LCR_NO_PARITY (0 << 3) |

| #define | UART_LCR_PARITY_EN (1 << 3) |

| #define | UART_LCR_PARITY_ODD (0 << 4) |

| #define | UART_LCR_PARITY_EVEN (1 << 4) |

| #define | UART_LCR_PARITY_SP_1 (1 << 5) |

| #define | UART_LCR_PARITY_SP_0 ((1 << 5) | (1 << 4)) |

| #define | UART_LCR_BREAK_EN (1 << 6) |

| #define | UART_LCR_DLAB_EN (1 << 7) |

| #define | UART_LCR_BITMASK ((uint8_t)(0xFF)) |

| #define | UART_LSR_RDR (1 << 0) |

| #define | UART_LSR_OE (1 << 1) |

| #define | UART_LSR_PE (1 << 2) |

| #define | UART_LSR_FE (1 << 3) |

| #define | UART_LSR_BI (1 << 4) |

| #define | UART_LSR_THRE (1 << 5) |

| #define | UART_LSR_TEMT (1 << 6) |

| #define | UART_LSR_RXFE (1 << 7) |

| #define | UART_LSR_BITMASK ((uint8_t)(0xFF)) |

| #define | UART_LSR_ERROR_MASK (UART_LSR_OE | UART_LSR_PE | UART_LSR_FE | UART_LSR_BI | UART_LSR_RXFE) |

| #define | UART_SCR_BIMASK ((uint8_t)(0xFF)) |

| #define | UART_ACR_START (1 << 0) |

| #define | UART_ACR_MODE (1 << 1) |

| #define | UART_ACR_AUTO_RESTART (1 << 2) |

| #define | UART_ACR_ABEOINT_CLR (1 << 8) |

| #define | UART_ACR_ABTOINT_CLR (1 << 9) |

| #define | UART_ACR_BITMASK ((uint32_t)(0x307)) |

| #define | UART_ICR_IRDAEN (1 << 0) |

| #define | UART_ICR_IRDAINV (1 << 1) |

| #define | UART_ICR_FIXPULSE_EN (1 << 2) |

| #define | UART_ICR_PULSEDIV(n) ((uint32_t)(((n)&0x07)<<3)) |

| #define | UART_ICR_BITMASK ((uint32_t)(0x3F)) |

| #define | UART_HDEN_HDEN (1 << 0) |

| #define | UART_SCICTRL_SCIEN (1 << 0) |

| #define | UART_SCICTRL_NACKDIS (1 << 1) |

| #define | UART_SCICTRL_PROTSEL_T1 (1 << 2) |

| #define | UART_SCICTRL_TXRETRY(n) ((uint32_t)(((n)&0x07)<<5)) |

| #define | UART_SCICTRL_GUARDTIME(n) ((uint32_t)(((n)&0xFF)<<8)) |

| #define | UART_SYNCCTRL_SYNC (1 << 0) |

| #define | UART_SYNCCTRL_CSRC_MASTER (1 << 1) |

| #define | UART_SYNCCTRL_FES (1 << 2) |

| #define | UART_SYNCCTRL_TSBYPASS (1 << 3) |

| #define | UART_SYNCCTRL_CSCEN (1 << 4) |

| #define | UART_SYNCCTRL_NOSTARTSTOP (1 << 5) |

| #define | UART_SYNCCTRL_CCCLR (1 << 6) |

| #define | UART_FDR_DIVADDVAL(n) ((uint32_t)((n)&0x0F)) |

| #define | UART_FDR_MULVAL(n) ((uint32_t)(((n)<<4)&0xF0)) |

| #define | UART_FDR_BITMASK ((uint32_t)(0xFF)) |

| #define | UART_TER_TXEN (1 << 0) /* Transmit enable bit */ |

| #define | UART_FIFOLVL_RX(n) ((uint32_t)((n)&0x0F)) |

| #define | UART_FIFOLVL_TX(n) ((uint32_t)(((n)>>8)&0x0F)) |

| #define | UART_FIFOLVL_BITMASK ((uint32_t)(0x0F0F)) |

Enumerations | |

| enum | uart_databit_t { UART_DATABIT_5 = UART_LCR_WLEN5 , UART_DATABIT_6 = UART_LCR_WLEN6 , UART_DATABIT_7 = UART_LCR_WLEN7 , UART_DATABIT_8 = UART_LCR_WLEN8 } |

| enum | uart_stopbit_t { UART_STOPBIT_1 = UART_LCR_ONE_STOPBIT , UART_STOPBIT_2 = UART_LCR_TWO_STOPBIT } |

| enum | uart_parity_t { UART_PARITY_NONE = UART_LCR_NO_PARITY , UART_PARITY_ODD = (UART_LCR_PARITY_ODD | UART_LCR_PARITY_EN) , UART_PARITY_EVEN = (UART_LCR_PARITY_EVEN | UART_LCR_PARITY_EN) , UART_PARITY_SP_1 = (UART_LCR_PARITY_SP_1 | UART_LCR_PARITY_EN) , UART_PARITY_SP_0 = (UART_LCR_PARITY_SP_0 | UART_LCR_PARITY_EN) } |

| enum | uart_num_t { UART0_NUM = UART0 , UART1_NUM = UART1 , UART2_NUM = UART2 , UART3_NUM = UART3 } |

| enum | uart_error_t { UART_NO_ERROR = 0 , UART_TIMEOUT_ERROR = 1 } |

| enum | uart_rx_data_ready_t { UART_RX_NO_DATA = 0 , UART_RX_DATA_READY = 1 , UART_RX_DATA_ERROR = 2 } |

Functions | |

| void | uart_init (uart_num_t uart_num, uart_databit_t data_nb_bits, uart_stopbit_t data_nb_stop, uart_parity_t data_parity, uint16_t uart_divisor, uint8_t uart_divaddval, uint8_t uart_mulval) |

| uart_rx_data_ready_t | uart_rx_data_ready (uart_num_t uart_num) |

| uint8_t | uart_read (uart_num_t uart_num) |

| uint8_t | uart_read_timeout (uart_num_t uart_num, uint32_t rx_timeout_nb_cycles, uart_error_t *error) |

| void | uart_write (uart_num_t uart_num, uint8_t data) |

Macro Definition Documentation

◆ UART0

| #define UART0 USART0_BASE /* APB0 */ |

◆ UART1

| #define UART1 UART1_BASE /* APB0 */ |

◆ UART1_IER_BITMASK

◆ UART1_IER_CTSINT_EN

◆ UART1_IER_MSINT_EN

◆ UART1_IIR_INTID_MODEM

◆ UART2

| #define UART2 USART2_BASE /* APB2 */ |

◆ UART3

| #define UART3 USART3_BASE /* APB2 */ |

◆ UART_ACR

◆ UART_ACR_ABEOINT_CLR

◆ UART_ACR_ABTOINT_CLR

◆ UART_ACR_AUTO_RESTART

◆ UART_ACR_BITMASK

◆ UART_ACR_MODE

◆ UART_ACR_START

◆ UART_DLL

◆ UART_DLL_MASKBIT

◆ UART_DLM

◆ UART_DLM_MASKBIT

◆ UART_FCR

◆ UART_FCR_BITMASK

◆ UART_FCR_DMAMODE_SEL

◆ UART_FCR_FIFO_EN

◆ UART_FCR_RX_RS

◆ UART_FCR_TRG_LEV0

◆ UART_FCR_TRG_LEV1

◆ UART_FCR_TRG_LEV2

◆ UART_FCR_TRG_LEV3

◆ UART_FCR_TX_RS

◆ UART_FDR

◆ UART_FDR_BITMASK

◆ UART_FDR_DIVADDVAL

◆ UART_FDR_MULVAL

◆ UART_FIFOLVL_BITMASK

◆ UART_FIFOLVL_RX

◆ UART_FIFOLVL_TX

◆ UART_HDEN

◆ UART_HDEN_HDEN

◆ UART_ICR

◆ UART_ICR_BITMASK

◆ UART_ICR_FIXPULSE_EN

◆ UART_ICR_IRDAEN

◆ UART_ICR_IRDAINV

◆ UART_ICR_PULSEDIV

◆ UART_IER

◆ UART_IER_ABEOINT_EN

◆ UART_IER_ABTOINT_EN

◆ UART_IER_BITMASK

◆ UART_IER_RBRINT_EN

◆ UART_IER_RLSINT_EN

◆ UART_IER_THREINT_EN

◆ UART_IIR

◆ UART_IIR_ABEO_INT

◆ UART_IIR_ABTO_INT

◆ UART_IIR_BITMASK

◆ UART_IIR_FIFO_EN

◆ UART_IIR_INTID_CTI

◆ UART_IIR_INTID_MASK

◆ UART_IIR_INTID_RDA

◆ UART_IIR_INTID_RLS

◆ UART_IIR_INTID_THRE

◆ UART_IIR_INTSTAT_PEND

◆ UART_LCR

◆ UART_LCR_BITMASK

◆ UART_LCR_BREAK_EN

◆ UART_LCR_DLAB_EN

◆ UART_LCR_NO_PARITY

◆ UART_LCR_ONE_STOPBIT

◆ UART_LCR_PARITY_EN

◆ UART_LCR_PARITY_EVEN

◆ UART_LCR_PARITY_ODD

◆ UART_LCR_PARITY_SP_0

◆ UART_LCR_PARITY_SP_1

◆ UART_LCR_TWO_STOPBIT

◆ UART_LCR_WLEN5

◆ UART_LCR_WLEN6

◆ UART_LCR_WLEN7

◆ UART_LCR_WLEN8

◆ UART_LOAD_DLL

◆ UART_LOAD_DLM

◆ UART_LSR

◆ UART_LSR_BI

◆ UART_LSR_BITMASK

◆ UART_LSR_ERROR_MASK

| #define UART_LSR_ERROR_MASK (UART_LSR_OE | UART_LSR_PE | UART_LSR_FE | UART_LSR_BI | UART_LSR_RXFE) |

◆ UART_LSR_FE

◆ UART_LSR_OE

◆ UART_LSR_PE

◆ UART_LSR_RDR

◆ UART_LSR_RXFE

◆ UART_LSR_TEMT

◆ UART_LSR_THRE

◆ UART_OSR

◆ UART_RBR

◆ UART_RBR_MASKBIT

◆ UART_RS485ADRMATCH

◆ UART_RS485CTRL

◆ UART_RS485DLY

◆ UART_SCICTRL

◆ UART_SCICTRL_GUARDTIME

| #define UART_SCICTRL_GUARDTIME | ( | n | ) | ((uint32_t)(((n)&0xFF)<<8)) |

◆ UART_SCICTRL_NACKDIS

◆ UART_SCICTRL_PROTSEL_T1

◆ UART_SCICTRL_SCIEN

◆ UART_SCICTRL_TXRETRY

| #define UART_SCICTRL_TXRETRY | ( | n | ) | ((uint32_t)(((n)&0x07)<<5)) |

◆ UART_SCR_BIMASK

◆ UART_SYNCCTRL

◆ UART_SYNCCTRL_CCCLR

◆ UART_SYNCCTRL_CSCEN

◆ UART_SYNCCTRL_CSRC_MASTER

◆ UART_SYNCCTRL_FES

◆ UART_SYNCCTRL_NOSTARTSTOP

◆ UART_SYNCCTRL_SYNC

◆ UART_SYNCCTRL_TSBYPASS

◆ UART_TER

◆ UART_TER_TXEN

◆ UART_THR

◆ UART_THR_MASKBIT

◆ UART_TX_FIFO_SIZE

Enumeration Type Documentation

◆ uart_databit_t

| enum uart_databit_t |

◆ uart_error_t

| enum uart_error_t |

◆ uart_num_t

| enum uart_num_t |

◆ uart_parity_t

| enum uart_parity_t |

◆ uart_rx_data_ready_t

| enum uart_rx_data_ready_t |

◆ uart_stopbit_t

| enum uart_stopbit_t |

Function Documentation

◆ uart_init()

| void uart_init | ( | uart_num_t | uart_num, |

| uart_databit_t | data_nb_bits, | ||

| uart_stopbit_t | data_nb_stop, | ||

| uart_parity_t | data_parity, | ||

| uint16_t | uart_divisor, | ||

| uint8_t | uart_divaddval, | ||

| uint8_t | uart_mulval | ||

| ) |

◆ uart_read()

| uint8_t uart_read | ( | uart_num_t | uart_num | ) |

◆ uart_read_timeout()

| uint8_t uart_read_timeout | ( | uart_num_t | uart_num, |

| uint32_t | rx_timeout_nb_cycles, | ||

| uart_error_t * | error | ||

| ) |

◆ uart_rx_data_ready()

| uart_rx_data_ready_t uart_rx_data_ready | ( | uart_num_t | uart_num | ) |

◆ uart_write()

| void uart_write | ( | uart_num_t | uart_num, |

| uint8_t | data | ||

| ) |