usb.h File Reference

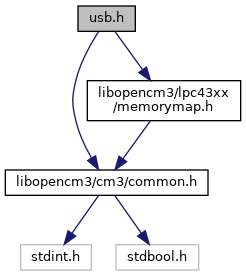

Include dependency graph for usb.h:

Go to the source code of this file.

Data Structures | |

| struct | usb_transfer_descriptor_t |

| struct | usb_queue_head_t |

Typedefs | |

| typedef struct usb_transfer_descriptor_t | usb_transfer_descriptor_t |

Macro Definition Documentation

◆ BIT_ARG

◆ BIT_MASK

| #define BIT_MASK | ( | base_name | ) | (((1 << base_name##_WIDTH) - 1) << base_name##_SHIFT) |

◆ USB0_ASYNCLISTADDR

◆ USB0_ASYNCLISTADDR_ASYBASE31_5

| #define USB0_ASYNCLISTADDR_ASYBASE31_5 | ( | x | ) | ((x) << USB0_ASYNCLISTADDR_ASYBASE31_5_SHIFT) |

◆ USB0_ASYNCLISTADDR_ASYBASE31_5_MASK

| #define USB0_ASYNCLISTADDR_ASYBASE31_5_MASK (0x7ffffff << USB0_ASYNCLISTADDR_ASYBASE31_5_SHIFT) |

◆ USB0_ASYNCLISTADDR_ASYBASE31_5_SHIFT

◆ USB0_BINTERVAL

◆ USB0_BINTERVAL_BINT

| #define USB0_BINTERVAL_BINT | ( | x | ) | ((x) << USB0_BINTERVAL_BINT_SHIFT) |

◆ USB0_BINTERVAL_BINT_MASK

| #define USB0_BINTERVAL_BINT_MASK (0xf << USB0_BINTERVAL_BINT_SHIFT) |

◆ USB0_BINTERVAL_BINT_SHIFT

◆ USB0_BURSTSIZE

◆ USB0_BURSTSIZE_RXPBURST

| #define USB0_BURSTSIZE_RXPBURST | ( | x | ) | ((x) << USB0_BURSTSIZE_RXPBURST_SHIFT) |

◆ USB0_BURSTSIZE_RXPBURST_MASK

| #define USB0_BURSTSIZE_RXPBURST_MASK (0xff << USB0_BURSTSIZE_RXPBURST_SHIFT) |

◆ USB0_BURSTSIZE_RXPBURST_SHIFT

◆ USB0_BURSTSIZE_TXPBURST

| #define USB0_BURSTSIZE_TXPBURST | ( | x | ) | ((x) << USB0_BURSTSIZE_TXPBURST_SHIFT) |

◆ USB0_BURSTSIZE_TXPBURST_MASK

| #define USB0_BURSTSIZE_TXPBURST_MASK (0xff << USB0_BURSTSIZE_TXPBURST_SHIFT) |

◆ USB0_BURSTSIZE_TXPBURST_SHIFT

◆ USB0_CAPLENGTH

◆ USB0_CAPLENGTH_CAPLENGTH

| #define USB0_CAPLENGTH_CAPLENGTH | ( | x | ) | ((x) << USB0_CAPLENGTH_CAPLENGTH_SHIFT) |

◆ USB0_CAPLENGTH_CAPLENGTH_MASK

| #define USB0_CAPLENGTH_CAPLENGTH_MASK (0xff << USB0_CAPLENGTH_CAPLENGTH_SHIFT) |

◆ USB0_CAPLENGTH_CAPLENGTH_SHIFT

◆ USB0_CAPLENGTH_HCIVERSION

| #define USB0_CAPLENGTH_HCIVERSION | ( | x | ) | ((x) << USB0_CAPLENGTH_HCIVERSION_SHIFT) |

◆ USB0_CAPLENGTH_HCIVERSION_MASK

| #define USB0_CAPLENGTH_HCIVERSION_MASK (0xffff << USB0_CAPLENGTH_HCIVERSION_SHIFT) |

◆ USB0_CAPLENGTH_HCIVERSION_SHIFT

◆ USB0_DCCPARAMS

◆ USB0_DCCPARAMS_DC

| #define USB0_DCCPARAMS_DC (1 << USB0_DCCPARAMS_DC_SHIFT) |

◆ USB0_DCCPARAMS_DC_SHIFT

◆ USB0_DCCPARAMS_DEN

| #define USB0_DCCPARAMS_DEN | ( | x | ) | ((x) << USB0_DCCPARAMS_DEN_SHIFT) |

◆ USB0_DCCPARAMS_DEN_MASK

| #define USB0_DCCPARAMS_DEN_MASK (0x1f << USB0_DCCPARAMS_DEN_SHIFT) |

◆ USB0_DCCPARAMS_DEN_SHIFT

◆ USB0_DCCPARAMS_HC

| #define USB0_DCCPARAMS_HC (1 << USB0_DCCPARAMS_HC_SHIFT) |

◆ USB0_DCCPARAMS_HC_SHIFT

◆ USB0_DCIVERSION

◆ USB0_DEVICEADDR

◆ USB0_DEVICEADDR_USBADR

| #define USB0_DEVICEADDR_USBADR | ( | x | ) | ((x) << USB0_DEVICEADDR_USBADR_SHIFT) |

◆ USB0_DEVICEADDR_USBADR_MASK

| #define USB0_DEVICEADDR_USBADR_MASK (0x7f << USB0_DEVICEADDR_USBADR_SHIFT) |

◆ USB0_DEVICEADDR_USBADR_SHIFT

◆ USB0_DEVICEADDR_USBADRA

| #define USB0_DEVICEADDR_USBADRA (1 << USB0_DEVICEADDR_USBADRA_SHIFT) |

◆ USB0_DEVICEADDR_USBADRA_SHIFT

◆ USB0_ENDPOINTLISTADDR

◆ USB0_ENDPOINTLISTADDR_EPBASE31_11

| #define USB0_ENDPOINTLISTADDR_EPBASE31_11 | ( | x | ) | ((x) << USB0_ENDPOINTLISTADDR_EPBASE31_11_SHIFT) |

◆ USB0_ENDPOINTLISTADDR_EPBASE31_11_MASK

| #define USB0_ENDPOINTLISTADDR_EPBASE31_11_MASK (0x1fffff << USB0_ENDPOINTLISTADDR_EPBASE31_11_SHIFT) |

◆ USB0_ENDPOINTLISTADDR_EPBASE31_11_SHIFT

◆ USB0_ENDPTCOMPLETE

◆ USB0_ENDPTCOMPLETE_ERCE

| #define USB0_ENDPTCOMPLETE_ERCE | ( | x | ) | ((x) << USB0_ENDPTCOMPLETE_ERCE_SHIFT) |

◆ USB0_ENDPTCOMPLETE_ERCE_MASK

| #define USB0_ENDPTCOMPLETE_ERCE_MASK (0x3f << USB0_ENDPTCOMPLETE_ERCE_SHIFT) |

◆ USB0_ENDPTCOMPLETE_ERCE_SHIFT

◆ USB0_ENDPTCOMPLETE_ETCE

| #define USB0_ENDPTCOMPLETE_ETCE | ( | x | ) | ((x) << USB0_ENDPTCOMPLETE_ETCE_SHIFT) |

◆ USB0_ENDPTCOMPLETE_ETCE_MASK

| #define USB0_ENDPTCOMPLETE_ETCE_MASK (0x3f << USB0_ENDPTCOMPLETE_ETCE_SHIFT) |

◆ USB0_ENDPTCOMPLETE_ETCE_SHIFT

◆ USB0_ENDPTCTRL

| #define USB0_ENDPTCTRL | ( | logical_ep | ) |

Value:

((logical_ep) * 4))

◆ USB0_ENDPTCTRL0

| #define USB0_ENDPTCTRL0 USB0_ENDPTCTRL(0) |

◆ USB0_ENDPTCTRL0_RXE

| #define USB0_ENDPTCTRL0_RXE (1 << USB0_ENDPTCTRL0_RXE_SHIFT) |

◆ USB0_ENDPTCTRL0_RXE_SHIFT

◆ USB0_ENDPTCTRL0_RXS

| #define USB0_ENDPTCTRL0_RXS (1 << USB0_ENDPTCTRL0_RXS_SHIFT) |

◆ USB0_ENDPTCTRL0_RXS_SHIFT

◆ USB0_ENDPTCTRL0_RXT1_0

| #define USB0_ENDPTCTRL0_RXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL0_RXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL0_RXT1_0_MASK

| #define USB0_ENDPTCTRL0_RXT1_0_MASK (0x3 << USB0_ENDPTCTRL0_RXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL0_RXT1_0_SHIFT

◆ USB0_ENDPTCTRL0_TXE

| #define USB0_ENDPTCTRL0_TXE (1 << USB0_ENDPTCTRL0_TXE_SHIFT) |

◆ USB0_ENDPTCTRL0_TXE_SHIFT

◆ USB0_ENDPTCTRL0_TXS

| #define USB0_ENDPTCTRL0_TXS (1 << USB0_ENDPTCTRL0_TXS_SHIFT) |

◆ USB0_ENDPTCTRL0_TXS_SHIFT

◆ USB0_ENDPTCTRL0_TXT1_0

| #define USB0_ENDPTCTRL0_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL0_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL0_TXT1_0_MASK

| #define USB0_ENDPTCTRL0_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL0_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL0_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL1

| #define USB0_ENDPTCTRL1 USB0_ENDPTCTRL(1) |

◆ USB0_ENDPTCTRL1_RXE

| #define USB0_ENDPTCTRL1_RXE (1 << USB0_ENDPTCTRL1_RXE_SHIFT) |

◆ USB0_ENDPTCTRL1_RXE_SHIFT

◆ USB0_ENDPTCTRL1_RXI

| #define USB0_ENDPTCTRL1_RXI (1 << USB0_ENDPTCTRL1_RXI_SHIFT) |

◆ USB0_ENDPTCTRL1_RXI_SHIFT

◆ USB0_ENDPTCTRL1_RXR

| #define USB0_ENDPTCTRL1_RXR (1 << USB0_ENDPTCTRL1_RXR_SHIFT) |

◆ USB0_ENDPTCTRL1_RXR_SHIFT

◆ USB0_ENDPTCTRL1_RXS

| #define USB0_ENDPTCTRL1_RXS (1 << USB0_ENDPTCTRL1_RXS_SHIFT) |

◆ USB0_ENDPTCTRL1_RXS_SHIFT

◆ USB0_ENDPTCTRL1_RXT

| #define USB0_ENDPTCTRL1_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL1_RXT_SHIFT) |

◆ USB0_ENDPTCTRL1_RXT_MASK

| #define USB0_ENDPTCTRL1_RXT_MASK (0x3 << USB0_ENDPTCTRL1_RXT_SHIFT) |

◆ USB0_ENDPTCTRL1_RXT_SHIFT

◆ USB0_ENDPTCTRL1_TXE

| #define USB0_ENDPTCTRL1_TXE (1 << USB0_ENDPTCTRL1_TXE_SHIFT) |

◆ USB0_ENDPTCTRL1_TXE_SHIFT

◆ USB0_ENDPTCTRL1_TXI

| #define USB0_ENDPTCTRL1_TXI (1 << USB0_ENDPTCTRL1_TXI_SHIFT) |

◆ USB0_ENDPTCTRL1_TXI_SHIFT

◆ USB0_ENDPTCTRL1_TXR

| #define USB0_ENDPTCTRL1_TXR (1 << USB0_ENDPTCTRL1_TXR_SHIFT) |

◆ USB0_ENDPTCTRL1_TXR_SHIFT

◆ USB0_ENDPTCTRL1_TXS

| #define USB0_ENDPTCTRL1_TXS (1 << USB0_ENDPTCTRL1_TXS_SHIFT) |

◆ USB0_ENDPTCTRL1_TXS_SHIFT

◆ USB0_ENDPTCTRL1_TXT1_0

| #define USB0_ENDPTCTRL1_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL1_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL1_TXT1_0_MASK

| #define USB0_ENDPTCTRL1_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL1_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL1_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL2

| #define USB0_ENDPTCTRL2 USB0_ENDPTCTRL(2) |

◆ USB0_ENDPTCTRL2_RXE

| #define USB0_ENDPTCTRL2_RXE (1 << USB0_ENDPTCTRL2_RXE_SHIFT) |

◆ USB0_ENDPTCTRL2_RXE_SHIFT

◆ USB0_ENDPTCTRL2_RXI

| #define USB0_ENDPTCTRL2_RXI (1 << USB0_ENDPTCTRL2_RXI_SHIFT) |

◆ USB0_ENDPTCTRL2_RXI_SHIFT

◆ USB0_ENDPTCTRL2_RXR

| #define USB0_ENDPTCTRL2_RXR (1 << USB0_ENDPTCTRL2_RXR_SHIFT) |

◆ USB0_ENDPTCTRL2_RXR_SHIFT

◆ USB0_ENDPTCTRL2_RXS

| #define USB0_ENDPTCTRL2_RXS (1 << USB0_ENDPTCTRL2_RXS_SHIFT) |

◆ USB0_ENDPTCTRL2_RXS_SHIFT

◆ USB0_ENDPTCTRL2_RXT

| #define USB0_ENDPTCTRL2_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL2_RXT_SHIFT) |

◆ USB0_ENDPTCTRL2_RXT_MASK

| #define USB0_ENDPTCTRL2_RXT_MASK (0x3 << USB0_ENDPTCTRL2_RXT_SHIFT) |

◆ USB0_ENDPTCTRL2_RXT_SHIFT

◆ USB0_ENDPTCTRL2_TXE

| #define USB0_ENDPTCTRL2_TXE (1 << USB0_ENDPTCTRL2_TXE_SHIFT) |

◆ USB0_ENDPTCTRL2_TXE_SHIFT

◆ USB0_ENDPTCTRL2_TXI

| #define USB0_ENDPTCTRL2_TXI (1 << USB0_ENDPTCTRL2_TXI_SHIFT) |

◆ USB0_ENDPTCTRL2_TXI_SHIFT

◆ USB0_ENDPTCTRL2_TXR

| #define USB0_ENDPTCTRL2_TXR (1 << USB0_ENDPTCTRL2_TXR_SHIFT) |

◆ USB0_ENDPTCTRL2_TXR_SHIFT

◆ USB0_ENDPTCTRL2_TXS

| #define USB0_ENDPTCTRL2_TXS (1 << USB0_ENDPTCTRL2_TXS_SHIFT) |

◆ USB0_ENDPTCTRL2_TXS_SHIFT

◆ USB0_ENDPTCTRL2_TXT1_0

| #define USB0_ENDPTCTRL2_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL2_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL2_TXT1_0_MASK

| #define USB0_ENDPTCTRL2_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL2_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL2_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL3

| #define USB0_ENDPTCTRL3 USB0_ENDPTCTRL(3) |

◆ USB0_ENDPTCTRL3_RXE

| #define USB0_ENDPTCTRL3_RXE (1 << USB0_ENDPTCTRL3_RXE_SHIFT) |

◆ USB0_ENDPTCTRL3_RXE_SHIFT

◆ USB0_ENDPTCTRL3_RXI

| #define USB0_ENDPTCTRL3_RXI (1 << USB0_ENDPTCTRL3_RXI_SHIFT) |

◆ USB0_ENDPTCTRL3_RXI_SHIFT

◆ USB0_ENDPTCTRL3_RXR

| #define USB0_ENDPTCTRL3_RXR (1 << USB0_ENDPTCTRL3_RXR_SHIFT) |

◆ USB0_ENDPTCTRL3_RXR_SHIFT

◆ USB0_ENDPTCTRL3_RXS

| #define USB0_ENDPTCTRL3_RXS (1 << USB0_ENDPTCTRL3_RXS_SHIFT) |

◆ USB0_ENDPTCTRL3_RXS_SHIFT

◆ USB0_ENDPTCTRL3_RXT

| #define USB0_ENDPTCTRL3_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL3_RXT_SHIFT) |

◆ USB0_ENDPTCTRL3_RXT_MASK

| #define USB0_ENDPTCTRL3_RXT_MASK (0x3 << USB0_ENDPTCTRL3_RXT_SHIFT) |

◆ USB0_ENDPTCTRL3_RXT_SHIFT

◆ USB0_ENDPTCTRL3_TXE

| #define USB0_ENDPTCTRL3_TXE (1 << USB0_ENDPTCTRL3_TXE_SHIFT) |

◆ USB0_ENDPTCTRL3_TXE_SHIFT

◆ USB0_ENDPTCTRL3_TXI

| #define USB0_ENDPTCTRL3_TXI (1 << USB0_ENDPTCTRL3_TXI_SHIFT) |

◆ USB0_ENDPTCTRL3_TXI_SHIFT

◆ USB0_ENDPTCTRL3_TXR

| #define USB0_ENDPTCTRL3_TXR (1 << USB0_ENDPTCTRL3_TXR_SHIFT) |

◆ USB0_ENDPTCTRL3_TXR_SHIFT

◆ USB0_ENDPTCTRL3_TXS

| #define USB0_ENDPTCTRL3_TXS (1 << USB0_ENDPTCTRL3_TXS_SHIFT) |

◆ USB0_ENDPTCTRL3_TXS_SHIFT

◆ USB0_ENDPTCTRL3_TXT1_0

| #define USB0_ENDPTCTRL3_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL3_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL3_TXT1_0_MASK

| #define USB0_ENDPTCTRL3_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL3_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL3_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL4

| #define USB0_ENDPTCTRL4 USB0_ENDPTCTRL(4) |

◆ USB0_ENDPTCTRL4_RXE

| #define USB0_ENDPTCTRL4_RXE (1 << USB0_ENDPTCTRL4_RXE_SHIFT) |

◆ USB0_ENDPTCTRL4_RXE_SHIFT

◆ USB0_ENDPTCTRL4_RXI

| #define USB0_ENDPTCTRL4_RXI (1 << USB0_ENDPTCTRL4_RXI_SHIFT) |

◆ USB0_ENDPTCTRL4_RXI_SHIFT

◆ USB0_ENDPTCTRL4_RXR

| #define USB0_ENDPTCTRL4_RXR (1 << USB0_ENDPTCTRL4_RXR_SHIFT) |

◆ USB0_ENDPTCTRL4_RXR_SHIFT

◆ USB0_ENDPTCTRL4_RXS

| #define USB0_ENDPTCTRL4_RXS (1 << USB0_ENDPTCTRL4_RXS_SHIFT) |

◆ USB0_ENDPTCTRL4_RXS_SHIFT

◆ USB0_ENDPTCTRL4_RXT

| #define USB0_ENDPTCTRL4_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL4_RXT_SHIFT) |

◆ USB0_ENDPTCTRL4_RXT_MASK

| #define USB0_ENDPTCTRL4_RXT_MASK (0x3 << USB0_ENDPTCTRL4_RXT_SHIFT) |

◆ USB0_ENDPTCTRL4_RXT_SHIFT

◆ USB0_ENDPTCTRL4_TXE

| #define USB0_ENDPTCTRL4_TXE (1 << USB0_ENDPTCTRL4_TXE_SHIFT) |

◆ USB0_ENDPTCTRL4_TXE_SHIFT

◆ USB0_ENDPTCTRL4_TXI

| #define USB0_ENDPTCTRL4_TXI (1 << USB0_ENDPTCTRL4_TXI_SHIFT) |

◆ USB0_ENDPTCTRL4_TXI_SHIFT

◆ USB0_ENDPTCTRL4_TXR

| #define USB0_ENDPTCTRL4_TXR (1 << USB0_ENDPTCTRL4_TXR_SHIFT) |

◆ USB0_ENDPTCTRL4_TXR_SHIFT

◆ USB0_ENDPTCTRL4_TXS

| #define USB0_ENDPTCTRL4_TXS (1 << USB0_ENDPTCTRL4_TXS_SHIFT) |

◆ USB0_ENDPTCTRL4_TXS_SHIFT

◆ USB0_ENDPTCTRL4_TXT1_0

| #define USB0_ENDPTCTRL4_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL4_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL4_TXT1_0_MASK

| #define USB0_ENDPTCTRL4_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL4_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL4_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL5

| #define USB0_ENDPTCTRL5 USB0_ENDPTCTRL(5) |

◆ USB0_ENDPTCTRL5_RXE

| #define USB0_ENDPTCTRL5_RXE (1 << USB0_ENDPTCTRL5_RXE_SHIFT) |

◆ USB0_ENDPTCTRL5_RXE_SHIFT

◆ USB0_ENDPTCTRL5_RXI

| #define USB0_ENDPTCTRL5_RXI (1 << USB0_ENDPTCTRL5_RXI_SHIFT) |

◆ USB0_ENDPTCTRL5_RXI_SHIFT

◆ USB0_ENDPTCTRL5_RXR

| #define USB0_ENDPTCTRL5_RXR (1 << USB0_ENDPTCTRL5_RXR_SHIFT) |

◆ USB0_ENDPTCTRL5_RXR_SHIFT

◆ USB0_ENDPTCTRL5_RXS

| #define USB0_ENDPTCTRL5_RXS (1 << USB0_ENDPTCTRL5_RXS_SHIFT) |

◆ USB0_ENDPTCTRL5_RXS_SHIFT

◆ USB0_ENDPTCTRL5_RXT

| #define USB0_ENDPTCTRL5_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL5_RXT_SHIFT) |

◆ USB0_ENDPTCTRL5_RXT_MASK

| #define USB0_ENDPTCTRL5_RXT_MASK (0x3 << USB0_ENDPTCTRL5_RXT_SHIFT) |

◆ USB0_ENDPTCTRL5_RXT_SHIFT

◆ USB0_ENDPTCTRL5_TXE

| #define USB0_ENDPTCTRL5_TXE (1 << USB0_ENDPTCTRL5_TXE_SHIFT) |

◆ USB0_ENDPTCTRL5_TXE_SHIFT

◆ USB0_ENDPTCTRL5_TXI

| #define USB0_ENDPTCTRL5_TXI (1 << USB0_ENDPTCTRL5_TXI_SHIFT) |

◆ USB0_ENDPTCTRL5_TXI_SHIFT

◆ USB0_ENDPTCTRL5_TXR

| #define USB0_ENDPTCTRL5_TXR (1 << USB0_ENDPTCTRL5_TXR_SHIFT) |

◆ USB0_ENDPTCTRL5_TXR_SHIFT

◆ USB0_ENDPTCTRL5_TXS

| #define USB0_ENDPTCTRL5_TXS (1 << USB0_ENDPTCTRL5_TXS_SHIFT) |

◆ USB0_ENDPTCTRL5_TXS_SHIFT

◆ USB0_ENDPTCTRL5_TXT1_0

| #define USB0_ENDPTCTRL5_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL5_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL5_TXT1_0_MASK

| #define USB0_ENDPTCTRL5_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL5_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL5_TXT1_0_SHIFT

◆ USB0_ENDPTCTRL_RXE

| #define USB0_ENDPTCTRL_RXE (1 << USB0_ENDPTCTRL_RXE_SHIFT) |

◆ USB0_ENDPTCTRL_RXE_SHIFT

◆ USB0_ENDPTCTRL_RXI

| #define USB0_ENDPTCTRL_RXI (1 << USB0_ENDPTCTRL_RXI_SHIFT) |

◆ USB0_ENDPTCTRL_RXI_SHIFT

◆ USB0_ENDPTCTRL_RXR

| #define USB0_ENDPTCTRL_RXR (1 << USB0_ENDPTCTRL_RXR_SHIFT) |

◆ USB0_ENDPTCTRL_RXR_SHIFT

◆ USB0_ENDPTCTRL_RXS

| #define USB0_ENDPTCTRL_RXS (1 << USB0_ENDPTCTRL_RXS_SHIFT) |

◆ USB0_ENDPTCTRL_RXS_SHIFT

◆ USB0_ENDPTCTRL_RXT

| #define USB0_ENDPTCTRL_RXT | ( | x | ) | ((x) << USB0_ENDPTCTRL_RXT_SHIFT) |

◆ USB0_ENDPTCTRL_RXT_MASK

| #define USB0_ENDPTCTRL_RXT_MASK (0x3 << USB0_ENDPTCTRL_RXT_SHIFT) |

◆ USB0_ENDPTCTRL_RXT_SHIFT

◆ USB0_ENDPTCTRL_TXE

| #define USB0_ENDPTCTRL_TXE (1 << USB0_ENDPTCTRL_TXE_SHIFT) |

◆ USB0_ENDPTCTRL_TXE_SHIFT

◆ USB0_ENDPTCTRL_TXI

| #define USB0_ENDPTCTRL_TXI (1 << USB0_ENDPTCTRL_TXI_SHIFT) |

◆ USB0_ENDPTCTRL_TXI_SHIFT

◆ USB0_ENDPTCTRL_TXR

| #define USB0_ENDPTCTRL_TXR (1 << USB0_ENDPTCTRL_TXR_SHIFT) |

◆ USB0_ENDPTCTRL_TXR_SHIFT

◆ USB0_ENDPTCTRL_TXS

| #define USB0_ENDPTCTRL_TXS (1 << USB0_ENDPTCTRL_TXS_SHIFT) |

◆ USB0_ENDPTCTRL_TXS_SHIFT

◆ USB0_ENDPTCTRL_TXT1_0

| #define USB0_ENDPTCTRL_TXT1_0 | ( | x | ) | ((x) << USB0_ENDPTCTRL_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL_TXT1_0_MASK

| #define USB0_ENDPTCTRL_TXT1_0_MASK (0x3 << USB0_ENDPTCTRL_TXT1_0_SHIFT) |

◆ USB0_ENDPTCTRL_TXT1_0_SHIFT

◆ USB0_ENDPTFLUSH

◆ USB0_ENDPTFLUSH_FERB

| #define USB0_ENDPTFLUSH_FERB | ( | x | ) | ((x) << USB0_ENDPTFLUSH_FERB_SHIFT) |

◆ USB0_ENDPTFLUSH_FERB_MASK

| #define USB0_ENDPTFLUSH_FERB_MASK (0x3f << USB0_ENDPTFLUSH_FERB_SHIFT) |

◆ USB0_ENDPTFLUSH_FERB_SHIFT

◆ USB0_ENDPTFLUSH_FETB

| #define USB0_ENDPTFLUSH_FETB | ( | x | ) | ((x) << USB0_ENDPTFLUSH_FETB_SHIFT) |

◆ USB0_ENDPTFLUSH_FETB_MASK

| #define USB0_ENDPTFLUSH_FETB_MASK (0x3f << USB0_ENDPTFLUSH_FETB_SHIFT) |

◆ USB0_ENDPTFLUSH_FETB_SHIFT

◆ USB0_ENDPTNAK

◆ USB0_ENDPTNAK_EPRN

| #define USB0_ENDPTNAK_EPRN | ( | x | ) | ((x) << USB0_ENDPTNAK_EPRN_SHIFT) |

◆ USB0_ENDPTNAK_EPRN_MASK

| #define USB0_ENDPTNAK_EPRN_MASK (0x3f << USB0_ENDPTNAK_EPRN_SHIFT) |

◆ USB0_ENDPTNAK_EPRN_SHIFT

◆ USB0_ENDPTNAK_EPTN

| #define USB0_ENDPTNAK_EPTN | ( | x | ) | ((x) << USB0_ENDPTNAK_EPTN_SHIFT) |

◆ USB0_ENDPTNAK_EPTN_MASK

| #define USB0_ENDPTNAK_EPTN_MASK (0x3f << USB0_ENDPTNAK_EPTN_SHIFT) |

◆ USB0_ENDPTNAK_EPTN_SHIFT

◆ USB0_ENDPTNAKEN

◆ USB0_ENDPTNAKEN_EPRNE

| #define USB0_ENDPTNAKEN_EPRNE | ( | x | ) | ((x) << USB0_ENDPTNAKEN_EPRNE_SHIFT) |

◆ USB0_ENDPTNAKEN_EPRNE_MASK

| #define USB0_ENDPTNAKEN_EPRNE_MASK (0x3f << USB0_ENDPTNAKEN_EPRNE_SHIFT) |

◆ USB0_ENDPTNAKEN_EPRNE_SHIFT

◆ USB0_ENDPTNAKEN_EPTNE

| #define USB0_ENDPTNAKEN_EPTNE | ( | x | ) | ((x) << USB0_ENDPTNAKEN_EPTNE_SHIFT) |

◆ USB0_ENDPTNAKEN_EPTNE_MASK

| #define USB0_ENDPTNAKEN_EPTNE_MASK (0x3f << USB0_ENDPTNAKEN_EPTNE_SHIFT) |

◆ USB0_ENDPTNAKEN_EPTNE_SHIFT

◆ USB0_ENDPTPRIME

◆ USB0_ENDPTPRIME_PERB

| #define USB0_ENDPTPRIME_PERB | ( | x | ) | ((x) << USB0_ENDPTPRIME_PERB_SHIFT) |

◆ USB0_ENDPTPRIME_PERB_MASK

| #define USB0_ENDPTPRIME_PERB_MASK (0x3f << USB0_ENDPTPRIME_PERB_SHIFT) |

◆ USB0_ENDPTPRIME_PERB_SHIFT

◆ USB0_ENDPTPRIME_PETB

| #define USB0_ENDPTPRIME_PETB | ( | x | ) | ((x) << USB0_ENDPTPRIME_PETB_SHIFT) |

◆ USB0_ENDPTPRIME_PETB_MASK

| #define USB0_ENDPTPRIME_PETB_MASK (0x3f << USB0_ENDPTPRIME_PETB_SHIFT) |

◆ USB0_ENDPTPRIME_PETB_SHIFT

◆ USB0_ENDPTSETUPSTAT

◆ USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT

| #define USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT | ( | x | ) | ((x) << USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT_SHIFT) |

◆ USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT_MASK

| #define USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT_MASK (0x3f << USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT_SHIFT) |

◆ USB0_ENDPTSETUPSTAT_ENDPTSETUPSTAT_SHIFT

◆ USB0_ENDPTSTAT

◆ USB0_ENDPTSTAT_ERBR

| #define USB0_ENDPTSTAT_ERBR | ( | x | ) | ((x) << USB0_ENDPTSTAT_ERBR_SHIFT) |

◆ USB0_ENDPTSTAT_ERBR_MASK

| #define USB0_ENDPTSTAT_ERBR_MASK (0x3f << USB0_ENDPTSTAT_ERBR_SHIFT) |

◆ USB0_ENDPTSTAT_ERBR_SHIFT

◆ USB0_ENDPTSTAT_ETBR

| #define USB0_ENDPTSTAT_ETBR | ( | x | ) | ((x) << USB0_ENDPTSTAT_ETBR_SHIFT) |

◆ USB0_ENDPTSTAT_ETBR_MASK

| #define USB0_ENDPTSTAT_ETBR_MASK (0x3f << USB0_ENDPTSTAT_ETBR_SHIFT) |

◆ USB0_ENDPTSTAT_ETBR_SHIFT

◆ USB0_FRINDEX_D

◆ USB0_FRINDEX_D_FRINDEX13_3

| #define USB0_FRINDEX_D_FRINDEX13_3 | ( | x | ) | ((x) << USB0_FRINDEX_D_FRINDEX13_3_SHIFT) |

◆ USB0_FRINDEX_D_FRINDEX13_3_MASK

| #define USB0_FRINDEX_D_FRINDEX13_3_MASK (0x7ff << USB0_FRINDEX_D_FRINDEX13_3_SHIFT) |

◆ USB0_FRINDEX_D_FRINDEX13_3_SHIFT

◆ USB0_FRINDEX_D_FRINDEX2_0

| #define USB0_FRINDEX_D_FRINDEX2_0 | ( | x | ) | ((x) << USB0_FRINDEX_D_FRINDEX2_0_SHIFT) |

◆ USB0_FRINDEX_D_FRINDEX2_0_MASK

| #define USB0_FRINDEX_D_FRINDEX2_0_MASK (0x7 << USB0_FRINDEX_D_FRINDEX2_0_SHIFT) |

◆ USB0_FRINDEX_D_FRINDEX2_0_SHIFT

◆ USB0_FRINDEX_H

◆ USB0_FRINDEX_H_FRINDEX12_3

| #define USB0_FRINDEX_H_FRINDEX12_3 | ( | x | ) | ((x) << USB0_FRINDEX_H_FRINDEX12_3_SHIFT) |

◆ USB0_FRINDEX_H_FRINDEX12_3_MASK

| #define USB0_FRINDEX_H_FRINDEX12_3_MASK (0x3ff << USB0_FRINDEX_H_FRINDEX12_3_SHIFT) |

◆ USB0_FRINDEX_H_FRINDEX12_3_SHIFT

◆ USB0_FRINDEX_H_FRINDEX2_0

| #define USB0_FRINDEX_H_FRINDEX2_0 | ( | x | ) | ((x) << USB0_FRINDEX_H_FRINDEX2_0_SHIFT) |

◆ USB0_FRINDEX_H_FRINDEX2_0_MASK

| #define USB0_FRINDEX_H_FRINDEX2_0_MASK (0x7 << USB0_FRINDEX_H_FRINDEX2_0_SHIFT) |

◆ USB0_FRINDEX_H_FRINDEX2_0_SHIFT

◆ USB0_HCCPARAMS

◆ USB0_HCCPARAMS_ADC

| #define USB0_HCCPARAMS_ADC (1 << USB0_HCCPARAMS_ADC_SHIFT) |

◆ USB0_HCCPARAMS_ADC_SHIFT

◆ USB0_HCCPARAMS_ASP

| #define USB0_HCCPARAMS_ASP (1 << USB0_HCCPARAMS_ASP_SHIFT) |

◆ USB0_HCCPARAMS_ASP_SHIFT

◆ USB0_HCCPARAMS_EECP

| #define USB0_HCCPARAMS_EECP | ( | x | ) | ((x) << USB0_HCCPARAMS_EECP_SHIFT) |

◆ USB0_HCCPARAMS_EECP_MASK

| #define USB0_HCCPARAMS_EECP_MASK (0xf << USB0_HCCPARAMS_EECP_SHIFT) |

◆ USB0_HCCPARAMS_EECP_SHIFT

◆ USB0_HCCPARAMS_IST

| #define USB0_HCCPARAMS_IST | ( | x | ) | ((x) << USB0_HCCPARAMS_IST_SHIFT) |

◆ USB0_HCCPARAMS_IST_MASK

| #define USB0_HCCPARAMS_IST_MASK (0xf << USB0_HCCPARAMS_IST_SHIFT) |

◆ USB0_HCCPARAMS_IST_SHIFT

◆ USB0_HCCPARAMS_PFL

| #define USB0_HCCPARAMS_PFL (1 << USB0_HCCPARAMS_PFL_SHIFT) |

◆ USB0_HCCPARAMS_PFL_SHIFT

◆ USB0_HCSPARAMS

◆ USB0_HCSPARAMS_N_CC

| #define USB0_HCSPARAMS_N_CC | ( | x | ) | ((x) << USB0_HCSPARAMS_N_CC_SHIFT) |

◆ USB0_HCSPARAMS_N_CC_MASK

| #define USB0_HCSPARAMS_N_CC_MASK (0xf << USB0_HCSPARAMS_N_CC_SHIFT) |

◆ USB0_HCSPARAMS_N_CC_SHIFT

◆ USB0_HCSPARAMS_N_PCC

| #define USB0_HCSPARAMS_N_PCC | ( | x | ) | ((x) << USB0_HCSPARAMS_N_PCC_SHIFT) |

◆ USB0_HCSPARAMS_N_PCC_MASK

| #define USB0_HCSPARAMS_N_PCC_MASK (0xf << USB0_HCSPARAMS_N_PCC_SHIFT) |

◆ USB0_HCSPARAMS_N_PCC_SHIFT

◆ USB0_HCSPARAMS_N_PORTS

| #define USB0_HCSPARAMS_N_PORTS | ( | x | ) | ((x) << USB0_HCSPARAMS_N_PORTS_SHIFT) |

◆ USB0_HCSPARAMS_N_PORTS_MASK

| #define USB0_HCSPARAMS_N_PORTS_MASK (0xf << USB0_HCSPARAMS_N_PORTS_SHIFT) |

◆ USB0_HCSPARAMS_N_PORTS_SHIFT

◆ USB0_HCSPARAMS_N_PTT

| #define USB0_HCSPARAMS_N_PTT | ( | x | ) | ((x) << USB0_HCSPARAMS_N_PTT_SHIFT) |

◆ USB0_HCSPARAMS_N_PTT_MASK

| #define USB0_HCSPARAMS_N_PTT_MASK (0xf << USB0_HCSPARAMS_N_PTT_SHIFT) |

◆ USB0_HCSPARAMS_N_PTT_SHIFT

◆ USB0_HCSPARAMS_N_TT

| #define USB0_HCSPARAMS_N_TT | ( | x | ) | ((x) << USB0_HCSPARAMS_N_TT_SHIFT) |

◆ USB0_HCSPARAMS_N_TT_MASK

| #define USB0_HCSPARAMS_N_TT_MASK (0xf << USB0_HCSPARAMS_N_TT_SHIFT) |

◆ USB0_HCSPARAMS_N_TT_SHIFT

◆ USB0_HCSPARAMS_PI

| #define USB0_HCSPARAMS_PI (1 << USB0_HCSPARAMS_PI_SHIFT) |

◆ USB0_HCSPARAMS_PI_SHIFT

◆ USB0_HCSPARAMS_PPC

| #define USB0_HCSPARAMS_PPC (1 << USB0_HCSPARAMS_PPC_SHIFT) |

◆ USB0_HCSPARAMS_PPC_SHIFT

◆ USB0_OTGSC

◆ USB0_OTGSC_ASV

| #define USB0_OTGSC_ASV (1 << USB0_OTGSC_ASV_SHIFT) |

◆ USB0_OTGSC_ASV_SHIFT

◆ USB0_OTGSC_ASVIE

| #define USB0_OTGSC_ASVIE (1 << USB0_OTGSC_ASVIE_SHIFT) |

◆ USB0_OTGSC_ASVIE_SHIFT

◆ USB0_OTGSC_ASVIS

| #define USB0_OTGSC_ASVIS (1 << USB0_OTGSC_ASVIS_SHIFT) |

◆ USB0_OTGSC_ASVIS_SHIFT

◆ USB0_OTGSC_AVV

| #define USB0_OTGSC_AVV (1 << USB0_OTGSC_AVV_SHIFT) |

◆ USB0_OTGSC_AVV_SHIFT

◆ USB0_OTGSC_AVVIE

| #define USB0_OTGSC_AVVIE (1 << USB0_OTGSC_AVVIE_SHIFT) |

◆ USB0_OTGSC_AVVIE_SHIFT

◆ USB0_OTGSC_AVVIS

| #define USB0_OTGSC_AVVIS (1 << USB0_OTGSC_AVVIS_SHIFT) |

◆ USB0_OTGSC_AVVIS_SHIFT

◆ USB0_OTGSC_BSE

| #define USB0_OTGSC_BSE (1 << USB0_OTGSC_BSE_SHIFT) |

◆ USB0_OTGSC_BSE_SHIFT

◆ USB0_OTGSC_BSEIE

| #define USB0_OTGSC_BSEIE (1 << USB0_OTGSC_BSEIE_SHIFT) |

◆ USB0_OTGSC_BSEIE_SHIFT

◆ USB0_OTGSC_BSEIS

| #define USB0_OTGSC_BSEIS (1 << USB0_OTGSC_BSEIS_SHIFT) |

◆ USB0_OTGSC_BSEIS_SHIFT

◆ USB0_OTGSC_BSV

| #define USB0_OTGSC_BSV (1 << USB0_OTGSC_BSV_SHIFT) |

◆ USB0_OTGSC_BSV_SHIFT

◆ USB0_OTGSC_BSVIE

| #define USB0_OTGSC_BSVIE (1 << USB0_OTGSC_BSVIE_SHIFT) |

◆ USB0_OTGSC_BSVIE_SHIFT

◆ USB0_OTGSC_BSVIS

| #define USB0_OTGSC_BSVIS (1 << USB0_OTGSC_BSVIS_SHIFT) |

◆ USB0_OTGSC_BSVIS_SHIFT

◆ USB0_OTGSC_DP

| #define USB0_OTGSC_DP (1 << USB0_OTGSC_DP_SHIFT) |

◆ USB0_OTGSC_DP_SHIFT

◆ USB0_OTGSC_DPIE

| #define USB0_OTGSC_DPIE (1 << USB0_OTGSC_DPIE_SHIFT) |

◆ USB0_OTGSC_DPIE_SHIFT

◆ USB0_OTGSC_DPIS

| #define USB0_OTGSC_DPIS (1 << USB0_OTGSC_DPIS_SHIFT) |

◆ USB0_OTGSC_DPIS_SHIFT

◆ USB0_OTGSC_DPS

| #define USB0_OTGSC_DPS (1 << USB0_OTGSC_DPS_SHIFT) |

◆ USB0_OTGSC_DPS_SHIFT

◆ USB0_OTGSC_HAAR

| #define USB0_OTGSC_HAAR (1 << USB0_OTGSC_HAAR_SHIFT) |

◆ USB0_OTGSC_HAAR_SHIFT

◆ USB0_OTGSC_HABA

| #define USB0_OTGSC_HABA (1 << USB0_OTGSC_HABA_SHIFT) |

◆ USB0_OTGSC_HABA_SHIFT

◆ USB0_OTGSC_HADP

| #define USB0_OTGSC_HADP (1 << USB0_OTGSC_HADP_SHIFT) |

◆ USB0_OTGSC_HADP_SHIFT

◆ USB0_OTGSC_ID

| #define USB0_OTGSC_ID (1 << USB0_OTGSC_ID_SHIFT) |

◆ USB0_OTGSC_ID_SHIFT

◆ USB0_OTGSC_IDIE

| #define USB0_OTGSC_IDIE (1 << USB0_OTGSC_IDIE_SHIFT) |

◆ USB0_OTGSC_IDIE_SHIFT

◆ USB0_OTGSC_IDIS

| #define USB0_OTGSC_IDIS (1 << USB0_OTGSC_IDIS_SHIFT) |

◆ USB0_OTGSC_IDIS_SHIFT

◆ USB0_OTGSC_IDPU

| #define USB0_OTGSC_IDPU (1 << USB0_OTGSC_IDPU_SHIFT) |

◆ USB0_OTGSC_IDPU_SHIFT

◆ USB0_OTGSC_MS1E

| #define USB0_OTGSC_MS1E (1 << USB0_OTGSC_MS1E_SHIFT) |

◆ USB0_OTGSC_MS1E_SHIFT

◆ USB0_OTGSC_MS1S

| #define USB0_OTGSC_MS1S (1 << USB0_OTGSC_MS1S_SHIFT) |

◆ USB0_OTGSC_MS1S_SHIFT

◆ USB0_OTGSC_MS1T

| #define USB0_OTGSC_MS1T (1 << USB0_OTGSC_MS1T_SHIFT) |

◆ USB0_OTGSC_MS1T_SHIFT

◆ USB0_OTGSC_OT

| #define USB0_OTGSC_OT (1 << USB0_OTGSC_OT_SHIFT) |

◆ USB0_OTGSC_OT_SHIFT

◆ USB0_OTGSC_VC

| #define USB0_OTGSC_VC (1 << USB0_OTGSC_VC_SHIFT) |

◆ USB0_OTGSC_VC_SHIFT

◆ USB0_OTGSC_VD

| #define USB0_OTGSC_VD (1 << USB0_OTGSC_VD_SHIFT) |

◆ USB0_OTGSC_VD_SHIFT

◆ USB0_PERIODICLISTBASE

◆ USB0_PERIODICLISTBASE_PERBASE31_12

| #define USB0_PERIODICLISTBASE_PERBASE31_12 | ( | x | ) | ((x) << USB0_PERIODICLISTBASE_PERBASE31_12_SHIFT) |

◆ USB0_PERIODICLISTBASE_PERBASE31_12_MASK

| #define USB0_PERIODICLISTBASE_PERBASE31_12_MASK (0xfffff << USB0_PERIODICLISTBASE_PERBASE31_12_SHIFT) |

◆ USB0_PERIODICLISTBASE_PERBASE31_12_SHIFT

◆ USB0_PORTSC1_D

◆ USB0_PORTSC1_D_CCS

| #define USB0_PORTSC1_D_CCS (1 << USB0_PORTSC1_D_CCS_SHIFT) |

◆ USB0_PORTSC1_D_CCS_SHIFT

◆ USB0_PORTSC1_D_FPR

| #define USB0_PORTSC1_D_FPR (1 << USB0_PORTSC1_D_FPR_SHIFT) |

◆ USB0_PORTSC1_D_FPR_SHIFT

◆ USB0_PORTSC1_D_HSP

| #define USB0_PORTSC1_D_HSP (1 << USB0_PORTSC1_D_HSP_SHIFT) |

◆ USB0_PORTSC1_D_HSP_SHIFT

◆ USB0_PORTSC1_D_PE

| #define USB0_PORTSC1_D_PE (1 << USB0_PORTSC1_D_PE_SHIFT) |

◆ USB0_PORTSC1_D_PE_SHIFT

◆ USB0_PORTSC1_D_PEC

| #define USB0_PORTSC1_D_PEC (1 << USB0_PORTSC1_D_PEC_SHIFT) |

◆ USB0_PORTSC1_D_PEC_SHIFT

◆ USB0_PORTSC1_D_PFSC

| #define USB0_PORTSC1_D_PFSC (1 << USB0_PORTSC1_D_PFSC_SHIFT) |

◆ USB0_PORTSC1_D_PFSC_SHIFT

◆ USB0_PORTSC1_D_PHCD

| #define USB0_PORTSC1_D_PHCD (1 << USB0_PORTSC1_D_PHCD_SHIFT) |

◆ USB0_PORTSC1_D_PHCD_SHIFT

◆ USB0_PORTSC1_D_PIC1_0

| #define USB0_PORTSC1_D_PIC1_0 | ( | x | ) | ((x) << USB0_PORTSC1_D_PIC1_0_SHIFT) |

◆ USB0_PORTSC1_D_PIC1_0_MASK

| #define USB0_PORTSC1_D_PIC1_0_MASK (0x3 << USB0_PORTSC1_D_PIC1_0_SHIFT) |

◆ USB0_PORTSC1_D_PIC1_0_SHIFT

◆ USB0_PORTSC1_D_PR

| #define USB0_PORTSC1_D_PR (1 << USB0_PORTSC1_D_PR_SHIFT) |

◆ USB0_PORTSC1_D_PR_SHIFT

◆ USB0_PORTSC1_D_PSPD

| #define USB0_PORTSC1_D_PSPD | ( | x | ) | ((x) << USB0_PORTSC1_D_PSPD_SHIFT) |

◆ USB0_PORTSC1_D_PSPD_MASK

| #define USB0_PORTSC1_D_PSPD_MASK (0x3 << USB0_PORTSC1_D_PSPD_SHIFT) |

◆ USB0_PORTSC1_D_PSPD_SHIFT

◆ USB0_PORTSC1_D_PTC3_0

| #define USB0_PORTSC1_D_PTC3_0 | ( | x | ) | ((x) << USB0_PORTSC1_D_PTC3_0_SHIFT) |

◆ USB0_PORTSC1_D_PTC3_0_MASK

| #define USB0_PORTSC1_D_PTC3_0_MASK (0xf << USB0_PORTSC1_D_PTC3_0_SHIFT) |

◆ USB0_PORTSC1_D_PTC3_0_SHIFT

◆ USB0_PORTSC1_D_SUSP

| #define USB0_PORTSC1_D_SUSP (1 << USB0_PORTSC1_D_SUSP_SHIFT) |

◆ USB0_PORTSC1_D_SUSP_SHIFT

◆ USB0_PORTSC1_H

◆ USB0_PORTSC1_H_CCS

| #define USB0_PORTSC1_H_CCS (1 << USB0_PORTSC1_H_CCS_SHIFT) |

◆ USB0_PORTSC1_H_CCS_SHIFT

◆ USB0_PORTSC1_H_CSC

| #define USB0_PORTSC1_H_CSC (1 << USB0_PORTSC1_H_CSC_SHIFT) |

◆ USB0_PORTSC1_H_CSC_SHIFT

◆ USB0_PORTSC1_H_FPR

| #define USB0_PORTSC1_H_FPR (1 << USB0_PORTSC1_H_FPR_SHIFT) |

◆ USB0_PORTSC1_H_FPR_SHIFT

◆ USB0_PORTSC1_H_HSP

| #define USB0_PORTSC1_H_HSP (1 << USB0_PORTSC1_H_HSP_SHIFT) |

◆ USB0_PORTSC1_H_HSP_SHIFT

◆ USB0_PORTSC1_H_LS

| #define USB0_PORTSC1_H_LS | ( | x | ) | ((x) << USB0_PORTSC1_H_LS_SHIFT) |

◆ USB0_PORTSC1_H_LS_MASK

| #define USB0_PORTSC1_H_LS_MASK (0x3 << USB0_PORTSC1_H_LS_SHIFT) |

◆ USB0_PORTSC1_H_LS_SHIFT

◆ USB0_PORTSC1_H_OCA

| #define USB0_PORTSC1_H_OCA (1 << USB0_PORTSC1_H_OCA_SHIFT) |

◆ USB0_PORTSC1_H_OCA_SHIFT

◆ USB0_PORTSC1_H_OCC

| #define USB0_PORTSC1_H_OCC (1 << USB0_PORTSC1_H_OCC_SHIFT) |

◆ USB0_PORTSC1_H_OCC_SHIFT

◆ USB0_PORTSC1_H_PE

| #define USB0_PORTSC1_H_PE (1 << USB0_PORTSC1_H_PE_SHIFT) |

◆ USB0_PORTSC1_H_PE_SHIFT

◆ USB0_PORTSC1_H_PEC

| #define USB0_PORTSC1_H_PEC (1 << USB0_PORTSC1_H_PEC_SHIFT) |

◆ USB0_PORTSC1_H_PEC_SHIFT

◆ USB0_PORTSC1_H_PFSC

| #define USB0_PORTSC1_H_PFSC (1 << USB0_PORTSC1_H_PFSC_SHIFT) |

◆ USB0_PORTSC1_H_PFSC_SHIFT

◆ USB0_PORTSC1_H_PHCD

| #define USB0_PORTSC1_H_PHCD (1 << USB0_PORTSC1_H_PHCD_SHIFT) |

◆ USB0_PORTSC1_H_PHCD_SHIFT

◆ USB0_PORTSC1_H_PIC1_0

| #define USB0_PORTSC1_H_PIC1_0 | ( | x | ) | ((x) << USB0_PORTSC1_H_PIC1_0_SHIFT) |

◆ USB0_PORTSC1_H_PIC1_0_MASK

| #define USB0_PORTSC1_H_PIC1_0_MASK (0x3 << USB0_PORTSC1_H_PIC1_0_SHIFT) |

◆ USB0_PORTSC1_H_PIC1_0_SHIFT

◆ USB0_PORTSC1_H_PP

| #define USB0_PORTSC1_H_PP (1 << USB0_PORTSC1_H_PP_SHIFT) |

◆ USB0_PORTSC1_H_PP_SHIFT

◆ USB0_PORTSC1_H_PR

| #define USB0_PORTSC1_H_PR (1 << USB0_PORTSC1_H_PR_SHIFT) |

◆ USB0_PORTSC1_H_PR_SHIFT

◆ USB0_PORTSC1_H_PSPD

| #define USB0_PORTSC1_H_PSPD | ( | x | ) | ((x) << USB0_PORTSC1_H_PSPD_SHIFT) |

◆ USB0_PORTSC1_H_PSPD_MASK

| #define USB0_PORTSC1_H_PSPD_MASK (0x3 << USB0_PORTSC1_H_PSPD_SHIFT) |

◆ USB0_PORTSC1_H_PSPD_SHIFT

◆ USB0_PORTSC1_H_PTC3_0

| #define USB0_PORTSC1_H_PTC3_0 | ( | x | ) | ((x) << USB0_PORTSC1_H_PTC3_0_SHIFT) |

◆ USB0_PORTSC1_H_PTC3_0_MASK

| #define USB0_PORTSC1_H_PTC3_0_MASK (0xf << USB0_PORTSC1_H_PTC3_0_SHIFT) |

◆ USB0_PORTSC1_H_PTC3_0_SHIFT

◆ USB0_PORTSC1_H_SUSP

| #define USB0_PORTSC1_H_SUSP (1 << USB0_PORTSC1_H_SUSP_SHIFT) |

◆ USB0_PORTSC1_H_SUSP_SHIFT

◆ USB0_PORTSC1_H_WKCN

| #define USB0_PORTSC1_H_WKCN (1 << USB0_PORTSC1_H_WKCN_SHIFT) |

◆ USB0_PORTSC1_H_WKCN_SHIFT

◆ USB0_PORTSC1_H_WKDC

| #define USB0_PORTSC1_H_WKDC (1 << USB0_PORTSC1_H_WKDC_SHIFT) |

◆ USB0_PORTSC1_H_WKDC_SHIFT

◆ USB0_PORTSC1_H_WKOC

| #define USB0_PORTSC1_H_WKOC (1 << USB0_PORTSC1_H_WKOC_SHIFT) |

◆ USB0_PORTSC1_H_WKOC_SHIFT

◆ USB0_TTCTRL

◆ USB0_TTCTRL_TTHA

| #define USB0_TTCTRL_TTHA | ( | x | ) | ((x) << USB0_TTCTRL_TTHA_SHIFT) |

◆ USB0_TTCTRL_TTHA_MASK

| #define USB0_TTCTRL_TTHA_MASK (0x7f << USB0_TTCTRL_TTHA_SHIFT) |

◆ USB0_TTCTRL_TTHA_SHIFT

◆ USB0_TXFILLTUNING

◆ USB0_TXFILLTUNING_TXFIFOTHRES

| #define USB0_TXFILLTUNING_TXFIFOTHRES | ( | x | ) | ((x) << USB0_TXFILLTUNING_TXFIFOTHRES_SHIFT) |

◆ USB0_TXFILLTUNING_TXFIFOTHRES_MASK

| #define USB0_TXFILLTUNING_TXFIFOTHRES_MASK (0x3f << USB0_TXFILLTUNING_TXFIFOTHRES_SHIFT) |

◆ USB0_TXFILLTUNING_TXFIFOTHRES_SHIFT

◆ USB0_TXFILLTUNING_TXSCHEATLTH

| #define USB0_TXFILLTUNING_TXSCHEATLTH | ( | x | ) | ((x) << USB0_TXFILLTUNING_TXSCHEATLTH_SHIFT) |

◆ USB0_TXFILLTUNING_TXSCHEATLTH_MASK

| #define USB0_TXFILLTUNING_TXSCHEATLTH_MASK (0x1f << USB0_TXFILLTUNING_TXSCHEATLTH_SHIFT) |

◆ USB0_TXFILLTUNING_TXSCHEATLTH_SHIFT

◆ USB0_TXFILLTUNING_TXSCHOH

| #define USB0_TXFILLTUNING_TXSCHOH | ( | x | ) | ((x) << USB0_TXFILLTUNING_TXSCHOH_SHIFT) |

◆ USB0_TXFILLTUNING_TXSCHOH_MASK

| #define USB0_TXFILLTUNING_TXSCHOH_MASK (0xff << USB0_TXFILLTUNING_TXSCHOH_SHIFT) |

◆ USB0_TXFILLTUNING_TXSCHOH_SHIFT

◆ USB0_USBCMD_D

◆ USB0_USBCMD_D_ATDTW

| #define USB0_USBCMD_D_ATDTW (1 << USB0_USBCMD_D_ATDTW_SHIFT) |

◆ USB0_USBCMD_D_ATDTW_SHIFT

◆ USB0_USBCMD_D_ITC

| #define USB0_USBCMD_D_ITC | ( | x | ) | ((x) << USB0_USBCMD_D_ITC_SHIFT) |

◆ USB0_USBCMD_D_ITC_MASK

| #define USB0_USBCMD_D_ITC_MASK (0xff << USB0_USBCMD_D_ITC_SHIFT) |

◆ USB0_USBCMD_D_ITC_SHIFT

◆ USB0_USBCMD_D_RS

| #define USB0_USBCMD_D_RS (1 << USB0_USBCMD_D_RS_SHIFT) |

◆ USB0_USBCMD_D_RS_SHIFT

◆ USB0_USBCMD_D_RST

| #define USB0_USBCMD_D_RST (1 << USB0_USBCMD_D_RST_SHIFT) |

◆ USB0_USBCMD_D_RST_SHIFT

◆ USB0_USBCMD_D_SUTW

| #define USB0_USBCMD_D_SUTW (1 << USB0_USBCMD_D_SUTW_SHIFT) |

◆ USB0_USBCMD_D_SUTW_SHIFT

◆ USB0_USBCMD_H

◆ USB0_USBCMD_H_ASE

| #define USB0_USBCMD_H_ASE (1 << USB0_USBCMD_H_ASE_SHIFT) |

◆ USB0_USBCMD_H_ASE_SHIFT

◆ USB0_USBCMD_H_ASP1_0

| #define USB0_USBCMD_H_ASP1_0 | ( | x | ) | ((x) << USB0_USBCMD_H_ASP1_0_SHIFT) |

◆ USB0_USBCMD_H_ASP1_0_MASK

| #define USB0_USBCMD_H_ASP1_0_MASK (0x3 << USB0_USBCMD_H_ASP1_0_SHIFT) |

◆ USB0_USBCMD_H_ASP1_0_SHIFT

◆ USB0_USBCMD_H_ASPE

| #define USB0_USBCMD_H_ASPE (1 << USB0_USBCMD_H_ASPE_SHIFT) |

◆ USB0_USBCMD_H_ASPE_SHIFT

◆ USB0_USBCMD_H_FS0

| #define USB0_USBCMD_H_FS0 (1 << USB0_USBCMD_H_FS0_SHIFT) |

◆ USB0_USBCMD_H_FS0_SHIFT

◆ USB0_USBCMD_H_FS1

| #define USB0_USBCMD_H_FS1 (1 << USB0_USBCMD_H_FS1_SHIFT) |

◆ USB0_USBCMD_H_FS1_SHIFT

◆ USB0_USBCMD_H_FS2

| #define USB0_USBCMD_H_FS2 (1 << USB0_USBCMD_H_FS2_SHIFT) |

◆ USB0_USBCMD_H_FS2_SHIFT

◆ USB0_USBCMD_H_IAA

| #define USB0_USBCMD_H_IAA (1 << USB0_USBCMD_H_IAA_SHIFT) |

◆ USB0_USBCMD_H_IAA_SHIFT

◆ USB0_USBCMD_H_ITC

| #define USB0_USBCMD_H_ITC | ( | x | ) | ((x) << USB0_USBCMD_H_ITC_SHIFT) |

◆ USB0_USBCMD_H_ITC_MASK

| #define USB0_USBCMD_H_ITC_MASK (0xff << USB0_USBCMD_H_ITC_SHIFT) |

◆ USB0_USBCMD_H_ITC_SHIFT

◆ USB0_USBCMD_H_PSE

| #define USB0_USBCMD_H_PSE (1 << USB0_USBCMD_H_PSE_SHIFT) |

◆ USB0_USBCMD_H_PSE_SHIFT

◆ USB0_USBCMD_H_RS

| #define USB0_USBCMD_H_RS (1 << USB0_USBCMD_H_RS_SHIFT) |

◆ USB0_USBCMD_H_RS_SHIFT

◆ USB0_USBCMD_H_RST

| #define USB0_USBCMD_H_RST (1 << USB0_USBCMD_H_RST_SHIFT) |

◆ USB0_USBCMD_H_RST_SHIFT

◆ USB0_USBINTR_D

◆ USB0_USBINTR_D_NAKE

| #define USB0_USBINTR_D_NAKE (1 << USB0_USBINTR_D_NAKE_SHIFT) |

◆ USB0_USBINTR_D_NAKE_SHIFT

◆ USB0_USBINTR_D_PCE

| #define USB0_USBINTR_D_PCE (1 << USB0_USBINTR_D_PCE_SHIFT) |

◆ USB0_USBINTR_D_PCE_SHIFT

◆ USB0_USBINTR_D_SLE

| #define USB0_USBINTR_D_SLE (1 << USB0_USBINTR_D_SLE_SHIFT) |

◆ USB0_USBINTR_D_SLE_SHIFT

◆ USB0_USBINTR_D_SRE

| #define USB0_USBINTR_D_SRE (1 << USB0_USBINTR_D_SRE_SHIFT) |

◆ USB0_USBINTR_D_SRE_SHIFT

◆ USB0_USBINTR_D_UE

| #define USB0_USBINTR_D_UE (1 << USB0_USBINTR_D_UE_SHIFT) |

◆ USB0_USBINTR_D_UE_SHIFT

◆ USB0_USBINTR_D_UEE

| #define USB0_USBINTR_D_UEE (1 << USB0_USBINTR_D_UEE_SHIFT) |

◆ USB0_USBINTR_D_UEE_SHIFT

◆ USB0_USBINTR_D_URE

| #define USB0_USBINTR_D_URE (1 << USB0_USBINTR_D_URE_SHIFT) |

◆ USB0_USBINTR_D_URE_SHIFT

◆ USB0_USBINTR_H

◆ USB0_USBINTR_H_AAE

| #define USB0_USBINTR_H_AAE (1 << USB0_USBINTR_H_AAE_SHIFT) |

◆ USB0_USBINTR_H_AAE_SHIFT

◆ USB0_USBINTR_H_FRE

| #define USB0_USBINTR_H_FRE (1 << USB0_USBINTR_H_FRE_SHIFT) |

◆ USB0_USBINTR_H_FRE_SHIFT

◆ USB0_USBINTR_H_PCE

| #define USB0_USBINTR_H_PCE (1 << USB0_USBINTR_H_PCE_SHIFT) |

◆ USB0_USBINTR_H_PCE_SHIFT

◆ USB0_USBINTR_H_SRE

| #define USB0_USBINTR_H_SRE (1 << USB0_USBINTR_H_SRE_SHIFT) |

◆ USB0_USBINTR_H_SRE_SHIFT

◆ USB0_USBINTR_H_UAIE

| #define USB0_USBINTR_H_UAIE (1 << USB0_USBINTR_H_UAIE_SHIFT) |

◆ USB0_USBINTR_H_UAIE_SHIFT

◆ USB0_USBINTR_H_UE

| #define USB0_USBINTR_H_UE (1 << USB0_USBINTR_H_UE_SHIFT) |

◆ USB0_USBINTR_H_UE_SHIFT

◆ USB0_USBINTR_H_UEE

| #define USB0_USBINTR_H_UEE (1 << USB0_USBINTR_H_UEE_SHIFT) |

◆ USB0_USBINTR_H_UEE_SHIFT

◆ USB0_USBINTR_H_UPIA

| #define USB0_USBINTR_H_UPIA (1 << USB0_USBINTR_H_UPIA_SHIFT) |

◆ USB0_USBINTR_H_UPIA_SHIFT

◆ USB0_USBMODE_D

◆ USB0_USBMODE_D_CM1_0

| #define USB0_USBMODE_D_CM1_0 | ( | x | ) | ((x) << USB0_USBMODE_D_CM1_0_SHIFT) |

◆ USB0_USBMODE_D_CM1_0_MASK

| #define USB0_USBMODE_D_CM1_0_MASK (0x3 << USB0_USBMODE_D_CM1_0_SHIFT) |

◆ USB0_USBMODE_D_CM1_0_SHIFT

◆ USB0_USBMODE_D_ES

| #define USB0_USBMODE_D_ES (1 << USB0_USBMODE_D_ES_SHIFT) |

◆ USB0_USBMODE_D_ES_SHIFT

◆ USB0_USBMODE_D_SDIS

| #define USB0_USBMODE_D_SDIS (1 << USB0_USBMODE_D_SDIS_SHIFT) |

◆ USB0_USBMODE_D_SDIS_SHIFT

◆ USB0_USBMODE_D_SLOM

| #define USB0_USBMODE_D_SLOM (1 << USB0_USBMODE_D_SLOM_SHIFT) |

◆ USB0_USBMODE_D_SLOM_SHIFT

◆ USB0_USBMODE_H

◆ USB0_USBMODE_H_CM

| #define USB0_USBMODE_H_CM | ( | x | ) | ((x) << USB0_USBMODE_H_CM_SHIFT) |

◆ USB0_USBMODE_H_CM_MASK

| #define USB0_USBMODE_H_CM_MASK (0x3 << USB0_USBMODE_H_CM_SHIFT) |

◆ USB0_USBMODE_H_CM_SHIFT

◆ USB0_USBMODE_H_ES

| #define USB0_USBMODE_H_ES (1 << USB0_USBMODE_H_ES_SHIFT) |

◆ USB0_USBMODE_H_ES_SHIFT

◆ USB0_USBMODE_H_SDIS

| #define USB0_USBMODE_H_SDIS (1 << USB0_USBMODE_H_SDIS_SHIFT) |

◆ USB0_USBMODE_H_SDIS_SHIFT

◆ USB0_USBMODE_H_VBPS

| #define USB0_USBMODE_H_VBPS (1 << USB0_USBMODE_H_VBPS_SHIFT) |

◆ USB0_USBMODE_H_VBPS_SHIFT

◆ USB0_USBSTS_D

◆ USB0_USBSTS_D_NAKI

| #define USB0_USBSTS_D_NAKI (1 << USB0_USBSTS_D_NAKI_SHIFT) |

◆ USB0_USBSTS_D_NAKI_SHIFT

◆ USB0_USBSTS_D_PCI

| #define USB0_USBSTS_D_PCI (1 << USB0_USBSTS_D_PCI_SHIFT) |

◆ USB0_USBSTS_D_PCI_SHIFT

◆ USB0_USBSTS_D_SLI

| #define USB0_USBSTS_D_SLI (1 << USB0_USBSTS_D_SLI_SHIFT) |

◆ USB0_USBSTS_D_SLI_SHIFT

◆ USB0_USBSTS_D_SRI

| #define USB0_USBSTS_D_SRI (1 << USB0_USBSTS_D_SRI_SHIFT) |

◆ USB0_USBSTS_D_SRI_SHIFT

◆ USB0_USBSTS_D_UEI

| #define USB0_USBSTS_D_UEI (1 << USB0_USBSTS_D_UEI_SHIFT) |

◆ USB0_USBSTS_D_UEI_SHIFT

◆ USB0_USBSTS_D_UI

| #define USB0_USBSTS_D_UI (1 << USB0_USBSTS_D_UI_SHIFT) |

◆ USB0_USBSTS_D_UI_SHIFT

◆ USB0_USBSTS_D_URI

| #define USB0_USBSTS_D_URI (1 << USB0_USBSTS_D_URI_SHIFT) |

◆ USB0_USBSTS_D_URI_SHIFT

◆ USB0_USBSTS_H

◆ USB0_USBSTS_H_AAI

| #define USB0_USBSTS_H_AAI (1 << USB0_USBSTS_H_AAI_SHIFT) |

◆ USB0_USBSTS_H_AAI_SHIFT

◆ USB0_USBSTS_H_AS

| #define USB0_USBSTS_H_AS (1 << USB0_USBSTS_H_AS_SHIFT) |

◆ USB0_USBSTS_H_AS_SHIFT

◆ USB0_USBSTS_H_FRI

| #define USB0_USBSTS_H_FRI (1 << USB0_USBSTS_H_FRI_SHIFT) |

◆ USB0_USBSTS_H_FRI_SHIFT

◆ USB0_USBSTS_H_HCH

| #define USB0_USBSTS_H_HCH (1 << USB0_USBSTS_H_HCH_SHIFT) |

◆ USB0_USBSTS_H_HCH_SHIFT

◆ USB0_USBSTS_H_PCI

| #define USB0_USBSTS_H_PCI (1 << USB0_USBSTS_H_PCI_SHIFT) |

◆ USB0_USBSTS_H_PCI_SHIFT

◆ USB0_USBSTS_H_PS

| #define USB0_USBSTS_H_PS (1 << USB0_USBSTS_H_PS_SHIFT) |

◆ USB0_USBSTS_H_PS_SHIFT

◆ USB0_USBSTS_H_RCL

| #define USB0_USBSTS_H_RCL (1 << USB0_USBSTS_H_RCL_SHIFT) |

◆ USB0_USBSTS_H_RCL_SHIFT

◆ USB0_USBSTS_H_SRI

| #define USB0_USBSTS_H_SRI (1 << USB0_USBSTS_H_SRI_SHIFT) |

◆ USB0_USBSTS_H_SRI_SHIFT

◆ USB0_USBSTS_H_UAI

| #define USB0_USBSTS_H_UAI (1 << USB0_USBSTS_H_UAI_SHIFT) |

◆ USB0_USBSTS_H_UAI_SHIFT

◆ USB0_USBSTS_H_UEI

| #define USB0_USBSTS_H_UEI (1 << USB0_USBSTS_H_UEI_SHIFT) |

◆ USB0_USBSTS_H_UEI_SHIFT

◆ USB0_USBSTS_H_UI

| #define USB0_USBSTS_H_UI (1 << USB0_USBSTS_H_UI_SHIFT) |

◆ USB0_USBSTS_H_UI_SHIFT

◆ USB0_USBSTS_H_UPI

| #define USB0_USBSTS_H_UPI (1 << USB0_USBSTS_H_UPI_SHIFT) |

◆ USB0_USBSTS_H_UPI_SHIFT

◆ USB_QH_CAPABILITIES_IOS

| #define USB_QH_CAPABILITIES_IOS (1 << USB_QH_CAPABILITIES_IOS_SHIFT) |

◆ USB_QH_CAPABILITIES_IOS_SHIFT

◆ USB_QH_CAPABILITIES_MPL

| #define USB_QH_CAPABILITIES_MPL | ( | x | ) | BIT_ARG(USB_QH_CAPABILITIES_MPL, (x)) |

◆ USB_QH_CAPABILITIES_MPL_MASK

| #define USB_QH_CAPABILITIES_MPL_MASK BIT_MASK(USB_QH_CAPABILITIES_MPL) |

◆ USB_QH_CAPABILITIES_MPL_SHIFT

◆ USB_QH_CAPABILITIES_MPL_WIDTH

◆ USB_QH_CAPABILITIES_MULT

| #define USB_QH_CAPABILITIES_MULT | ( | x | ) | BIT_ARG(USB_QH_CAPABILITIES_MULT, (x)) |

◆ USB_QH_CAPABILITIES_MULT_MASK

| #define USB_QH_CAPABILITIES_MULT_MASK BIT_MASK(USB_QH_CAPABILITIES_MULT) |

◆ USB_QH_CAPABILITIES_MULT_SHIFT

◆ USB_QH_CAPABILITIES_MULT_WIDTH

◆ USB_QH_CAPABILITIES_ZLT

| #define USB_QH_CAPABILITIES_ZLT (1 << USB_QH_CAPABILITIES_ZLT_SHIFT) |

◆ USB_QH_CAPABILITIES_ZLT_SHIFT

◆ USB_TD_DTD_TOKEN_IOC

| #define USB_TD_DTD_TOKEN_IOC (1 << USB_TD_DTD_TOKEN_IOC_SHIFT) |

◆ USB_TD_DTD_TOKEN_IOC_SHIFT

◆ USB_TD_DTD_TOKEN_MULTO

| #define USB_TD_DTD_TOKEN_MULTO | ( | x | ) | BIT_ARG(USB_TD_DTD_TOKEN_MULTO, (x)) |

◆ USB_TD_DTD_TOKEN_MULTO_MASK

| #define USB_TD_DTD_TOKEN_MULTO_MASK BIT_MASK(USB_TD_DTD_TOKEN_MULTO) |

◆ USB_TD_DTD_TOKEN_MULTO_SHIFT

◆ USB_TD_DTD_TOKEN_MULTO_WIDTH

◆ USB_TD_DTD_TOKEN_STATUS_ACTIVE

| #define USB_TD_DTD_TOKEN_STATUS_ACTIVE (1 << USB_TD_DTD_TOKEN_STATUS_ACTIVE_SHIFT) |

◆ USB_TD_DTD_TOKEN_STATUS_ACTIVE_SHIFT

◆ USB_TD_DTD_TOKEN_STATUS_BUFFER_ERROR

| #define USB_TD_DTD_TOKEN_STATUS_BUFFER_ERROR (1 << USB_TD_DTD_TOKEN_STATUS_BUFFER_ERROR_SHIFT) |

◆ USB_TD_DTD_TOKEN_STATUS_BUFFER_ERROR_SHIFT

◆ USB_TD_DTD_TOKEN_STATUS_HALTED

| #define USB_TD_DTD_TOKEN_STATUS_HALTED (1 << USB_TD_DTD_TOKEN_STATUS_HALTED_SHIFT) |

◆ USB_TD_DTD_TOKEN_STATUS_HALTED_SHIFT

◆ USB_TD_DTD_TOKEN_STATUS_TRANSACTION_ERROR

| #define USB_TD_DTD_TOKEN_STATUS_TRANSACTION_ERROR (1 << USB_TD_DTD_TOKEN_STATUS_TRANSACTION_ERROR_SHIFT) |

◆ USB_TD_DTD_TOKEN_STATUS_TRANSACTION_ERROR_SHIFT

◆ USB_TD_DTD_TOKEN_TOTAL_BYTES

| #define USB_TD_DTD_TOKEN_TOTAL_BYTES | ( | x | ) | BIT_ARG(USB_TD_DTD_TOKEN_TOTAL_BYTES, (x)) |

◆ USB_TD_DTD_TOKEN_TOTAL_BYTES_MASK

| #define USB_TD_DTD_TOKEN_TOTAL_BYTES_MASK BIT_MASK(USB_TD_DTD_TOKEN_TOTAL_BYTES) |

◆ USB_TD_DTD_TOKEN_TOTAL_BYTES_SHIFT

◆ USB_TD_DTD_TOKEN_TOTAL_BYTES_WIDTH

◆ USB_TD_NEXT_DTD_POINTER_TERMINATE

| #define USB_TD_NEXT_DTD_POINTER_TERMINATE |

Value:

((volatile usb_transfer_descriptor_t *) \

Definition: usb.h:39

#define USB_TD_NEXT_DTD_POINTER_TERMINATE_SHIFT

Definition: usb.h:46

◆ USB_TD_NEXT_DTD_POINTER_TERMINATE_SHIFT

Typedef Documentation

◆ usb_transfer_descriptor_t

| typedef struct usb_transfer_descriptor_t usb_transfer_descriptor_t |