ccs.h File Reference

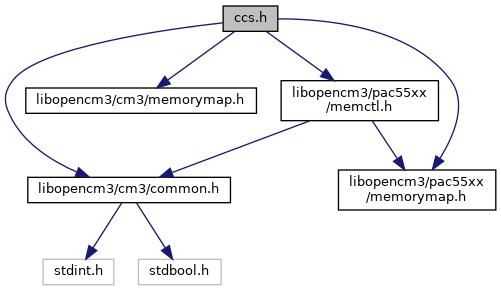

#include <libopencm3/cm3/common.h>#include <libopencm3/cm3/memorymap.h>#include <libopencm3/pac55xx/memorymap.h>#include <libopencm3/pac55xx/memctl.h>

Include dependency graph for ccs.h:

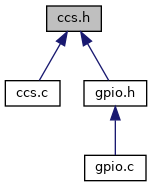

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | ccs_clk_config |

| CCS Clock Configuration structure. More... | |

Enumerations | |

| enum | ccs_muxsel_func_t { CCS_MUXSEL_GPIO = 0 , CCS_MUXSEL_AF1 = 1 , CCS_MUXSEL_AF2 = 2 , CCS_MUXSEL_AF3 = 3 , CCS_MUXSEL_AF4 = 4 , CCS_MUXSEL_AF5 = 5 , CCS_MUXSEL_AF6 = 6 , CCS_MUXSEL_AF7 = 7 } |

| enum | ccs_pull_updown_t { CCS_IO_PULL_NONE = 0 , CCS_IO_PULL_UP = 1 , CCS_IO_PULL_DOWN = 2 } |

| Pull Up/Down enum for type specificity. More... | |

| enum | ccs_drive_strength_t { CCS_DSR_DS_6MA = 0x00 , CCS_DSR_DS_8MA = 0x01 , CCS_DSR_DS_11MA = 0x02 , CCS_DSR_DS_14MA = 0x03 , CCS_DSR_DS_17MA = 0x04 , CCS_DSR_DS_20MA = 0x05 , CCS_DSR_DS_22MA = 0x06 , CCS_DSR_DS_25MA = 0x07 } |

| Drive strength enumeration for type specificity. More... | |

Functions | |

| void | ccs_frclkmux_select (uint32_t sel) |

| Select the source for FRCLK. More... | |

| void | ccs_rosc_enable (void) |

| Enable the 16MHz Ring oscillator. More... | |

| void | ccs_rosc_disable (void) |

| Disable the 16MHz Ring oscillator. More... | |

| void | ccs_sclkmux_select_frclk (void) |

| Select FRCLK for SCLK. More... | |

| void | ccs_sclkmux_select_pllclk (void) |

| Select PLLCLK for SCLK. More... | |

| void | ccs_clkfail_enable (void) |

| Enable Clock Fail Detection. More... | |

| void | ccs_clkfail_disable (void) |

| Disable Clock Fail Detection. More... | |

| void | ccs_clkfailmux_select_frclk (void) |

| Select FRCLK for Clock Fail Detection. More... | |

| void | ccs_clkfailmux_select_pllclk (void) |

| Select PLLCLK for Clock Fail Detection. More... | |

| void | ccs_ldo_enable (void) |

| Enable the LDO. More... | |

| void | ccs_ldo_disable (void) |

| Disable the LDO. More... | |

| void | ccs_pclk_enable (void) |

| Enable the Peripheral Clock. More... | |

| void | ccs_pclk_disable (void) |

| Disable the Peripheral Clock. More... | |

| void | ccs_aclk_enable (void) |

| Enable the Auxiliary Clock. More... | |

| void | ccs_aclk_disable (void) |

| Disable the Auxiliary Clock. More... | |

| void | ccs_adcclk_enable (void) |

| Enable the ADC Clock. More... | |

| void | ccs_adcclk_disable (void) |

| Disable the ADC Clock. More... | |

| void | ccs_stclk_sleep_enable (void) |

| Enable SysTick clock gating in deep sleep mode. More... | |

| void | ccs_stclk_sleep_disable (void) |

| Disable SysTick clock gating in deep sleep mode. More... | |

| void | ccs_set_pclkdiv (uint32_t div) |

| Set the divisor for the Peripheral Clock. More... | |

| void | ccs_set_aclkdiv (uint32_t div) |

| Set the divisor for the Auxiliary Clock. More... | |

| void | ccs_set_hclkdiv (uint32_t div) |

| Set the divisor for the AHB Clock. More... | |

| void | ccs_pll_enable (void) |

| Enable the PLL. More... | |

| void | ccs_pll_disable (void) |

| Disable the PLL. More... | |

| bool | ccs_pll_locked (void) |

| Check if the PLL is locked. More... | |

| void | ccs_pll_bypass_enable (void) |

| Enable the PLL bypass. More... | |

| void | ccs_pll_bypass_disable (void) |

| Disable the PLL bypass. More... | |

| void | ccs_pll_set_outdiv (uint32_t div) |

| Set the output divisor. More... | |

| void | ccs_pll_set_indiv (uint32_t div) |

| Set the PLL input divisor. More... | |

| void | ccs_pll_set_fbdiv (uint32_t div) |

| Set the PLL feedback divisor. More... | |

| void | css_pll_config_enable (uint32_t indiv, uint32_t fbdiv, uint32_t outdiv) |

| Configure the CCS PLL, enable it, and wait for lock. More... | |

| uint32_t | ccs_get_peripheral_clk_freq (uint32_t periph, uint32_t select) |

| Get the clock rate (in Hz) of the specified peripheral. More... | |

| void | ccs_reset_clocks (void) |

| Restores CCSCTL and CCSPLLCTL registers to default/safe values. More... | |

| void | ccs_configure_clocks (const struct ccs_clk_config *config) |

| Setup the PAC55xx clocks with the given struct. More... | |