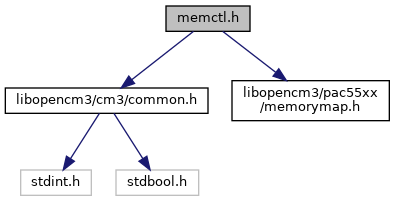

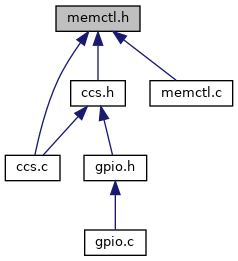

Go to the source code of this file.

Functions | |

| void | memctl_flash_set_wstate (uint32_t wstate) |

| Set the number of wait states for Flash reads. More... | |

| void | memctl_flash_set_mclkdiv (uint32_t div) |

| Set the MCLK divisor. More... | |

| void | memctl_flash_reset_write_buffer (void) |

| Set WRITEWORDCOUNT to 0 to reset the Flash write data buffer. More... | |

| void | memctl_flash_standby_mode_enable (void) |

| Enable Flash Standby Mode. More... | |

| void | memctl_flash_standby_mode_disable (void) |

| Disable Flash Standby Mode. More... | |

| void | memctl_flash_cache_enable (void) |

| Enable Flash cache. More... | |

| void | memctl_flash_cache_disable (void) |

| Disable Flash cache. More... | |

| void | memctl_flash_select_roscclk (void) |

| Select ROSCCLK as input to Flash Memory Controller. More... | |

| void | memctl_flash_select_mclk (void) |

| Select MCLK as input to Flash Memory Controller. More... | |

| void | memctl_sram_ecc_enable (void) |

| Enable SRAM ECC. More... | |

| void | memctl_sram_ecc_disable (void) |

| Disable SRAM ECC. More... | |

| void | memctl_sram_ecc_single_bit_interrupt_enable (void) |

| Enable SRAM ECC Single Bit Detection Interrupt. More... | |

| void | memctl_sram_ecc_single_bit_interrupt_disable (void) |

| Disable SRAM ECC Single Bit Detection Interrupt. More... | |

| void | memctl_sram_ecc_dual_bit_interrupt_enable (void) |

| Enable SRAM ECC Dual Bit Detection Interrupt. More... | |

| void | memctl_sram_ecc_dual_bit_interrupt_disable (void) |

| Disable SRAM ECC Dual Bit Detection Interrupt. More... | |

| void | memctl_invaddr_interrupt_enable (void) |

| Enable Invalid Memory Access Interrupt. More... | |

| void | memctl_invaddr_interrupt_disable (void) |

| Disable Invalid Memory Access Interrupt. More... | |

Function Documentation

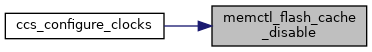

◆ memctl_flash_cache_disable()

| void memctl_flash_cache_disable | ( | void | ) |

Disable Flash cache.

Definition at line 46 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_CACHEDIS.

Referenced by ccs_configure_clocks().

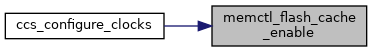

◆ memctl_flash_cache_enable()

| void memctl_flash_cache_enable | ( | void | ) |

Enable Flash cache.

Definition at line 43 of file memctl.c.

References MEMCTL_MEMCTLR.

Referenced by ccs_configure_clocks().

◆ memctl_flash_reset_write_buffer()

| void memctl_flash_reset_write_buffer | ( | void | ) |

Set WRITEWORDCOUNT to 0 to reset the Flash write data buffer.

Definition at line 34 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_WRITEWORDCNT_MASK.

◆ memctl_flash_select_mclk()

| void memctl_flash_select_mclk | ( | void | ) |

Select MCLK as input to Flash Memory Controller.

Definition at line 52 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_MCLKSEL.

Referenced by ccs_configure_clocks().

◆ memctl_flash_select_roscclk()

| void memctl_flash_select_roscclk | ( | void | ) |

Select ROSCCLK as input to Flash Memory Controller.

Definition at line 49 of file memctl.c.

References MEMCTL_MEMCTLR.

Referenced by ccs_configure_clocks().

◆ memctl_flash_set_mclkdiv()

| void memctl_flash_set_mclkdiv | ( | uint32_t | div | ) |

Set the MCLK divisor.

- Parameters

-

[in] div HCLK to MCLK divisor: 1-16

Definition at line 31 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_MCLKDIV.

Referenced by ccs_configure_clocks().

◆ memctl_flash_set_wstate()

| void memctl_flash_set_wstate | ( | uint32_t | wstate | ) |

Set the number of wait states for Flash reads.

- Parameters

-

[in] wstate Wait states: 0-15

Set the number of wait states for Flash reads.

- Date

- April 1, 2020

This library supports the Memory Controller in the PAC55xx SoC from Qorvo.

LGPL License Terms libopencm3 License

Definition at line 28 of file memctl.c.

References MEMCTL_MEMCTLR, MEMCTL_MEMCTLR_WSTATE, and MEMCTL_MEMCTLR_WSTATE_MASK.

Referenced by ccs_configure_clocks().

◆ memctl_flash_standby_mode_disable()

| void memctl_flash_standby_mode_disable | ( | void | ) |

◆ memctl_flash_standby_mode_enable()

| void memctl_flash_standby_mode_enable | ( | void | ) |

Enable Flash Standby Mode.

Definition at line 37 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_STBY.

◆ memctl_invaddr_interrupt_disable()

| void memctl_invaddr_interrupt_disable | ( | void | ) |

Disable Invalid Memory Access Interrupt.

Definition at line 76 of file memctl.c.

References MEMCTL_MEMCTLR.

◆ memctl_invaddr_interrupt_enable()

| void memctl_invaddr_interrupt_enable | ( | void | ) |

Enable Invalid Memory Access Interrupt.

Definition at line 73 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_INVADDRIE.

◆ memctl_sram_ecc_disable()

| void memctl_sram_ecc_disable | ( | void | ) |

Disable SRAM ECC.

Definition at line 58 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_ECCDIS.

◆ memctl_sram_ecc_dual_bit_interrupt_disable()

| void memctl_sram_ecc_dual_bit_interrupt_disable | ( | void | ) |

Disable SRAM ECC Dual Bit Detection Interrupt.

Definition at line 70 of file memctl.c.

References MEMCTL_MEMCTLR.

◆ memctl_sram_ecc_dual_bit_interrupt_enable()

| void memctl_sram_ecc_dual_bit_interrupt_enable | ( | void | ) |

Enable SRAM ECC Dual Bit Detection Interrupt.

Definition at line 67 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_DEIE.

◆ memctl_sram_ecc_enable()

| void memctl_sram_ecc_enable | ( | void | ) |

◆ memctl_sram_ecc_single_bit_interrupt_disable()

| void memctl_sram_ecc_single_bit_interrupt_disable | ( | void | ) |

Disable SRAM ECC Single Bit Detection Interrupt.

Definition at line 64 of file memctl.c.

References MEMCTL_MEMCTLR.

◆ memctl_sram_ecc_single_bit_interrupt_enable()

| void memctl_sram_ecc_single_bit_interrupt_enable | ( | void | ) |

Enable SRAM ECC Single Bit Detection Interrupt.

Definition at line 61 of file memctl.c.

References MEMCTL_MEMCTLR, and MEMCTL_MEMCTLR_SEIE.