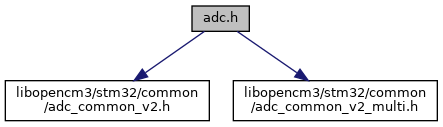

#include <libopencm3/stm32/common/adc_common_v2.h>#include <libopencm3/stm32/common/adc_common_v2_multi.h>

Include dependency graph for f3/adc.h:

Go to the source code of this file.

Functions | |

| void | adc_enable_analog_watchdog_regular (uint32_t adc) |

| ADC Enable Analog Watchdog for Regular Conversions. More... | |

| void | adc_disable_analog_watchdog_regular (uint32_t adc) |

| ADC Enable Analog Watchdog for Regular Conversions. More... | |

| void | adc_enable_analog_watchdog_injected (uint32_t adc) |

| ADC Enable Analog Watchdog for Injected Conversions. More... | |

| void | adc_disable_analog_watchdog_injected (uint32_t adc) |

| ADC Disable Analog Watchdog for Injected Conversions. More... | |

| void | adc_enable_discontinuous_mode_regular (uint32_t adc, uint8_t length) |

| ADC Enable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_disable_discontinuous_mode_regular (uint32_t adc) |

| ADC Disable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_enable_discontinuous_mode_injected (uint32_t adc) |

| ADC Enable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_disable_discontinuous_mode_injected (uint32_t adc) |

| ADC Disable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_enable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Enable Automatic Injected Conversions. More... | |

| void | adc_disable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Disable Automatic Injected Conversions. More... | |

| void | adc_enable_analog_watchdog_on_all_channels (uint32_t adc) |

| ADC Enable Analog Watchdog for All Regular and/or Injected Channels. More... | |

| void | adc_enable_analog_watchdog_on_selected_channel (uint32_t adc, uint8_t channel) |

| ADC Enable Analog Watchdog for a Selected Channel. More... | |

| void | adc_enable_eoc_interrupt_injected (uint32_t adc) |

| ADC Enable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_disable_eoc_interrupt_injected (uint32_t adc) |

| ADC Disable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_enable_eos_interrupt_injected (uint32_t adc) |

| ADC Enable Injected End-Of-Sequence Interrupt. More... | |

| void | adc_disable_eos_interrupt_injected (uint32_t adc) |

| ADC Disable Injected End-Of-Sequence Interrupt. More... | |

| void | adc_enable_all_awd_interrupt (uint32_t adc) |

| ADC Enable Analog Watchdog Interrupt. More... | |

| void | adc_disable_all_awd_interrupt (uint32_t adc) |

| ADC Disable Analog Watchdog Interrupt. More... | |

| void | adc_enable_eos_interrupt (uint32_t adc) |

| ADC Enable Regular End-Of-Sequence Interrupt. More... | |

| void | adc_disable_eos_interrupt (uint32_t adc) |

| ADC Disable Regular End-Of-Sequence Interrupt. More... | |

| void | adc_start_conversion_injected (uint32_t adc) |

| ADC Software Triggered Conversion on Injected Channels. More... | |

| void | adc_disable_external_trigger_regular (uint32_t adc) |

| ADC Disable an External Trigger for Regular Channels. More... | |

| void | adc_disable_external_trigger_injected (uint32_t adc) |

| ADC Disable an External Trigger for Injected Channels. More... | |

| void | adc_set_watchdog_high_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Upper Threshold. More... | |

| void | adc_set_watchdog_low_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Lower Threshold. More... | |

| void | adc_set_injected_sequence (uint32_t adc, uint8_t length, uint8_t channel[]) |

| ADC Set an Injected Channel Conversion Sequence. More... | |

| bool | adc_eoc_injected (uint32_t adc) |

| ADC Read the End-of-Conversion Flag for Injected Conversion. More... | |

| bool | adc_eos_injected (uint32_t adc) |

| ADC Read the End-of-Sequence Flag for Injected Conversions. More... | |

| uint32_t | adc_read_injected (uint32_t adc, uint8_t reg) |

| ADC Read from an Injected Conversion Result Register. More... | |

| void | adc_set_injected_offset (uint32_t adc, uint8_t reg, uint32_t offset) |

| ADC Set the Injected Channel Data Offset. More... | |

| void | adc_set_clk_prescale (uint32_t adc, uint32_t prescaler) |

| ADC Set Clock Prescale. More... | |

| void | adc_set_multi_mode (uint32_t adc, uint32_t mode) |

| ADC set multi mode. More... | |

| void | adc_enable_external_trigger_regular (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Regular Channels. More... | |

| void | adc_enable_external_trigger_injected (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Injected Channels. More... | |

| bool | adc_awd (uint32_t adc) |

| ADC Read the Analog Watchdog Flag. More... | |