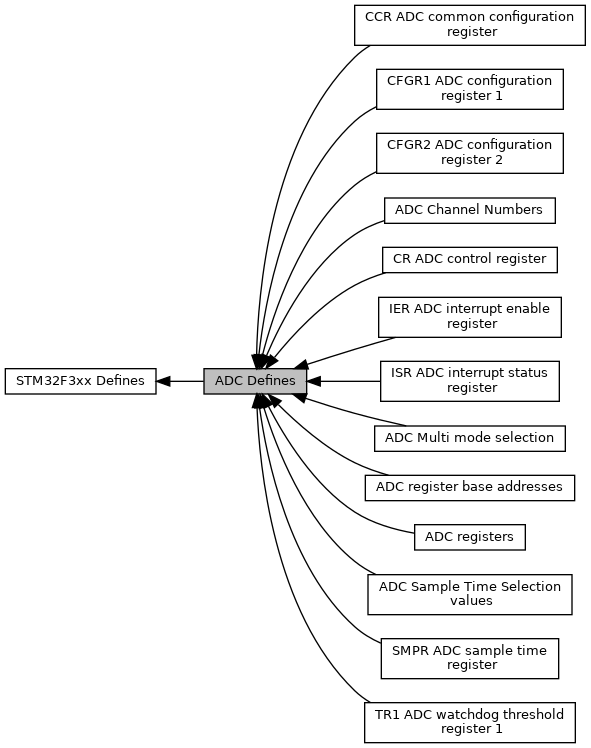

Defined Constants and Types for the STM32F37x Analog to Digital converter More...

Functions | |

| void | adc_enable_analog_watchdog_regular (uint32_t adc) |

| ADC Enable Analog Watchdog for Regular Conversions. More... | |

| void | adc_disable_analog_watchdog_regular (uint32_t adc) |

| ADC Enable Analog Watchdog for Regular Conversions. More... | |

| void | adc_enable_analog_watchdog_injected (uint32_t adc) |

| ADC Enable Analog Watchdog for Injected Conversions. More... | |

| void | adc_disable_analog_watchdog_injected (uint32_t adc) |

| ADC Disable Analog Watchdog for Injected Conversions. More... | |

| void | adc_enable_discontinuous_mode_regular (uint32_t adc, uint8_t length) |

| ADC Enable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_disable_discontinuous_mode_regular (uint32_t adc) |

| ADC Disable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_enable_discontinuous_mode_injected (uint32_t adc) |

| ADC Enable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_disable_discontinuous_mode_injected (uint32_t adc) |

| ADC Disable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_enable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Enable Automatic Injected Conversions. More... | |

| void | adc_disable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Disable Automatic Injected Conversions. More... | |

| void | adc_enable_analog_watchdog_on_all_channels (uint32_t adc) |

| ADC Enable Analog Watchdog for All Regular and/or Injected Channels. More... | |

| void | adc_enable_analog_watchdog_on_selected_channel (uint32_t adc, uint8_t channel) |

| ADC Enable Analog Watchdog for a Selected Channel. More... | |

| void | adc_enable_eoc_interrupt_injected (uint32_t adc) |

| ADC Enable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_disable_eoc_interrupt_injected (uint32_t adc) |

| ADC Disable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_enable_eos_interrupt_injected (uint32_t adc) |

| ADC Enable Injected End-Of-Sequence Interrupt. More... | |

| void | adc_disable_eos_interrupt_injected (uint32_t adc) |

| ADC Disable Injected End-Of-Sequence Interrupt. More... | |

| void | adc_enable_all_awd_interrupt (uint32_t adc) |

| ADC Enable Analog Watchdog Interrupt. More... | |

| void | adc_disable_all_awd_interrupt (uint32_t adc) |

| ADC Disable Analog Watchdog Interrupt. More... | |

| void | adc_enable_eos_interrupt (uint32_t adc) |

| ADC Enable Regular End-Of-Sequence Interrupt. More... | |

| void | adc_disable_eos_interrupt (uint32_t adc) |

| ADC Disable Regular End-Of-Sequence Interrupt. More... | |

| void | adc_start_conversion_injected (uint32_t adc) |

| ADC Software Triggered Conversion on Injected Channels. More... | |

| void | adc_disable_external_trigger_regular (uint32_t adc) |

| ADC Disable an External Trigger for Regular Channels. More... | |

| void | adc_disable_external_trigger_injected (uint32_t adc) |

| ADC Disable an External Trigger for Injected Channels. More... | |

| void | adc_set_watchdog_high_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Upper Threshold. More... | |

| void | adc_set_watchdog_low_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Lower Threshold. More... | |

| void | adc_set_injected_sequence (uint32_t adc, uint8_t length, uint8_t channel[]) |

| ADC Set an Injected Channel Conversion Sequence. More... | |

| bool | adc_eoc_injected (uint32_t adc) |

| ADC Read the End-of-Conversion Flag for Injected Conversion. More... | |

| bool | adc_eos_injected (uint32_t adc) |

| ADC Read the End-of-Sequence Flag for Injected Conversions. More... | |

| uint32_t | adc_read_injected (uint32_t adc, uint8_t reg) |

| ADC Read from an Injected Conversion Result Register. More... | |

| void | adc_set_injected_offset (uint32_t adc, uint8_t reg, uint32_t offset) |

| ADC Set the Injected Channel Data Offset. More... | |

| void | adc_set_clk_prescale (uint32_t adc, uint32_t prescaler) |

| ADC Set Clock Prescale. More... | |

| void | adc_set_multi_mode (uint32_t adc, uint32_t mode) |

| ADC set multi mode. More... | |

| void | adc_enable_external_trigger_regular (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Regular Channels. More... | |

| void | adc_enable_external_trigger_injected (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Injected Channels. More... | |

| bool | adc_awd (uint32_t adc) |

| ADC Read the Analog Watchdog Flag. More... | |

| void | adc_power_on_async (uint32_t adc) |

| Turn on the ADC (async) More... | |

| void | adc_power_on (uint32_t adc) |

| Turn on the ADC. More... | |

| bool | adc_is_power_on (uint32_t adc) |

| Is the ADC powered up and ready? More... | |

| void | adc_power_off_async (uint32_t adc) |

| Turn off the ADC (async) This will actually block if it needs to turn off a currently running conversion, as per ref man. More... | |

| void | adc_power_off (uint32_t adc) |

| Turn off the ADC This will actually block if it needs to turn off a currently running conversion, as per ref man. More... | |

| bool | adc_is_power_off (uint32_t adc) |

| Is the ADC powered down? More... | |

| void | adc_calibrate_async (uint32_t adc) |

| Start the ADC calibration and immediately return. More... | |

| bool | adc_is_calibrating (uint32_t adc) |

| Is the ADC Calibrating? More... | |

| void | adc_calibrate (uint32_t adc) |

| Start ADC calibration and wait for it to finish. More... | |

| void | adc_set_continuous_conversion_mode (uint32_t adc) |

| Enable Continuous Conversion Mode In this mode the ADC starts a new conversion of a single channel or a channel group immediately following completion of the previous channel group conversion. More... | |

| void | adc_set_single_conversion_mode (uint32_t adc) |

| Enable Single Conversion Mode In this mode the ADC performs a conversion of one channel or a channel group and stops. More... | |

| void | adc_set_regular_sequence (uint32_t adc, uint8_t length, uint8_t channel[]) |

| ADC Set a Regular Channel Conversion Sequence. More... | |

| void | adc_set_sample_time_on_all_channels (uint32_t adc, uint8_t time) |

| ADC Set the Sample Time for All Channels. More... | |

| void | adc_enable_temperature_sensor (void) |

| Enable the temperature sensor (only) The channel this is available on is unfortunately not consistent, even though the bit used to enable it is. More... | |

| void | adc_disable_temperature_sensor (void) |

| Disable the temperature sensor (only) More... | |

| void | adc_enable_vrefint (void) |

| Enable the internal voltage reference (only) The channel this is available on is unfortunately not consistent, even though the bit used to enable it is. More... | |

| void | adc_disable_vrefint (void) |

| Disable the internal voltage reference (only) More... | |

| void | adc_set_resolution (uint32_t adc, uint16_t resolution) |

| ADC Set Resolution. More... | |

| void | adc_set_left_aligned (uint32_t adc) |

| ADC Set the Data as Left Aligned. More... | |

| void | adc_set_right_aligned (uint32_t adc) |

| ADC Set the Data as Right Aligned. More... | |

| void | adc_enable_dma (uint32_t adc) |

| ADC Enable DMA Transfers. More... | |

| void | adc_disable_dma (uint32_t adc) |

| ADC Disable DMA Transfers. More... | |

| bool | adc_eoc (uint32_t adc) |

| ADC Read the End-of-Conversion Flag. More... | |

| bool | adc_eos (uint32_t adc) |

| ADC Read the End-of-Sequence Flag for Regular Conversions. More... | |

| void | adc_enable_eoc_interrupt (uint32_t adc) |

| ADC Enable Regular End-Of-Conversion Interrupt. More... | |

| void | adc_disable_eoc_interrupt (uint32_t adc) |

| ADC Disable Regular End-Of-Conversion Interrupt. More... | |

| void | adc_enable_overrun_interrupt (uint32_t adc) |

| ADC Enable the Overrun Interrupt. More... | |

| void | adc_disable_overrun_interrupt (uint32_t adc) |

| ADC Disable the Overrun Interrupt. More... | |

| bool | adc_get_overrun_flag (uint32_t adc) |

| ADC Read the Overrun Flag. More... | |

| void | adc_clear_overrun_flag (uint32_t adc) |

| ADC Clear Overrun Flags. More... | |

| uint32_t | adc_read_regular (uint32_t adc) |

| ADC Read from the Regular Conversion Result Register. More... | |

| void | adc_start_conversion_regular (uint32_t adc) |

| ADC Software Triggered Conversion on Regular Channels. More... | |

| void | adc_enable_dma_circular_mode (uint32_t adc) |

| Enable circular mode for DMA transfers. More... | |

| void | adc_disable_dma_circular_mode (uint32_t adc) |

| Disable circular mode for DMA transfers. More... | |

| void | adc_enable_delayed_conversion_mode (uint32_t adc) |

| Enable Delayed Conversion Mode. More... | |

| void | adc_disable_delayed_conversion_mode (uint32_t adc) |

| Enable Delayed Conversion Mode. More... | |

| void | adc_set_sample_time (uint32_t adc, uint8_t channel, uint8_t time) |

| ADC Set the Sample Time for a Single Channel. More... | |

| void | adc_enable_regulator (uint32_t adc) |

| Enable the ADC Voltage regulator Before any use of the ADC, the ADC Voltage regulator must be enabled. More... | |

| void | adc_disable_regulator (uint32_t adc) |

| Disable the ADC Voltage regulator You can disable the adc vreg when not in use to save power. More... | |

Detailed Description

Defined Constants and Types for the STM32F37x Analog to Digital converter

- Version

- 1.0.0

- Date

- 11 July 2013

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ ADC12_CCR

◆ ADC12_CDR

◆ ADC12_CSR

◆ ADC1_AWD2CR

| #define ADC1_AWD2CR ADC_AWD2CR(ADC1_BASE) |

◆ ADC1_AWD3CR

| #define ADC1_AWD3CR ADC_AWD3CR(ADC1_BASE) |

◆ ADC1_CALFACT

| #define ADC1_CALFACT ADC_CALFACT(ADC1_BASE) |

◆ ADC1_CFGR

◆ ADC1_CFGR1

◆ ADC1_CR

◆ ADC1_DIFSEL

| #define ADC1_DIFSEL ADC_DIFSEL(ADC1_BASE) |

◆ ADC1_DR

◆ ADC1_IER

◆ ADC1_ISR

◆ ADC1_JDR1

◆ ADC1_JDR2

◆ ADC1_JDR3

◆ ADC1_JDR4

◆ ADC1_JSQR

◆ ADC1_OFR1

◆ ADC1_OFR2

◆ ADC1_OFR3

◆ ADC1_OFR4

◆ ADC1_SMPR1

◆ ADC1_SMPR2

◆ ADC1_SQR1

◆ ADC1_SQR2

◆ ADC1_SQR3

◆ ADC1_SQR4

◆ ADC1_TR1

◆ ADC1_TR2

◆ ADC1_TR3

◆ ADC2_AWD2CR

| #define ADC2_AWD2CR ADC_AWD2CR(ADC2_BASE) |

◆ ADC2_AWD3CR

| #define ADC2_AWD3CR ADC_AWD3CR(ADC2_BASE) |

◆ ADC2_CALFACT

| #define ADC2_CALFACT ADC_CALFACT(ADC2_BASE) |

◆ ADC2_CFGR

◆ ADC2_CFGR1

◆ ADC2_CR

◆ ADC2_DIFSEL

| #define ADC2_DIFSEL ADC_DIFSEL(ADC2_BASE) |

◆ ADC2_DR

◆ ADC2_IER

◆ ADC2_ISR

◆ ADC2_JDR1

◆ ADC2_JDR2

◆ ADC2_JDR3

◆ ADC2_JDR4

◆ ADC2_JSQR

◆ ADC2_OFR1

◆ ADC2_OFR2

◆ ADC2_OFR3

◆ ADC2_OFR4

◆ ADC2_SMPR1

◆ ADC2_SMPR2

◆ ADC2_SQR1

◆ ADC2_SQR2

◆ ADC2_SQR3

◆ ADC2_SQR4

◆ ADC2_TR1

◆ ADC2_TR2

◆ ADC2_TR3

◆ ADC34_CCR

◆ ADC34_CDR

◆ ADC34_CSR

◆ ADC3_AWD2CR

| #define ADC3_AWD2CR ADC_AWD2CR(ADC3_BASE) |

◆ ADC3_AWD3CR

| #define ADC3_AWD3CR ADC_AWD3CR(ADC3_BASE) |

◆ ADC3_CALFACT

| #define ADC3_CALFACT ADC_CALFACT(ADC3_BASE) |

◆ ADC3_CFGR

◆ ADC3_CFGR1

◆ ADC3_CR

◆ ADC3_DIFSEL

| #define ADC3_DIFSEL ADC_DIFSEL(ADC3_BASE) |

◆ ADC3_DR

◆ ADC3_IER

◆ ADC3_ISR

◆ ADC3_JDR1

◆ ADC3_JDR2

◆ ADC3_JDR3

◆ ADC3_JDR4

◆ ADC3_JSQR

◆ ADC3_OFR1

◆ ADC3_OFR2

◆ ADC3_OFR3

◆ ADC3_OFR4

◆ ADC3_SMPR1

◆ ADC3_SMPR2

◆ ADC3_SQR1

◆ ADC3_SQR2

◆ ADC3_SQR3

◆ ADC3_SQR4

◆ ADC3_TR1

◆ ADC3_TR2

◆ ADC3_TR3

◆ ADC4_AWD2CR

| #define ADC4_AWD2CR ADC_AWD2CR(ADC4_BASE) |

◆ ADC4_AWD3CR

| #define ADC4_AWD3CR ADC_AWD3CR(ADC4_BASE) |

◆ ADC4_CALFACT

| #define ADC4_CALFACT ADC_CALFACT(ADC4_BASE) |

◆ ADC4_CFGR

◆ ADC4_CFGR1

◆ ADC4_CR

◆ ADC4_DIFSEL

| #define ADC4_DIFSEL ADC_DIFSEL(ADC4_BASE) |

◆ ADC4_DR

◆ ADC4_IER

◆ ADC4_ISR

◆ ADC4_JDR1

◆ ADC4_JDR2

◆ ADC4_JDR3

◆ ADC4_JDR4

◆ ADC4_JSQR

◆ ADC4_OFR1

◆ ADC4_OFR2

◆ ADC4_OFR3

◆ ADC4_OFR4

◆ ADC4_SMPR1

◆ ADC4_SMPR2

◆ ADC4_SQR1

◆ ADC4_SQR2

◆ ADC4_SQR3

◆ ADC4_SQR4

◆ ADC4_TR1

◆ ADC4_TR2

◆ ADC4_TR3

◆ ADC_CCR_CKMODE_CKX

◆ ADC_CCR_CKMODE_DIV1

◆ ADC_CCR_CKMODE_DIV2

◆ ADC_CCR_CKMODE_DIV4

◆ ADC_CCR_CKMODE_MASK

◆ ADC_CCR_DELAY_SHIFT

◆ ADC_CCR_DMACFG

◆ ADC_CCR_DUAL_MASK

◆ ADC_CCR_DUAL_SHIFT

◆ ADC_CCR_MDMA_12_10_BIT

◆ ADC_CCR_MDMA_8_6_BIT

◆ ADC_CCR_MDMA_DISABLE

◆ ADC_CCR_TSEN

◆ ADC_CCR_VBATEN

◆ ADC_CCR_VREFEN

◆ ADC_CFGR

◆ ADC_CFGR1_ALIGN

◆ ADC_CFGR1_DISCNUM_MASK

| #define ADC_CFGR1_DISCNUM_MASK (0x7 << ADC_CFGR1_DISCNUM_SHIFT) |

Definition at line 143 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_DISCNUM_SHIFT

| #define ADC_CFGR1_DISCNUM_SHIFT 17 |

Definition at line 142 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_DISCNUM_VAL

| #define ADC_CFGR1_DISCNUM_VAL | ( | x | ) | (((x) - 1) << ADC_CFGR1_DISCNUM_SHIFT) |

Definition at line 144 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_EXTSEL_MASK

| #define ADC_CFGR1_EXTSEL_MASK (0xf << ADC_CFGR1_EXTSEL_SHIFT) |

◆ ADC_CFGR1_EXTSEL_SHIFT

◆ ADC_CFGR1_EXTSEL_VAL

| #define ADC_CFGR1_EXTSEL_VAL | ( | x | ) | ((x) << ADC_CFGR1_EXTSEL_SHIFT) |

◆ ADC_CFGR1_JAUTO

| #define ADC_CFGR1_JAUTO (1 << 25) |

Definition at line 130 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_JAWD1EN

| #define ADC_CFGR1_JAWD1EN (1 << 24) |

Definition at line 133 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_JDISCEN

| #define ADC_CFGR1_JDISCEN (1 << 20) |

Definition at line 139 of file adc_common_v2_multi.h.

◆ ADC_CFGR1_JQM

| #define ADC_CFGR1_JQM (1 << 21) |

Definition at line 136 of file adc_common_v2_multi.h.

◆ ADC_CR_ADCALDIF

| #define ADC_CR_ADCALDIF (1 << 30) |

Definition at line 121 of file adc_common_v2_multi.h.

◆ ADC_CR_ADVREGEN_DISABLE

◆ ADC_CR_ADVREGEN_ENABLE

| #define ADC_CR_ADVREGEN_ENABLE (0x1 << 28) |

◆ ADC_CR_ADVREGEN_MASK

◆ ADC_CR_JADSTART

| #define ADC_CR_JADSTART (1 << 3) |

Definition at line 125 of file adc_common_v2_multi.h.

◆ ADC_CR_JADSTP

| #define ADC_CR_JADSTP (1 << 5) |

Definition at line 123 of file adc_common_v2_multi.h.

◆ ADC_CSR_ADRDY_MST

◆ ADC_CSR_ADRDY_SLV

◆ ADC_CSR_AWD1_MST

◆ ADC_CSR_AWD1_SLV

◆ ADC_CSR_AWD2_MST

◆ ADC_CSR_AWD2_SLV

◆ ADC_CSR_AWD3_MST

◆ ADC_CSR_AWD3_SLV

◆ ADC_CSR_EOC_MST

◆ ADC_CSR_EOC_SLV

◆ ADC_CSR_EOS_MST

◆ ADC_CSR_EOS_SLV

◆ ADC_CSR_EOSMP_MST

◆ ADC_CSR_EOSMP_SLV

◆ ADC_CSR_JEOC_MST

◆ ADC_CSR_JEOC_SLV

◆ ADC_CSR_JEOS_MST

◆ ADC_CSR_JEOS_SLV

◆ ADC_CSR_JQOVF_MST

◆ ADC_CSR_JQOVF_SLV

◆ ADC_CSR_OVR_MST

◆ ADC_CSR_OVR_SLV

◆ ADC_IER_AWD2IE

| #define ADC_IER_AWD2IE (1 << 8) |

Definition at line 112 of file adc_common_v2_multi.h.

◆ ADC_IER_AWD3IE

| #define ADC_IER_AWD3IE (1 << 9) |

Definition at line 110 of file adc_common_v2_multi.h.

◆ ADC_IER_JEOCIE

| #define ADC_IER_JEOCIE (1 << 5) |

Definition at line 116 of file adc_common_v2_multi.h.

◆ ADC_IER_JEOSIE

| #define ADC_IER_JEOSIE (1 << 6) |

Definition at line 114 of file adc_common_v2_multi.h.

◆ ADC_IER_JQOVFIE

| #define ADC_IER_JQOVFIE (1 << 10) |

Definition at line 108 of file adc_common_v2_multi.h.

◆ ADC_ISR_AWD2

| #define ADC_ISR_AWD2 (1 << 8) |

Definition at line 99 of file adc_common_v2_multi.h.

◆ ADC_ISR_AWD3

| #define ADC_ISR_AWD3 (1 << 9) |

Definition at line 97 of file adc_common_v2_multi.h.

◆ ADC_ISR_JEOC

| #define ADC_ISR_JEOC (1 << 5) |

Definition at line 103 of file adc_common_v2_multi.h.

◆ ADC_ISR_JEOS

| #define ADC_ISR_JEOS (1 << 6) |

Definition at line 101 of file adc_common_v2_multi.h.

◆ ADC_ISR_JQOVF

| #define ADC_ISR_JQOVF (1 << 10) |

Definition at line 95 of file adc_common_v2_multi.h.

◆ ADC_JSQR_JEXTEN_BOTH_EDGES

◆ ADC_JSQR_JEXTEN_DISABLED

◆ ADC_JSQR_JEXTEN_FALLING_EDGE

◆ ADC_JSQR_JEXTEN_MASK

◆ ADC_JSQR_JEXTEN_RISING_EDGE

◆ ADC_JSQR_JEXTSEL_EVENT_0

◆ ADC_JSQR_JEXTSEL_EVENT_1

◆ ADC_JSQR_JEXTSEL_EVENT_10

◆ ADC_JSQR_JEXTSEL_EVENT_11

◆ ADC_JSQR_JEXTSEL_EVENT_12

◆ ADC_JSQR_JEXTSEL_EVENT_13

◆ ADC_JSQR_JEXTSEL_EVENT_14

◆ ADC_JSQR_JEXTSEL_EVENT_15

◆ ADC_JSQR_JEXTSEL_EVENT_2

◆ ADC_JSQR_JEXTSEL_EVENT_3

◆ ADC_JSQR_JEXTSEL_EVENT_4

◆ ADC_JSQR_JEXTSEL_EVENT_5

◆ ADC_JSQR_JEXTSEL_EVENT_6

◆ ADC_JSQR_JEXTSEL_EVENT_7

◆ ADC_JSQR_JEXTSEL_EVENT_8

◆ ADC_JSQR_JEXTSEL_EVENT_9

◆ ADC_JSQR_JEXTSEL_MASK

◆ ADC_JSQR_JL_1_CONVERSION

◆ ADC_JSQR_JL_2_CONVERSIONS

◆ ADC_JSQR_JL_3_CONVERSIONS

◆ ADC_JSQR_JL_4_CONVERSIONS

◆ ADC_JSQR_JL_LSB

◆ ADC_JSQR_JL_SHIFT

◆ ADC_JSQR_JL_VAL

| #define ADC_JSQR_JL_VAL | ( | val | ) | (((val) - 1) << ADC_JSQR_JL_SHIFT) |

◆ ADC_JSQR_JSQ1_LSB

◆ ADC_JSQR_JSQ2_LSB

◆ ADC_JSQR_JSQ3_LSB

◆ ADC_JSQR_JSQ4_LSB

◆ ADC_JSQR_JSQ_VAL

| #define ADC_JSQR_JSQ_VAL | ( | n, | |

| val | |||

| ) | ((val) << (((n) - 1) * 6 + 8)) |

◆ ADC_OFR1_OFFSET1_EN

◆ ADC_OFR2_OFFSET2_EN

◆ ADC_OFR3_OFFSET3_EN

◆ ADC_OFR4_OFFSET4_EN

◆ ADC_SQR1_L_MASK

| #define ADC_SQR1_L_MASK 0xf |

Definition at line 149 of file adc_common_v2_multi.h.

◆ ADC_SQR1_L_SHIFT

| #define ADC_SQR1_L_SHIFT 0 |

Definition at line 148 of file adc_common_v2_multi.h.

◆ ADC_SQR1_SQ1_SHIFT

| #define ADC_SQR1_SQ1_SHIFT 6 |

Definition at line 151 of file adc_common_v2_multi.h.

◆ ADC_SQR1_SQ2_SHIFT

| #define ADC_SQR1_SQ2_SHIFT 12 |

Definition at line 152 of file adc_common_v2_multi.h.

◆ ADC_SQR1_SQ3_SHIFT

| #define ADC_SQR1_SQ3_SHIFT 18 |

Definition at line 153 of file adc_common_v2_multi.h.

◆ ADC_SQR1_SQ4_SHIFT

| #define ADC_SQR1_SQ4_SHIFT 24 |

Definition at line 154 of file adc_common_v2_multi.h.

◆ ADC_SQR2_SQ5_SHIFT

| #define ADC_SQR2_SQ5_SHIFT 0 |

Definition at line 155 of file adc_common_v2_multi.h.

◆ ADC_SQR2_SQ6_SHIFT

| #define ADC_SQR2_SQ6_SHIFT 6 |

Definition at line 156 of file adc_common_v2_multi.h.

◆ ADC_SQR2_SQ7_SHIFT

| #define ADC_SQR2_SQ7_SHIFT 12 |

Definition at line 157 of file adc_common_v2_multi.h.

◆ ADC_SQR2_SQ8_SHIFT

| #define ADC_SQR2_SQ8_SHIFT 18 |

Definition at line 158 of file adc_common_v2_multi.h.

◆ ADC_SQR2_SQ9_SHIFT

| #define ADC_SQR2_SQ9_SHIFT 24 |

Definition at line 159 of file adc_common_v2_multi.h.

◆ ADC_SQR3_SQ10_SHIFT

| #define ADC_SQR3_SQ10_SHIFT 0 |

Definition at line 160 of file adc_common_v2_multi.h.

◆ ADC_SQR3_SQ11_SHIFT

| #define ADC_SQR3_SQ11_SHIFT 6 |

Definition at line 161 of file adc_common_v2_multi.h.

◆ ADC_SQR3_SQ12_SHIFT

| #define ADC_SQR3_SQ12_SHIFT 12 |

Definition at line 162 of file adc_common_v2_multi.h.

◆ ADC_SQR3_SQ13_SHIFT

| #define ADC_SQR3_SQ13_SHIFT 18 |

Definition at line 163 of file adc_common_v2_multi.h.

◆ ADC_SQR3_SQ14_SHIFT

| #define ADC_SQR3_SQ14_SHIFT 24 |

Definition at line 164 of file adc_common_v2_multi.h.

◆ ADC_SQR4_SQ15_SHIFT

| #define ADC_SQR4_SQ15_SHIFT 0 |

Definition at line 165 of file adc_common_v2_multi.h.

◆ ADC_SQR4_SQ16_SHIFT

| #define ADC_SQR4_SQ16_SHIFT 6 |

Definition at line 166 of file adc_common_v2_multi.h.

◆ ADC_SQRx_SQx_MASK

| #define ADC_SQRx_SQx_MASK 0x1f |

Definition at line 150 of file adc_common_v2_multi.h.

Function Documentation

◆ adc_awd()

| bool adc_awd | ( | uint32_t | adc | ) |

ADC Read the Analog Watchdog Flag.

This flag is set when the converted voltage crosses the high or low thresholds.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. AWD flag.

Definition at line 696 of file adc.c.

References ADC_ISR, ADC_ISR_AWD1, ADC_ISR_AWD2, and ADC_ISR_AWD3.

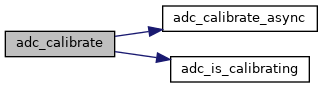

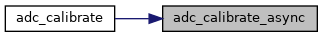

◆ adc_calibrate()

| void adc_calibrate | ( | uint32_t | adc | ) |

Start ADC calibration and wait for it to finish.

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 175 of file adc_common_v2.c.

References adc_calibrate_async(), and adc_is_calibrating().

◆ adc_calibrate_async()

| void adc_calibrate_async | ( | uint32_t | adc | ) |

Start the ADC calibration and immediately return.

- See also

- adc_calibrate

- adc_is_calibrating

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 156 of file adc_common_v2.c.

References ADC_CR, and ADC_CR_ADCAL.

Referenced by adc_calibrate().

◆ adc_clear_overrun_flag()

| void adc_clear_overrun_flag | ( | uint32_t | adc | ) |

ADC Clear Overrun Flags.

The overrun flag is cleared. Note that if an overrun occurs, DMA is terminated. The flag must be cleared and the DMA stream and ADC reinitialised to resume conversions (see the reference manual).

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 299 of file adc_common_v2.c.

References ADC_ISR, and ADC_ISR_OVR.

◆ adc_disable_all_awd_interrupt()

| void adc_disable_all_awd_interrupt | ( | uint32_t | adc | ) |

ADC Disable Analog Watchdog Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 360 of file adc.c.

References ADC_IER.

◆ adc_disable_analog_watchdog_injected()

| void adc_disable_analog_watchdog_injected | ( | uint32_t | adc | ) |

ADC Disable Analog Watchdog for Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 142 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_analog_watchdog_regular()

| void adc_disable_analog_watchdog_regular | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for Regular Conversions.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 114 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_automatic_injected_group_conversion()

| void adc_disable_automatic_injected_group_conversion | ( | uint32_t | adc | ) |

ADC Disable Automatic Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 234 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_delayed_conversion_mode()

| void adc_disable_delayed_conversion_mode | ( | uint32_t | adc | ) |

Enable Delayed Conversion Mode.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses

Definition at line 425 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_disable_discontinuous_mode_injected()

| void adc_disable_discontinuous_mode_injected | ( | uint32_t | adc | ) |

ADC Disable Discontinuous Mode for Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 205 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_discontinuous_mode_regular()

| void adc_disable_discontinuous_mode_regular | ( | uint32_t | adc | ) |

ADC Disable Discontinuous Mode for Regular Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 177 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_dma()

| void adc_disable_dma | ( | uint32_t | adc | ) |

ADC Disable DMA Transfers.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 250 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_disable_dma_circular_mode()

| void adc_disable_dma_circular_mode | ( | uint32_t | adc | ) |

Disable circular mode for DMA transfers.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 407 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_disable_eoc_interrupt()

| void adc_disable_eoc_interrupt | ( | uint32_t | adc | ) |

ADC Disable Regular End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 317 of file adc_common_v2.c.

References ADC_IER.

◆ adc_disable_eoc_interrupt_injected()

| void adc_disable_eoc_interrupt_injected | ( | uint32_t | adc | ) |

ADC Disable Injected End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 309 of file adc.c.

References ADC_IER.

◆ adc_disable_eos_interrupt()

| void adc_disable_eos_interrupt | ( | uint32_t | adc | ) |

ADC Disable Regular End-Of-Sequence Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 386 of file adc.c.

References ADC_IER.

◆ adc_disable_eos_interrupt_injected()

| void adc_disable_eos_interrupt_injected | ( | uint32_t | adc | ) |

ADC Disable Injected End-Of-Sequence Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 333 of file adc.c.

References ADC_IER.

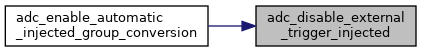

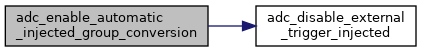

◆ adc_disable_external_trigger_injected()

| void adc_disable_external_trigger_injected | ( | uint32_t | adc | ) |

ADC Disable an External Trigger for Injected Channels.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 679 of file adc.c.

References ADC_JSQR.

Referenced by adc_enable_automatic_injected_group_conversion().

◆ adc_disable_external_trigger_regular()

| void adc_disable_external_trigger_regular | ( | uint32_t | adc | ) |

ADC Disable an External Trigger for Regular Channels.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 643 of file adc.c.

References ADC_CFGR1.

◆ adc_disable_overrun_interrupt()

| void adc_disable_overrun_interrupt | ( | uint32_t | adc | ) |

ADC Disable the Overrun Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 272 of file adc_common_v2.c.

References ADC_IER.

◆ adc_disable_regulator()

| void adc_disable_regulator | ( | uint32_t | adc | ) |

Disable the ADC Voltage regulator You can disable the adc vreg when not in use to save power.

- Parameters

-

[in] adc ADC block register address base

- See also

- adc_enable_regulator

Definition at line 723 of file adc.c.

References ADC_CR, and ADC_CR_ADVREGEN_DISABLE.

◆ adc_disable_temperature_sensor()

| void adc_disable_temperature_sensor | ( | void | ) |

Disable the temperature sensor (only)

- See also

- adc_enable_temperature_sensor

Definition at line 351 of file adc_common_v2.c.

◆ adc_disable_vrefint()

| void adc_disable_vrefint | ( | void | ) |

Disable the internal voltage reference (only)

- See also

- adc_enable_vrefint

Definition at line 372 of file adc_common_v2.c.

◆ adc_enable_all_awd_interrupt()

| void adc_enable_all_awd_interrupt | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 346 of file adc.c.

References ADC_IER, ADC_IER_AWD1IE, ADC_IER_AWD2IE, and ADC_IER_AWD3IE.

◆ adc_enable_analog_watchdog_injected()

| void adc_enable_analog_watchdog_injected | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for Injected Conversions.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 130 of file adc.c.

References ADC_CFGR1, and ADC_CFGR1_JAWD1EN.

◆ adc_enable_analog_watchdog_on_all_channels()

| void adc_enable_analog_watchdog_on_all_channels | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for All Regular and/or Injected Channels.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Note

- The analog watchdog must be enabled for either or both of the regular or injected channels. If neither are enabled, the analog watchdog feature will be disabled.

adc_enable_analog_watchdog_injected, adc_enable_analog_watchdog_regular.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 256 of file adc.c.

References ADC_CFGR1.

◆ adc_enable_analog_watchdog_on_selected_channel()

| void adc_enable_analog_watchdog_on_selected_channel | ( | uint32_t | adc, |

| uint8_t | channel | ||

| ) |

ADC Enable Analog Watchdog for a Selected Channel.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Note

- The analog watchdog must be enabled for either or both of the regular or injected channels. If neither are enabled, the analog watchdog feature will be disabled. If both are enabled, the same channel number is monitored adc_enable_analog_watchdog_injected, adc_enable_analog_watchdog_regular.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] channel Unsigned int8. ADC channel numbe adc_watchdog_channel

Definition at line 280 of file adc.c.

References ADC_CFGR1, ADC_CFGR1_AWD1CH_VAL, ADC_CFGR1_AWD1EN, and ADC_CFGR1_AWD1SGL.

◆ adc_enable_analog_watchdog_regular()

| void adc_enable_analog_watchdog_regular | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for Regular Conversions.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 99 of file adc.c.

References ADC_CFGR1, and ADC_CFGR1_AWD1EN.

◆ adc_enable_automatic_injected_group_conversion()

| void adc_enable_automatic_injected_group_conversion | ( | uint32_t | adc | ) |

ADC Enable Automatic Injected Conversions.

The ADC converts a defined injected group of channels immediately after the regular channels have been converted. The external trigger on the injected channels is disabled as required.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 221 of file adc.c.

References ADC_CFGR1, ADC_CFGR1_JAUTO, and adc_disable_external_trigger_injected().

◆ adc_enable_delayed_conversion_mode()

| void adc_enable_delayed_conversion_mode | ( | uint32_t | adc | ) |

Enable Delayed Conversion Mode.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses

Definition at line 416 of file adc_common_v2.c.

References ADC_CFGR1, and ADC_CFGR1_AUTDLY.

◆ adc_enable_discontinuous_mode_injected()

| void adc_enable_discontinuous_mode_injected | ( | uint32_t | adc | ) |

ADC Enable Discontinuous Mode for Injected Conversions.

In this mode the ADC converts sequentially one channel of the defined group of injected channels, cycling back to the first channel in the group once the entire group has been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 193 of file adc.c.

References ADC_CFGR1, and ADC_CFGR1_JDISCEN.

◆ adc_enable_discontinuous_mode_regular()

| void adc_enable_discontinuous_mode_regular | ( | uint32_t | adc, |

| uint8_t | length | ||

| ) |

ADC Enable Discontinuous Mode for Regular Conversions.

In this mode the ADC converts, on each trigger, a subgroup of up to 8 of the defined regular channel group. The subgroup is defined by the number of consecutive channels to be converted. After a subgroup has been converted the next trigger will start conversion of the immediately following subgroup of the same length or until the whole group has all been converted. When the whole group has been converted, the next trigger will restart conversion of the subgroup at the beginning of the whole group.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses [in] length Number of channels in the group adc_cr1_discnum

Definition at line 161 of file adc.c.

References ADC_CFGR1, ADC_CFGR1_DISCEN, and ADC_CFGR1_DISCNUM_SHIFT.

◆ adc_enable_dma()

| void adc_enable_dma | ( | uint32_t | adc | ) |

ADC Enable DMA Transfers.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 241 of file adc_common_v2.c.

References ADC_CFGR1, and ADC_CFGR1_DMAEN.

◆ adc_enable_dma_circular_mode()

| void adc_enable_dma_circular_mode | ( | uint32_t | adc | ) |

Enable circular mode for DMA transfers.

For this to work it needs to be ebabled on the DMA side as well.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 398 of file adc_common_v2.c.

References ADC_CFGR1, and ADC_CFGR1_DMACFG.

◆ adc_enable_eoc_interrupt()

| void adc_enable_eoc_interrupt | ( | uint32_t | adc | ) |

ADC Enable Regular End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 308 of file adc_common_v2.c.

References ADC_IER, and ADC_IER_EOCIE.

◆ adc_enable_eoc_interrupt_injected()

| void adc_enable_eoc_interrupt_injected | ( | uint32_t | adc | ) |

ADC Enable Injected End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 297 of file adc.c.

References ADC_IER, and ADC_IER_JEOCIE.

◆ adc_enable_eos_interrupt()

| void adc_enable_eos_interrupt | ( | uint32_t | adc | ) |

ADC Enable Regular End-Of-Sequence Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 374 of file adc.c.

References ADC_IER, and ADC_IER_EOSIE.

◆ adc_enable_eos_interrupt_injected()

| void adc_enable_eos_interrupt_injected | ( | uint32_t | adc | ) |

ADC Enable Injected End-Of-Sequence Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 321 of file adc.c.

References ADC_IER, and ADC_IER_JEOSIE.

◆ adc_enable_external_trigger_injected()

| void adc_enable_external_trigger_injected | ( | uint32_t | adc, |

| uint32_t | trigger, | ||

| uint32_t | polarity | ||

| ) |

ADC Enable an External Trigger for Injected Channels.

This enables an external trigger for set of defined injected channels, and sets the polarity of the trigger event: rising or falling edge or both.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] trigger Unsigned int8. Trigger identifier adc_trigger_injected [in] polarity Unsigned int32. Trigger polarity adc_trigger_polarity_injected

Definition at line 662 of file adc.c.

References ADC_JSQR, ADC_JSQR_JEXTEN_MASK, and ADC_JSQR_JEXTSEL_MASK.

◆ adc_enable_external_trigger_regular()

| void adc_enable_external_trigger_regular | ( | uint32_t | adc, |

| uint32_t | trigger, | ||

| uint32_t | polarity | ||

| ) |

ADC Enable an External Trigger for Regular Channels.

This enables an external trigger for set of defined regular channels, and sets the polarity of the trigger event: rising or falling edge or both. Note that if the trigger polarity is zero, triggering is disabled.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] trigger Unsigned int32. Trigger identifier adc_trigger_regular [in] polarity Unsigned int32. Trigger polarity adc_trigger_polarity_regular

Definition at line 626 of file adc.c.

References ADC_CFGR1, ADC_CFGR1_EXTEN_MASK, and ADC_CFGR1_EXTSEL_MASK.

◆ adc_enable_overrun_interrupt()

| void adc_enable_overrun_interrupt | ( | uint32_t | adc | ) |

ADC Enable the Overrun Interrupt.

The overrun interrupt is generated when data is not read from a result register before the next conversion is written. If DMA is enabled, all transfers are terminated and any conversion sequence is aborted.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 263 of file adc_common_v2.c.

References ADC_IER, and ADC_IER_OVRIE.

◆ adc_enable_regulator()

| void adc_enable_regulator | ( | uint32_t | adc | ) |

Enable the ADC Voltage regulator Before any use of the ADC, the ADC Voltage regulator must be enabled.

You must wait up to 10uSecs afterwards before trying anything else.

- Parameters

-

[in] adc ADC block register address base

- See also

- adc_disable_regulator

Definition at line 711 of file adc.c.

References ADC_CR, and ADC_CR_ADVREGEN_ENABLE.

◆ adc_enable_temperature_sensor()

| void adc_enable_temperature_sensor | ( | void | ) |

Enable the temperature sensor (only) The channel this is available on is unfortunately not consistent, even though the bit used to enable it is.

- See also

- adc_disable_temperature_sensor

Definition at line 342 of file adc_common_v2.c.

References ADC1, ADC_CCR, and ADC_CCR_TSEN.

◆ adc_enable_vrefint()

| void adc_enable_vrefint | ( | void | ) |

Enable the internal voltage reference (only) The channel this is available on is unfortunately not consistent, even though the bit used to enable it is.

FIXME - on f3, you can actually have it on ADC34 as well!

- See also

- adc_disable_vrefint

Definition at line 363 of file adc_common_v2.c.

References ADC1, ADC_CCR, and ADC_CCR_VREFEN.

◆ adc_eoc()

| bool adc_eoc | ( | uint32_t | adc | ) |

ADC Read the End-of-Conversion Flag.

This flag is set by hardware at the end of each regular conversion of a channel when a new data is available in the ADCx_DR register.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 49 of file adc_common_v2.c.

References ADC_ISR, and ADC_ISR_EOC.

◆ adc_eoc_injected()

| bool adc_eoc_injected | ( | uint32_t | adc | ) |

ADC Read the End-of-Conversion Flag for Injected Conversion.

This flag is set by hardware at the end of each injected conversion of a channel when a new data is available in the corresponding ADCx_JDRy register.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 491 of file adc.c.

References ADC_ISR, and ADC_ISR_JEOC.

◆ adc_eos()

| bool adc_eos | ( | uint32_t | adc | ) |

ADC Read the End-of-Sequence Flag for Regular Conversions.

This flag is set after all channels of an regular group have been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 63 of file adc_common_v2.c.

References ADC_ISR, and ADC_ISR_EOS.

◆ adc_eos_injected()

| bool adc_eos_injected | ( | uint32_t | adc | ) |

ADC Read the End-of-Sequence Flag for Injected Conversions.

This flag is set after all channels of an injected group have been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 506 of file adc.c.

References ADC_ISR, and ADC_ISR_JEOS.

◆ adc_get_overrun_flag()

| bool adc_get_overrun_flag | ( | uint32_t | adc | ) |

ADC Read the Overrun Flag.

The overrun flag is set when data is not read from a result register before the next conversion is written. If DMA is enabled, all transfers are terminated and any conversion sequence is aborted.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 285 of file adc_common_v2.c.

References ADC_ISR, and ADC_ISR_OVR.

◆ adc_is_calibrating()

| bool adc_is_calibrating | ( | uint32_t | adc | ) |

Is the ADC Calibrating?

- Parameters

-

adc ADC Block register address base ADC register base addresses

- Returns

- true if the adc is currently calibrating

Definition at line 166 of file adc_common_v2.c.

References ADC_CR, and ADC_CR_ADCAL.

Referenced by adc_calibrate().

◆ adc_is_power_off()

| bool adc_is_power_off | ( | uint32_t | adc | ) |

Is the ADC powered down?

- See also

- adc_power_off_async

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 132 of file adc_common_v2.c.

References ADC_CR, and ADC_CR_ADEN.

Referenced by adc_power_off(), and adc_power_off_async().

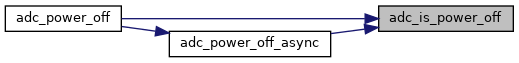

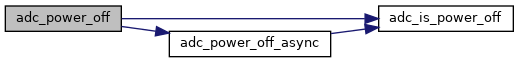

◆ adc_is_power_on()

| bool adc_is_power_on | ( | uint32_t | adc | ) |

Is the ADC powered up and ready?

- See also

- adc_power_on_async

- Parameters

-

adc ADC Block register address base ADC register base addresses

- Returns

- true if adc is ready for use

Definition at line 84 of file adc_common_v2.c.

References ADC_ISR, and ADC_ISR_ADRDY.

Referenced by adc_power_on().

◆ adc_power_off()

| void adc_power_off | ( | uint32_t | adc | ) |

Turn off the ADC This will actually block if it needs to turn off a currently running conversion, as per ref man.

- See also

- adc_power_off_async

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 144 of file adc_common_v2.c.

References adc_is_power_off(), and adc_power_off_async().

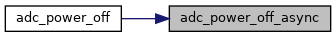

◆ adc_power_off_async()

| void adc_power_off_async | ( | uint32_t | adc | ) |

Turn off the ADC (async) This will actually block if it needs to turn off a currently running conversion, as per ref man.

(Handles injected on hardware that supports injected conversions.

- See also

- adc_wait_power_off

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 108 of file adc_common_v2.c.

References ADC_CR, ADC_CR_ADDIS, ADC_CR_ADSTART, ADC_CR_ADSTP, ADC_CR_JADSTART, ADC_CR_JADSTP, and adc_is_power_off().

Referenced by adc_power_off().

◆ adc_power_on()

| void adc_power_on | ( | uint32_t | adc | ) |

Turn on the ADC.

- See also

- adc_power_on_async

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 94 of file adc_common_v2.c.

References adc_is_power_on(), and adc_power_on_async().

◆ adc_power_on_async()

| void adc_power_on_async | ( | uint32_t | adc | ) |

Turn on the ADC (async)

- See also

- adc_wait_power_on

- Parameters

-

adc ADC Block register address base ADC register base addresses

Definition at line 73 of file adc_common_v2.c.

References ADC_CR, and ADC_CR_ADEN.

Referenced by adc_power_on().

◆ adc_read_injected()

| uint32_t adc_read_injected | ( | uint32_t | adc, |

| uint8_t | reg | ||

| ) |

ADC Read from an Injected Conversion Result Register.

The result read back from the selected injected result register (one of four) is 12 bits, right or left aligned within the first 16 bits. The result can have a negative value if the injected channel offset has been set

- See also

- adc_set_injected_offset.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] reg Unsigned int8. Register number (1 ... 4).

- Returns

- Unsigned int32 conversion result.

◆ adc_read_regular()

| uint32_t adc_read_regular | ( | uint32_t | adc | ) |

ADC Read from the Regular Conversion Result Register.

The result read back is 12 bits, right or left aligned within the first 16 bits.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- Unsigned int32 conversion result.

Definition at line 331 of file adc_common_v2.c.

References ADC_DR.

◆ adc_set_clk_prescale()

| void adc_set_clk_prescale | ( | uint32_t | adc, |

| uint32_t | prescale | ||

| ) |

ADC Set Clock Prescale.

The ADC clock taken from the APB2 clock can be scaled down by 2, 4, 6 or 8.

- Parameters

-

adc peripheral of choice ADC register base addresses [in] prescale Unsigned int32. Prescale value for ADC Clock adc_ccr_adcpre

Definition at line 585 of file adc.c.

References ADC_CCR.

◆ adc_set_continuous_conversion_mode()

| void adc_set_continuous_conversion_mode | ( | uint32_t | adc | ) |

Enable Continuous Conversion Mode In this mode the ADC starts a new conversion of a single channel or a channel group immediately following completion of the previous channel group conversion.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses

Definition at line 189 of file adc_common_v2.c.

References ADC_CFGR1, and ADC_CFGR1_CONT.

◆ adc_set_injected_offset()

| void adc_set_injected_offset | ( | uint32_t | adc, |

| uint8_t | reg, | ||

| uint32_t | offset | ||

| ) |

ADC Set the Injected Channel Data Offset.

This value is subtracted from the injected channel results after conversion is complete, and can result in negative results. A separate value can be specified for each injected data register.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] reg Unsigned int8. Register number (1 ... 4). [in] offset Unsigned int32.

Definition at line 554 of file adc.c.

References ADC_OFR1, ADC_OFR1_OFFSET1_EN, ADC_OFR2, ADC_OFR2_OFFSET2_EN, ADC_OFR3, ADC_OFR3_OFFSET3_EN, ADC_OFR4, and ADC_OFR4_OFFSET4_EN.

◆ adc_set_injected_sequence()

| void adc_set_injected_sequence | ( | uint32_t | adc, |

| uint8_t | length, | ||

| uint8_t | channel[] | ||

| ) |

ADC Set an Injected Channel Conversion Sequence.

Defines a sequence of channels to be converted as an injected group with a length from 1 to 4 channels. If this is called during conversion, the current conversion is reset and conversion begins again with the newly defined group.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] length Unsigned int8. Number of channels in the group. [in] channel Unsigned int8[]. Set of channels in sequence, integers 0..18

Definition at line 461 of file adc.c.

References ADC_JSQR, ADC_JSQR_JL_VAL, and ADC_JSQR_JSQ_VAL.

◆ adc_set_left_aligned()

| void adc_set_left_aligned | ( | uint32_t | adc | ) |

ADC Set the Data as Left Aligned.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 223 of file adc_common_v2.c.

References ADC_CFGR1, and ADC_CFGR1_ALIGN.

◆ adc_set_multi_mode()

| void adc_set_multi_mode | ( | uint32_t | adc, |

| uint32_t | mode | ||

| ) |

ADC set multi mode.

The multiple mode can uses these arrangement:

- ADC1 as master and ADC2 as slave

- ADC3 as master and ADC4 as slave

This setting is applied to ADC master only (ADC1 or ADC3).

The various modes possible are described in the reference manual.

- Parameters

-

adc peripheral of choice ADC register base addresses [in] mode Multiple mode selection from ADC Multi mode selection

Definition at line 605 of file adc.c.

References ADC_CCR, ADC_CCR_DUAL_MASK, and ADC_CCR_DUAL_SHIFT.

◆ adc_set_regular_sequence()

| void adc_set_regular_sequence | ( | uint32_t | adc, |

| uint8_t | length, | ||

| uint8_t | channel[] | ||

| ) |

ADC Set a Regular Channel Conversion Sequence.

Define a sequence of channels to be converted as a regular group with a length from 1 to 16 channels. If this is called during conversion, the current conversion is reset and conversion begins again with the newly defined group.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses [in] length Number of channels in the group, range 0..16 [in] channel Set of channels in sequence, range ADC Channel Numbers

Definition at line 100 of file adc_common_v2_multi.c.

References ADC_SQR1, ADC_SQR1_L_SHIFT, ADC_SQR2, ADC_SQR3, and ADC_SQR4.

◆ adc_set_resolution()

| void adc_set_resolution | ( | uint32_t | adc, |

| uint16_t | resolution | ||

| ) |

ADC Set Resolution.

ADC Resolution can be reduced from 12 bits to 10, 8 or 6 bits for a corresponding reduction in conversion time.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses) [in] resolution Unsigned int16. Resolution value (adc_api_res)

Definition at line 214 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_set_right_aligned()

| void adc_set_right_aligned | ( | uint32_t | adc | ) |

ADC Set the Data as Right Aligned.

- Parameters

-

[in] adc Unsigned int32. ADC base address (ADC register base addresses)

Definition at line 232 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_set_sample_time()

| void adc_set_sample_time | ( | uint32_t | adc, |

| uint8_t | channel, | ||

| uint8_t | time | ||

| ) |

ADC Set the Sample Time for a Single Channel.

The sampling time can be selected in ADC clock cycles, exact values depend on the device.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses [in] channel ADC Channel integer ADC Channel Numbers [in] time Sampling time selection from ADC Sample Time Selection values

Definition at line 47 of file adc_common_v2_multi.c.

◆ adc_set_sample_time_on_all_channels()

| void adc_set_sample_time_on_all_channels | ( | uint32_t | adc, |

| uint8_t | time | ||

| ) |

ADC Set the Sample Time for All Channels.

The sampling time can be selected in ADC clock cycles, exact values depend on the device.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses [in] time Sampling time selection from ADC Sample Time Selection values

Definition at line 72 of file adc_common_v2_multi.c.

◆ adc_set_single_conversion_mode()

| void adc_set_single_conversion_mode | ( | uint32_t | adc | ) |

Enable Single Conversion Mode In this mode the ADC performs a conversion of one channel or a channel group and stops.

- Parameters

-

[in] adc ADC block register address base ADC register base addresses

Definition at line 201 of file adc_common_v2.c.

References ADC_CFGR1.

◆ adc_set_watchdog_high_threshold()

| void adc_set_watchdog_high_threshold | ( | uint32_t | adc, |

| uint16_t | threshold | ||

| ) |

◆ adc_set_watchdog_low_threshold()

| void adc_set_watchdog_low_threshold | ( | uint32_t | adc, |

| uint16_t | threshold | ||

| ) |

◆ adc_start_conversion_injected()

| void adc_start_conversion_injected | ( | uint32_t | adc | ) |

ADC Software Triggered Conversion on Injected Channels.

This starts conversion on a set of defined injected channels. Depending on the configuration bits JEXTEN, a conversion will start immediately (software trigger configuration) or once an injected hardware trigger event occurs (hardware trigger configuration).

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 404 of file adc.c.

References ADC_CR, and ADC_CR_JADSTART.

◆ adc_start_conversion_regular()

| void adc_start_conversion_regular | ( | uint32_t | adc | ) |

ADC Software Triggered Conversion on Regular Channels.

This starts conversion on a set of defined regular channels. Depending on the configuration bits EXTEN, a conversion will start immediately (software trigger configuration) or once a regular hardware trigger event occurs (hardware trigger configuration)

- Parameters

-

[in] adc ADC block register address base ADC register base addresses

Definition at line 386 of file adc_common_v2.c.

References ADC_CR, and ADC_CR_ADSTART.