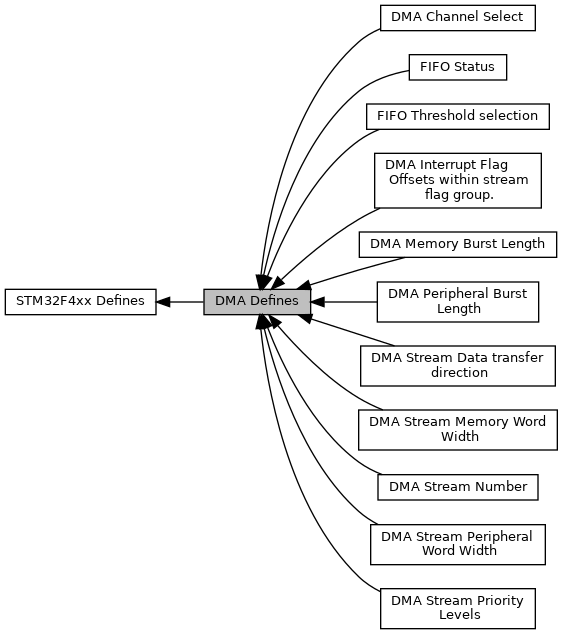

Defined Constants and Types for the STM32F4xx DMA Controller. More...

Functions | |

| void | dma_stream_reset (uint32_t dma, uint8_t stream) |

| DMA Stream Reset. More... | |

| void | dma_clear_interrupt_flags (uint32_t dma, uint8_t stream, uint32_t interrupts) |

| DMA Stream Clear Interrupt Flag. More... | |

| bool | dma_get_interrupt_flag (uint32_t dma, uint8_t stream, uint32_t interrupt) |

| DMA Stream Read Interrupt Flag. More... | |

| void | dma_set_transfer_mode (uint32_t dma, uint8_t stream, uint32_t direction) |

| DMA Stream Enable Transfer Direction. More... | |

| void | dma_set_priority (uint32_t dma, uint8_t stream, uint32_t prio) |

| DMA Stream Set Priority. More... | |

| void | dma_set_memory_size (uint32_t dma, uint8_t stream, uint32_t mem_size) |

| DMA Stream Set Memory Word Width. More... | |

| void | dma_set_peripheral_size (uint32_t dma, uint8_t stream, uint32_t peripheral_size) |

| DMA Stream Set Peripheral Word Width. More... | |

| void | dma_enable_memory_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Memory Increment after Transfer. More... | |

| void | dma_disable_memory_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Disable Memory Increment after Transfer. More... | |

| void | dma_enable_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Enable Variable Sized Peripheral Increment after Transfer. More... | |

| void | dma_disable_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Disable Peripheral Increment after Transfer. More... | |

| void | dma_enable_fixed_peripheral_increment_mode (uint32_t dma, uint8_t stream) |

| DMA Channel Enable Fixed Sized Peripheral Increment after Transfer. More... | |

| void | dma_enable_circular_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Memory Circular Mode. More... | |

| void | dma_channel_select (uint32_t dma, uint8_t stream, uint32_t channel) |

| DMA Stream Channel Select. More... | |

| void | dma_set_memory_burst (uint32_t dma, uint8_t stream, uint32_t burst) |

| DMA Stream Set Memory Burst Configuration. More... | |

| void | dma_set_peripheral_burst (uint32_t dma, uint8_t stream, uint32_t burst) |

| DMA Stream Set Peripheral Burst Configuration. More... | |

| void | dma_set_initial_target (uint32_t dma, uint8_t stream, uint8_t memory) |

| DMA Stream Set Initial Target Memory. More... | |

| uint8_t | dma_get_target (uint32_t dma, uint8_t stream) |

| DMA Stream Read Current Memory Target. More... | |

| void | dma_enable_double_buffer_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Double Buffer Mode. More... | |

| void | dma_disable_double_buffer_mode (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Double Buffer Mode. More... | |

| void | dma_set_peripheral_flow_control (uint32_t dma, uint8_t stream) |

| DMA Stream Set Peripheral Flow Control. More... | |

| void | dma_set_dma_flow_control (uint32_t dma, uint8_t stream) |

| DMA Stream Set DMA Flow Control. More... | |

| void | dma_enable_transfer_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Error. More... | |

| void | dma_disable_transfer_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Error. More... | |

| void | dma_enable_half_transfer_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Half Complete. More... | |

| void | dma_disable_half_transfer_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Half Complete. More... | |

| void | dma_enable_transfer_complete_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Transfer Complete. More... | |

| void | dma_disable_transfer_complete_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Transfer Complete. More... | |

| uint32_t | dma_fifo_status (uint32_t dma, uint8_t stream) |

| DMA Get FIFO Status. More... | |

| void | dma_enable_direct_mode_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Enable Interrupt on Direct Mode Error. More... | |

| void | dma_disable_direct_mode_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Stream Disable Interrupt on Direct Mode Error. More... | |

| void | dma_enable_fifo_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Enable Interrupt on FIFO Error. More... | |

| void | dma_disable_fifo_error_interrupt (uint32_t dma, uint8_t stream) |

| DMA Disable Interrupt on FIFO Error. More... | |

| void | dma_enable_direct_mode (uint32_t dma, uint8_t stream) |

| DMA Enable Direct Mode. More... | |

| void | dma_enable_fifo_mode (uint32_t dma, uint8_t stream) |

| DMA Enable FIFO Mode. More... | |

| void | dma_set_fifo_threshold (uint32_t dma, uint8_t stream, uint32_t threshold) |

| DMA Set FIFO Threshold. More... | |

| void | dma_enable_stream (uint32_t dma, uint8_t stream) |

| DMA Stream Enable. More... | |

| void | dma_disable_stream (uint32_t dma, uint8_t stream) |

| DMA Stream Disable. More... | |

| void | dma_set_peripheral_address (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Peripheral Address. More... | |

| void | dma_set_memory_address (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Base Memory Address 0. More... | |

| void | dma_set_memory_address_1 (uint32_t dma, uint8_t stream, uint32_t address) |

| DMA Stream Set the Base Memory Address 1. More... | |

| uint16_t | dma_get_number_of_data (uint32_t dma, uint8_t stream) |

| DMA Stream Get the Transfer Block Size. More... | |

| void | dma_set_number_of_data (uint32_t dma, uint8_t stream, uint16_t number) |

| DMA Stream Set the Transfer Block Size. More... | |

Detailed Description

Defined Constants and Types for the STM32F4xx DMA Controller.

- Version

- 1.0.0

- Date

- 30 November 2012

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ DMA1

| #define DMA1 DMA1_BASE |

Definition at line 44 of file dma_common_f24.h.

◆ DMA1_HIFCR

Definition at line 103 of file dma_common_f24.h.

◆ DMA1_HISR

Definition at line 93 of file dma_common_f24.h.

◆ DMA1_LIFCR

Definition at line 98 of file dma_common_f24.h.

◆ DMA1_LISR

Definition at line 88 of file dma_common_f24.h.

◆ DMA1_S0CR

| #define DMA1_S0CR DMA1_SCR(0) |

Definition at line 113 of file dma_common_f24.h.

◆ DMA1_S0FCR

| #define DMA1_S0FCR DMA1_SFCR(0) |

Definition at line 231 of file dma_common_f24.h.

◆ DMA1_S0M0AR

| #define DMA1_S0M0AR DMA1_SM0AR(0) |

Definition at line 184 of file dma_common_f24.h.

◆ DMA1_S0M1AR

| #define DMA1_S0M1AR DMA1_SM1AR(0) |

Definition at line 208 of file dma_common_f24.h.

◆ DMA1_S0NDTR

| #define DMA1_S0NDTR DMA1_SNDTR(0) |

Definition at line 136 of file dma_common_f24.h.

◆ DMA1_S0PAR

| #define DMA1_S0PAR DMA1_SPAR(0) |

Definition at line 160 of file dma_common_f24.h.

◆ DMA1_S1CR

| #define DMA1_S1CR DMA1_SCR(1) |

Definition at line 114 of file dma_common_f24.h.

◆ DMA1_S1FCR

| #define DMA1_S1FCR DMA1_SFCR(1) |

Definition at line 232 of file dma_common_f24.h.

◆ DMA1_S1M0AR

| #define DMA1_S1M0AR DMA1_SM0AR(1) |

Definition at line 185 of file dma_common_f24.h.

◆ DMA1_S1M1AR

| #define DMA1_S1M1AR DMA1_SM1AR(1) |

Definition at line 209 of file dma_common_f24.h.

◆ DMA1_S1NDTR

| #define DMA1_S1NDTR DMA1_SNDTR(1) |

Definition at line 137 of file dma_common_f24.h.

◆ DMA1_S1PAR

| #define DMA1_S1PAR DMA1_SPAR(1) |

Definition at line 161 of file dma_common_f24.h.

◆ DMA1_S2CR

| #define DMA1_S2CR DMA1_SCR(2) |

Definition at line 115 of file dma_common_f24.h.

◆ DMA1_S2FCR

| #define DMA1_S2FCR DMA1_SFCR(2) |

Definition at line 233 of file dma_common_f24.h.

◆ DMA1_S2M0AR

| #define DMA1_S2M0AR DMA1_SM0AR(2) |

Definition at line 186 of file dma_common_f24.h.

◆ DMA1_S2M1AR

| #define DMA1_S2M1AR DMA1_SM1AR(2) |

Definition at line 210 of file dma_common_f24.h.

◆ DMA1_S2NDTR

| #define DMA1_S2NDTR DMA1_SNDTR(2) |

Definition at line 138 of file dma_common_f24.h.

◆ DMA1_S2PAR

| #define DMA1_S2PAR DMA1_SPAR(2) |

Definition at line 162 of file dma_common_f24.h.

◆ DMA1_S3CR

| #define DMA1_S3CR DMA1_SCR(3) |

Definition at line 116 of file dma_common_f24.h.

◆ DMA1_S3FCR

| #define DMA1_S3FCR DMA1_SFCR(3) |

Definition at line 234 of file dma_common_f24.h.

◆ DMA1_S3M0AR

| #define DMA1_S3M0AR DMA1_SM0AR(3) |

Definition at line 187 of file dma_common_f24.h.

◆ DMA1_S3M1AR

| #define DMA1_S3M1AR DMA1_SM1AR(3) |

Definition at line 211 of file dma_common_f24.h.

◆ DMA1_S3NDTR

| #define DMA1_S3NDTR DMA1_SNDTR(3) |

Definition at line 139 of file dma_common_f24.h.

◆ DMA1_S3PAR

| #define DMA1_S3PAR DMA1_SPAR(3) |

Definition at line 163 of file dma_common_f24.h.

◆ DMA1_S4CR

| #define DMA1_S4CR DMA1_SCR(4) |

Definition at line 117 of file dma_common_f24.h.

◆ DMA1_S4FCR

| #define DMA1_S4FCR DMA1_SFCR(4) |

Definition at line 235 of file dma_common_f24.h.

◆ DMA1_S4M0AR

| #define DMA1_S4M0AR DMA1_SM0AR(4) |

Definition at line 188 of file dma_common_f24.h.

◆ DMA1_S4M1AR

| #define DMA1_S4M1AR DMA1_SM1AR(4) |

Definition at line 212 of file dma_common_f24.h.

◆ DMA1_S4NDTR

| #define DMA1_S4NDTR DMA1_SNDTR(4) |

Definition at line 140 of file dma_common_f24.h.

◆ DMA1_S4PAR

| #define DMA1_S4PAR DMA1_SPAR(4) |

Definition at line 164 of file dma_common_f24.h.

◆ DMA1_S5CR

| #define DMA1_S5CR DMA1_SCR(5) |

Definition at line 118 of file dma_common_f24.h.

◆ DMA1_S5FCR

| #define DMA1_S5FCR DMA1_SFCR(5) |

Definition at line 236 of file dma_common_f24.h.

◆ DMA1_S5M0AR

| #define DMA1_S5M0AR DMA1_SM0AR(5) |

Definition at line 189 of file dma_common_f24.h.

◆ DMA1_S5M1AR

| #define DMA1_S5M1AR DMA1_SM1AR(5) |

Definition at line 213 of file dma_common_f24.h.

◆ DMA1_S5NDTR

| #define DMA1_S5NDTR DMA1_SNDTR(5) |

Definition at line 141 of file dma_common_f24.h.

◆ DMA1_S5PAR

| #define DMA1_S5PAR DMA1_SPAR(5) |

Definition at line 165 of file dma_common_f24.h.

◆ DMA1_S6CR

| #define DMA1_S6CR DMA1_SCR(6) |

Definition at line 119 of file dma_common_f24.h.

◆ DMA1_S6FCR

| #define DMA1_S6FCR DMA1_SFCR(6) |

Definition at line 237 of file dma_common_f24.h.

◆ DMA1_S6M0AR

| #define DMA1_S6M0AR DMA1_SM0AR(6) |

Definition at line 190 of file dma_common_f24.h.

◆ DMA1_S6M1AR

| #define DMA1_S6M1AR DMA1_SM1AR(6) |

Definition at line 214 of file dma_common_f24.h.

◆ DMA1_S6NDTR

| #define DMA1_S6NDTR DMA1_SNDTR(6) |

Definition at line 142 of file dma_common_f24.h.

◆ DMA1_S6PAR

| #define DMA1_S6PAR DMA1_SPAR(6) |

Definition at line 166 of file dma_common_f24.h.

◆ DMA1_S7CR

| #define DMA1_S7CR DMA1_SCR(7) |

Definition at line 120 of file dma_common_f24.h.

◆ DMA1_S7FCR

| #define DMA1_S7FCR DMA1_SFCR(7) |

Definition at line 238 of file dma_common_f24.h.

◆ DMA1_S7M0AR

| #define DMA1_S7M0AR DMA1_SM0AR(7) |

Definition at line 191 of file dma_common_f24.h.

◆ DMA1_S7M1AR

| #define DMA1_S7M1AR DMA1_SM1AR(7) |

Definition at line 215 of file dma_common_f24.h.

◆ DMA1_S7NDTR

| #define DMA1_S7NDTR DMA1_SNDTR(7) |

Definition at line 143 of file dma_common_f24.h.

◆ DMA1_S7PAR

| #define DMA1_S7PAR DMA1_SPAR(7) |

Definition at line 167 of file dma_common_f24.h.

◆ DMA1_SCR

Definition at line 110 of file dma_common_f24.h.

◆ DMA1_SFCR

Definition at line 228 of file dma_common_f24.h.

◆ DMA1_SM0AR

Definition at line 181 of file dma_common_f24.h.

◆ DMA1_SM1AR

Definition at line 205 of file dma_common_f24.h.

◆ DMA1_SNDTR

Definition at line 133 of file dma_common_f24.h.

◆ DMA1_SPAR

Definition at line 157 of file dma_common_f24.h.

◆ DMA1_STREAM

| #define DMA1_STREAM | ( | n | ) | DMA_STREAM(DMA1, (n)) |

Definition at line 63 of file dma_common_f24.h.

◆ DMA1_STREAM0

| #define DMA1_STREAM0 DMA1_STREAM(0) |

Definition at line 66 of file dma_common_f24.h.

◆ DMA1_STREAM1

| #define DMA1_STREAM1 DMA1_STREAM(1) |

Definition at line 67 of file dma_common_f24.h.

◆ DMA1_STREAM2

| #define DMA1_STREAM2 DMA1_STREAM(2) |

Definition at line 68 of file dma_common_f24.h.

◆ DMA1_STREAM3

| #define DMA1_STREAM3 DMA1_STREAM(3) |

Definition at line 69 of file dma_common_f24.h.

◆ DMA1_STREAM4

| #define DMA1_STREAM4 DMA1_STREAM(4) |

Definition at line 70 of file dma_common_f24.h.

◆ DMA1_STREAM5

| #define DMA1_STREAM5 DMA1_STREAM(5) |

Definition at line 71 of file dma_common_f24.h.

◆ DMA1_STREAM6

| #define DMA1_STREAM6 DMA1_STREAM(6) |

Definition at line 72 of file dma_common_f24.h.

◆ DMA1_STREAM7

| #define DMA1_STREAM7 DMA1_STREAM(7) |

Definition at line 73 of file dma_common_f24.h.

◆ DMA2

| #define DMA2 DMA2_BASE |

Definition at line 45 of file dma_common_f24.h.

◆ DMA2_HIFCR

Definition at line 104 of file dma_common_f24.h.

◆ DMA2_HISR

Definition at line 94 of file dma_common_f24.h.

◆ DMA2_LIFCR

Definition at line 99 of file dma_common_f24.h.

◆ DMA2_LISR

Definition at line 89 of file dma_common_f24.h.

◆ DMA2_S0CR

| #define DMA2_S0CR DMA2_SCR(0) |

Definition at line 122 of file dma_common_f24.h.

◆ DMA2_S0FCR

| #define DMA2_S0FCR DMA2_SFCR(0) |

Definition at line 240 of file dma_common_f24.h.

◆ DMA2_S0M0AR

| #define DMA2_S0M0AR DMA2_SM0AR(0) |

Definition at line 193 of file dma_common_f24.h.

◆ DMA2_S0M1AR

| #define DMA2_S0M1AR DMA2_SM1AR(0) |

Definition at line 217 of file dma_common_f24.h.

◆ DMA2_S0NDTR

| #define DMA2_S0NDTR DMA2_SNDTR(0) |

Definition at line 145 of file dma_common_f24.h.

◆ DMA2_S0PAR

| #define DMA2_S0PAR DMA2_SPAR(0) |

Definition at line 169 of file dma_common_f24.h.

◆ DMA2_S1CR

| #define DMA2_S1CR DMA2_SCR(1) |

Definition at line 123 of file dma_common_f24.h.

◆ DMA2_S1FCR

| #define DMA2_S1FCR DMA2_SFCR(1) |

Definition at line 241 of file dma_common_f24.h.

◆ DMA2_S1M0AR

| #define DMA2_S1M0AR DMA2_SM0AR(1) |

Definition at line 194 of file dma_common_f24.h.

◆ DMA2_S1M1AR

| #define DMA2_S1M1AR DMA2_SM1AR(1) |

Definition at line 218 of file dma_common_f24.h.

◆ DMA2_S1NDTR

| #define DMA2_S1NDTR DMA2_SNDTR(1) |

Definition at line 146 of file dma_common_f24.h.

◆ DMA2_S1PAR

| #define DMA2_S1PAR DMA2_SPAR(1) |

Definition at line 170 of file dma_common_f24.h.

◆ DMA2_S2CR

| #define DMA2_S2CR DMA2_SCR(2) |

Definition at line 124 of file dma_common_f24.h.

◆ DMA2_S2FCR

| #define DMA2_S2FCR DMA2_SFCR(2) |

Definition at line 242 of file dma_common_f24.h.

◆ DMA2_S2M0AR

| #define DMA2_S2M0AR DMA2_SM0AR(2) |

Definition at line 195 of file dma_common_f24.h.

◆ DMA2_S2M1AR

| #define DMA2_S2M1AR DMA2_SM1AR(2) |

Definition at line 219 of file dma_common_f24.h.

◆ DMA2_S2NDTR

| #define DMA2_S2NDTR DMA2_SNDTR(2) |

Definition at line 147 of file dma_common_f24.h.

◆ DMA2_S2PAR

| #define DMA2_S2PAR DMA2_SPAR(2) |

Definition at line 171 of file dma_common_f24.h.

◆ DMA2_S3CR

| #define DMA2_S3CR DMA2_SCR(3) |

Definition at line 125 of file dma_common_f24.h.

◆ DMA2_S3FCR

| #define DMA2_S3FCR DMA2_SFCR(3) |

Definition at line 243 of file dma_common_f24.h.

◆ DMA2_S3M0AR

| #define DMA2_S3M0AR DMA2_SM0AR(3) |

Definition at line 196 of file dma_common_f24.h.

◆ DMA2_S3M1AR

| #define DMA2_S3M1AR DMA2_SM1AR(3) |

Definition at line 220 of file dma_common_f24.h.

◆ DMA2_S3NDTR

| #define DMA2_S3NDTR DMA2_SNDTR(3) |

Definition at line 148 of file dma_common_f24.h.

◆ DMA2_S3PAR

| #define DMA2_S3PAR DMA2_SPAR(3) |

Definition at line 172 of file dma_common_f24.h.

◆ DMA2_S4CR

| #define DMA2_S4CR DMA2_SCR(4) |

Definition at line 126 of file dma_common_f24.h.

◆ DMA2_S4FCR

| #define DMA2_S4FCR DMA2_SFCR(4) |

Definition at line 244 of file dma_common_f24.h.

◆ DMA2_S4M0AR

| #define DMA2_S4M0AR DMA2_SM0AR(4) |

Definition at line 197 of file dma_common_f24.h.

◆ DMA2_S4M1AR

| #define DMA2_S4M1AR DMA2_SM1AR(4) |

Definition at line 221 of file dma_common_f24.h.

◆ DMA2_S4NDTR

| #define DMA2_S4NDTR DMA2_SNDTR(4) |

Definition at line 149 of file dma_common_f24.h.

◆ DMA2_S4PAR

| #define DMA2_S4PAR DMA2_SPAR(4) |

Definition at line 173 of file dma_common_f24.h.

◆ DMA2_S5CR

| #define DMA2_S5CR DMA2_SCR(5) |

Definition at line 127 of file dma_common_f24.h.

◆ DMA2_S5FCR

| #define DMA2_S5FCR DMA2_SFCR(5) |

Definition at line 245 of file dma_common_f24.h.

◆ DMA2_S5M0AR

| #define DMA2_S5M0AR DMA2_SM0AR(5) |

Definition at line 198 of file dma_common_f24.h.

◆ DMA2_S5M1AR

| #define DMA2_S5M1AR DMA2_SM1AR(5) |

Definition at line 222 of file dma_common_f24.h.

◆ DMA2_S5NDTR

| #define DMA2_S5NDTR DMA2_SNDTR(5) |

Definition at line 150 of file dma_common_f24.h.

◆ DMA2_S5PAR

| #define DMA2_S5PAR DMA2_SPAR(5) |

Definition at line 174 of file dma_common_f24.h.

◆ DMA2_S6CR

| #define DMA2_S6CR DMA2_SCR(6) |

Definition at line 128 of file dma_common_f24.h.

◆ DMA2_S6FCR

| #define DMA2_S6FCR DMA2_SFCR(6) |

Definition at line 246 of file dma_common_f24.h.

◆ DMA2_S6M0AR

| #define DMA2_S6M0AR DMA2_SM0AR(6) |

Definition at line 199 of file dma_common_f24.h.

◆ DMA2_S6M1AR

| #define DMA2_S6M1AR DMA2_SM1AR(6) |

Definition at line 223 of file dma_common_f24.h.

◆ DMA2_S6NDTR

| #define DMA2_S6NDTR DMA2_SNDTR(6) |

Definition at line 151 of file dma_common_f24.h.

◆ DMA2_S6PAR

| #define DMA2_S6PAR DMA2_SPAR(6) |

Definition at line 175 of file dma_common_f24.h.

◆ DMA2_S7CR

| #define DMA2_S7CR DMA2_SCR(7) |

Definition at line 129 of file dma_common_f24.h.

◆ DMA2_S7FCR

| #define DMA2_S7FCR DMA2_SFCR(7) |

Definition at line 247 of file dma_common_f24.h.

◆ DMA2_S7M0AR

| #define DMA2_S7M0AR DMA2_SM0AR(7) |

Definition at line 200 of file dma_common_f24.h.

◆ DMA2_S7M1AR

| #define DMA2_S7M1AR DMA2_SM1AR(7) |

Definition at line 224 of file dma_common_f24.h.

◆ DMA2_S7NDTR

| #define DMA2_S7NDTR DMA2_SNDTR(7) |

Definition at line 152 of file dma_common_f24.h.

◆ DMA2_S7PAR

| #define DMA2_S7PAR DMA2_SPAR(7) |

Definition at line 176 of file dma_common_f24.h.

◆ DMA2_SCR

Definition at line 111 of file dma_common_f24.h.

◆ DMA2_SFCR

Definition at line 229 of file dma_common_f24.h.

◆ DMA2_SM0AR

Definition at line 182 of file dma_common_f24.h.

◆ DMA2_SM1AR

Definition at line 206 of file dma_common_f24.h.

◆ DMA2_SNDTR

Definition at line 134 of file dma_common_f24.h.

◆ DMA2_SPAR

Definition at line 158 of file dma_common_f24.h.

◆ DMA2_STREAM

| #define DMA2_STREAM | ( | n | ) | DMA_STREAM(DMA2, (n)) |

Definition at line 64 of file dma_common_f24.h.

◆ DMA2_STREAM0

| #define DMA2_STREAM0 DMA2_STREAM(0) |

Definition at line 75 of file dma_common_f24.h.

◆ DMA2_STREAM1

| #define DMA2_STREAM1 DMA2_STREAM(1) |

Definition at line 76 of file dma_common_f24.h.

◆ DMA2_STREAM2

| #define DMA2_STREAM2 DMA2_STREAM(2) |

Definition at line 77 of file dma_common_f24.h.

◆ DMA2_STREAM3

| #define DMA2_STREAM3 DMA2_STREAM(3) |

Definition at line 78 of file dma_common_f24.h.

◆ DMA2_STREAM4

| #define DMA2_STREAM4 DMA2_STREAM(4) |

Definition at line 79 of file dma_common_f24.h.

◆ DMA2_STREAM5

| #define DMA2_STREAM5 DMA2_STREAM(5) |

Definition at line 80 of file dma_common_f24.h.

◆ DMA2_STREAM6

| #define DMA2_STREAM6 DMA2_STREAM(6) |

Definition at line 81 of file dma_common_f24.h.

◆ DMA2_STREAM7

| #define DMA2_STREAM7 DMA2_STREAM(7) |

Definition at line 82 of file dma_common_f24.h.

◆ DMA_HIFCR

| #define DMA_HIFCR | ( | port | ) | MMIO32((port) + 0x0C) |

Definition at line 102 of file dma_common_f24.h.

◆ DMA_HIFCR_CDMEIF4

| #define DMA_HIFCR_CDMEIF4 (1 << 2) |

Definition at line 358 of file dma_common_f24.h.

◆ DMA_HIFCR_CDMEIF5

| #define DMA_HIFCR_CDMEIF5 (1 << 8) |

Definition at line 364 of file dma_common_f24.h.

◆ DMA_HIFCR_CDMEIF6

| #define DMA_HIFCR_CDMEIF6 (1 << 18) |

Definition at line 370 of file dma_common_f24.h.

◆ DMA_HIFCR_CDMEIF7

| #define DMA_HIFCR_CDMEIF7 (1 << 24) |

Definition at line 376 of file dma_common_f24.h.

◆ DMA_HIFCR_CFEIF4

| #define DMA_HIFCR_CFEIF4 (1 << 0) |

Definition at line 357 of file dma_common_f24.h.

◆ DMA_HIFCR_CFEIF5

| #define DMA_HIFCR_CFEIF5 (1 << 6) |

Definition at line 363 of file dma_common_f24.h.

◆ DMA_HIFCR_CFEIF6

| #define DMA_HIFCR_CFEIF6 (1 << 16) |

Definition at line 369 of file dma_common_f24.h.

◆ DMA_HIFCR_CFEIF7

| #define DMA_HIFCR_CFEIF7 (1 << 22) |

Definition at line 375 of file dma_common_f24.h.

◆ DMA_HIFCR_CHTIF4

| #define DMA_HIFCR_CHTIF4 (1 << 4) |

Definition at line 360 of file dma_common_f24.h.

◆ DMA_HIFCR_CHTIF5

| #define DMA_HIFCR_CHTIF5 (1 << 10) |

Definition at line 366 of file dma_common_f24.h.

◆ DMA_HIFCR_CHTIF6

| #define DMA_HIFCR_CHTIF6 (1 << 20) |

Definition at line 372 of file dma_common_f24.h.

◆ DMA_HIFCR_CHTIF7

| #define DMA_HIFCR_CHTIF7 (1 << 26) |

Definition at line 378 of file dma_common_f24.h.

◆ DMA_HIFCR_CTCIF4

| #define DMA_HIFCR_CTCIF4 (1 << 5) |

Definition at line 361 of file dma_common_f24.h.

◆ DMA_HIFCR_CTCIF5

| #define DMA_HIFCR_CTCIF5 (1 << 11) |

Definition at line 367 of file dma_common_f24.h.

◆ DMA_HIFCR_CTCIF6

| #define DMA_HIFCR_CTCIF6 (1 << 21) |

Definition at line 373 of file dma_common_f24.h.

◆ DMA_HIFCR_CTCIF7

| #define DMA_HIFCR_CTCIF7 (1 << 27) |

Definition at line 379 of file dma_common_f24.h.

◆ DMA_HIFCR_CTEIF4

| #define DMA_HIFCR_CTEIF4 (1 << 3) |

Definition at line 359 of file dma_common_f24.h.

◆ DMA_HIFCR_CTEIF5

| #define DMA_HIFCR_CTEIF5 (1 << 9) |

Definition at line 365 of file dma_common_f24.h.

◆ DMA_HIFCR_CTEIF6

| #define DMA_HIFCR_CTEIF6 (1 << 19) |

Definition at line 371 of file dma_common_f24.h.

◆ DMA_HIFCR_CTEIF7

| #define DMA_HIFCR_CTEIF7 (1 << 25) |

Definition at line 377 of file dma_common_f24.h.

◆ DMA_HISR

| #define DMA_HISR | ( | port | ) | MMIO32((port) + 0x04) |

Definition at line 92 of file dma_common_f24.h.

◆ DMA_HISR_DMEIF4

| #define DMA_HISR_DMEIF4 (1 << 2) |

Definition at line 306 of file dma_common_f24.h.

◆ DMA_HISR_DMEIF5

| #define DMA_HISR_DMEIF5 (1 << 8) |

Definition at line 312 of file dma_common_f24.h.

◆ DMA_HISR_DMEIF6

| #define DMA_HISR_DMEIF6 (1 << 18) |

Definition at line 318 of file dma_common_f24.h.

◆ DMA_HISR_DMEIF7

| #define DMA_HISR_DMEIF7 (1 << 24) |

Definition at line 324 of file dma_common_f24.h.

◆ DMA_HISR_FEIF4

| #define DMA_HISR_FEIF4 (1 << 0) |

Definition at line 305 of file dma_common_f24.h.

◆ DMA_HISR_FEIF5

| #define DMA_HISR_FEIF5 (1 << 6) |

Definition at line 311 of file dma_common_f24.h.

◆ DMA_HISR_FEIF6

| #define DMA_HISR_FEIF6 (1 << 16) |

Definition at line 317 of file dma_common_f24.h.

◆ DMA_HISR_FEIF7

| #define DMA_HISR_FEIF7 (1 << 22) |

Definition at line 323 of file dma_common_f24.h.

◆ DMA_HISR_HTIF4

| #define DMA_HISR_HTIF4 (1 << 4) |

Definition at line 308 of file dma_common_f24.h.

◆ DMA_HISR_HTIF5

| #define DMA_HISR_HTIF5 (1 << 10) |

Definition at line 314 of file dma_common_f24.h.

◆ DMA_HISR_HTIF6

| #define DMA_HISR_HTIF6 (1 << 20) |

Definition at line 320 of file dma_common_f24.h.

◆ DMA_HISR_HTIF7

| #define DMA_HISR_HTIF7 (1 << 26) |

Definition at line 326 of file dma_common_f24.h.

◆ DMA_HISR_TCIF4

| #define DMA_HISR_TCIF4 (1 << 5) |

Definition at line 309 of file dma_common_f24.h.

◆ DMA_HISR_TCIF5

| #define DMA_HISR_TCIF5 (1 << 11) |

Definition at line 315 of file dma_common_f24.h.

◆ DMA_HISR_TCIF6

| #define DMA_HISR_TCIF6 (1 << 21) |

Definition at line 321 of file dma_common_f24.h.

◆ DMA_HISR_TCIF7

| #define DMA_HISR_TCIF7 (1 << 27) |

Definition at line 327 of file dma_common_f24.h.

◆ DMA_HISR_TEIF4

| #define DMA_HISR_TEIF4 (1 << 3) |

Definition at line 307 of file dma_common_f24.h.

◆ DMA_HISR_TEIF5

| #define DMA_HISR_TEIF5 (1 << 9) |

Definition at line 313 of file dma_common_f24.h.

◆ DMA_HISR_TEIF6

| #define DMA_HISR_TEIF6 (1 << 19) |

Definition at line 319 of file dma_common_f24.h.

◆ DMA_HISR_TEIF7

| #define DMA_HISR_TEIF7 (1 << 25) |

Definition at line 325 of file dma_common_f24.h.

◆ DMA_ISR_FLAGS

| #define DMA_ISR_FLAGS |

Definition at line 273 of file dma_common_f24.h.

◆ DMA_ISR_MASK

| #define DMA_ISR_MASK | ( | stream | ) | (DMA_ISR_FLAGS << DMA_ISR_OFFSET(stream)) |

Definition at line 275 of file dma_common_f24.h.

◆ DMA_ISR_OFFSET

| #define DMA_ISR_OFFSET | ( | stream | ) | (6*((stream) & 0x01)+16*(((stream) & 0x02) >> 1)) |

Definition at line 272 of file dma_common_f24.h.

◆ DMA_LIFCR

| #define DMA_LIFCR | ( | port | ) | MMIO32((port) + 0x08) |

Definition at line 97 of file dma_common_f24.h.

◆ DMA_LIFCR_CDMEIF0

| #define DMA_LIFCR_CDMEIF0 (1 << 2) |

Definition at line 332 of file dma_common_f24.h.

◆ DMA_LIFCR_CDMEIF1

| #define DMA_LIFCR_CDMEIF1 (1 << 8) |

Definition at line 338 of file dma_common_f24.h.

◆ DMA_LIFCR_CDMEIF2

| #define DMA_LIFCR_CDMEIF2 (1 << 18) |

Definition at line 344 of file dma_common_f24.h.

◆ DMA_LIFCR_CDMEIF3

| #define DMA_LIFCR_CDMEIF3 (1 << 24) |

Definition at line 350 of file dma_common_f24.h.

◆ DMA_LIFCR_CFEIF0

| #define DMA_LIFCR_CFEIF0 (1 << 0) |

Definition at line 331 of file dma_common_f24.h.

◆ DMA_LIFCR_CFEIF1

| #define DMA_LIFCR_CFEIF1 (1 << 6) |

Definition at line 337 of file dma_common_f24.h.

◆ DMA_LIFCR_CFEIF2

| #define DMA_LIFCR_CFEIF2 (1 << 16) |

Definition at line 343 of file dma_common_f24.h.

◆ DMA_LIFCR_CFEIF3

| #define DMA_LIFCR_CFEIF3 (1 << 22) |

Definition at line 349 of file dma_common_f24.h.

◆ DMA_LIFCR_CHTIF0

| #define DMA_LIFCR_CHTIF0 (1 << 4) |

Definition at line 334 of file dma_common_f24.h.

◆ DMA_LIFCR_CHTIF1

| #define DMA_LIFCR_CHTIF1 (1 << 10) |

Definition at line 340 of file dma_common_f24.h.

◆ DMA_LIFCR_CHTIF2

| #define DMA_LIFCR_CHTIF2 (1 << 20) |

Definition at line 346 of file dma_common_f24.h.

◆ DMA_LIFCR_CHTIF3

| #define DMA_LIFCR_CHTIF3 (1 << 26) |

Definition at line 352 of file dma_common_f24.h.

◆ DMA_LIFCR_CTCIF0

| #define DMA_LIFCR_CTCIF0 (1 << 5) |

Definition at line 335 of file dma_common_f24.h.

◆ DMA_LIFCR_CTCIF1

| #define DMA_LIFCR_CTCIF1 (1 << 11) |

Definition at line 341 of file dma_common_f24.h.

◆ DMA_LIFCR_CTCIF2

| #define DMA_LIFCR_CTCIF2 (1 << 21) |

Definition at line 347 of file dma_common_f24.h.

◆ DMA_LIFCR_CTCIF3

| #define DMA_LIFCR_CTCIF3 (1 << 27) |

Definition at line 353 of file dma_common_f24.h.

◆ DMA_LIFCR_CTEIF0

| #define DMA_LIFCR_CTEIF0 (1 << 3) |

Definition at line 333 of file dma_common_f24.h.

◆ DMA_LIFCR_CTEIF1

| #define DMA_LIFCR_CTEIF1 (1 << 9) |

Definition at line 339 of file dma_common_f24.h.

◆ DMA_LIFCR_CTEIF2

| #define DMA_LIFCR_CTEIF2 (1 << 19) |

Definition at line 345 of file dma_common_f24.h.

◆ DMA_LIFCR_CTEIF3

| #define DMA_LIFCR_CTEIF3 (1 << 25) |

Definition at line 351 of file dma_common_f24.h.

◆ DMA_LISR

| #define DMA_LISR | ( | port | ) | MMIO32((port) + 0x00) |

Definition at line 87 of file dma_common_f24.h.

◆ DMA_LISR_DMEIF0

| #define DMA_LISR_DMEIF0 (1 << 2) |

Definition at line 280 of file dma_common_f24.h.

◆ DMA_LISR_DMEIF1

| #define DMA_LISR_DMEIF1 (1 << 8) |

Definition at line 286 of file dma_common_f24.h.

◆ DMA_LISR_DMEIF2

| #define DMA_LISR_DMEIF2 (1 << 18) |

Definition at line 292 of file dma_common_f24.h.

◆ DMA_LISR_DMEIF3

| #define DMA_LISR_DMEIF3 (1 << 24) |

Definition at line 298 of file dma_common_f24.h.

◆ DMA_LISR_FEIF0

| #define DMA_LISR_FEIF0 (1 << 0) |

Definition at line 279 of file dma_common_f24.h.

◆ DMA_LISR_FEIF1

| #define DMA_LISR_FEIF1 (1 << 6) |

Definition at line 285 of file dma_common_f24.h.

◆ DMA_LISR_FEIF2

| #define DMA_LISR_FEIF2 (1 << 16) |

Definition at line 291 of file dma_common_f24.h.

◆ DMA_LISR_FEIF3

| #define DMA_LISR_FEIF3 (1 << 22) |

Definition at line 297 of file dma_common_f24.h.

◆ DMA_LISR_HTIF0

| #define DMA_LISR_HTIF0 (1 << 4) |

Definition at line 282 of file dma_common_f24.h.

◆ DMA_LISR_HTIF1

| #define DMA_LISR_HTIF1 (1 << 10) |

Definition at line 288 of file dma_common_f24.h.

◆ DMA_LISR_HTIF2

| #define DMA_LISR_HTIF2 (1 << 20) |

Definition at line 294 of file dma_common_f24.h.

◆ DMA_LISR_HTIF3

| #define DMA_LISR_HTIF3 (1 << 26) |

Definition at line 300 of file dma_common_f24.h.

◆ DMA_LISR_TCIF0

| #define DMA_LISR_TCIF0 (1 << 5) |

Definition at line 283 of file dma_common_f24.h.

◆ DMA_LISR_TCIF1

| #define DMA_LISR_TCIF1 (1 << 11) |

Definition at line 289 of file dma_common_f24.h.

◆ DMA_LISR_TCIF2

| #define DMA_LISR_TCIF2 (1 << 21) |

Definition at line 295 of file dma_common_f24.h.

◆ DMA_LISR_TCIF3

| #define DMA_LISR_TCIF3 (1 << 27) |

Definition at line 301 of file dma_common_f24.h.

◆ DMA_LISR_TEIF0

| #define DMA_LISR_TEIF0 (1 << 3) |

Definition at line 281 of file dma_common_f24.h.

◆ DMA_LISR_TEIF1

| #define DMA_LISR_TEIF1 (1 << 9) |

Definition at line 287 of file dma_common_f24.h.

◆ DMA_LISR_TEIF2

| #define DMA_LISR_TEIF2 (1 << 19) |

Definition at line 293 of file dma_common_f24.h.

◆ DMA_LISR_TEIF3

| #define DMA_LISR_TEIF3 (1 << 25) |

Definition at line 299 of file dma_common_f24.h.

◆ DMA_SCR

| #define DMA_SCR | ( | port, | |

| n | |||

| ) | MMIO32(DMA_STREAM((port), (n)) + 0x00) |

Definition at line 109 of file dma_common_f24.h.

◆ DMA_SFCR

| #define DMA_SFCR | ( | port, | |

| n | |||

| ) | MMIO32(DMA_STREAM((port), (n)) + 0x14) |

Definition at line 227 of file dma_common_f24.h.

◆ DMA_SM0AR

| #define DMA_SM0AR | ( | port, | |

| n | |||

| ) |

Definition at line 179 of file dma_common_f24.h.

◆ DMA_SM1AR

| #define DMA_SM1AR | ( | port, | |

| n | |||

| ) |

Definition at line 203 of file dma_common_f24.h.

◆ DMA_SNDTR

| #define DMA_SNDTR | ( | port, | |

| n | |||

| ) | MMIO32(DMA_STREAM((port), (n)) + 0x04) |

Definition at line 132 of file dma_common_f24.h.

◆ DMA_SPAR

| #define DMA_SPAR | ( | port, | |

| n | |||

| ) |

Definition at line 155 of file dma_common_f24.h.

◆ DMA_STREAM

| #define DMA_STREAM | ( | port, | |

| n | |||

| ) | ((port) + 0x10 + (24 * (n))) |

Definition at line 62 of file dma_common_f24.h.

◆ DMA_SxCR_CHSEL

| #define DMA_SxCR_CHSEL | ( | n | ) | ((n) << DMA_SxCR_CHSEL_SHIFT) |

Definition at line 504 of file dma_common_f24.h.

◆ DMA_SxCR_CHSEL_MASK

| #define DMA_SxCR_CHSEL_MASK (7 << 25) |

Definition at line 503 of file dma_common_f24.h.

◆ DMA_SxCR_CHSEL_SHIFT

| #define DMA_SxCR_CHSEL_SHIFT 25 |

Definition at line 502 of file dma_common_f24.h.

◆ DMA_SxCR_CIRC

| #define DMA_SxCR_CIRC (1 << 8) |

Definition at line 409 of file dma_common_f24.h.

◆ DMA_SxCR_CT

| #define DMA_SxCR_CT (1 << 19) |

Definition at line 458 of file dma_common_f24.h.

◆ DMA_SxCR_DBM

| #define DMA_SxCR_DBM (1 << 18) |

Definition at line 456 of file dma_common_f24.h.

◆ DMA_SxCR_DIR_MASK

| #define DMA_SxCR_DIR_MASK (3 << 6) |

Definition at line 406 of file dma_common_f24.h.

◆ DMA_SxCR_DIR_SHIFT

| #define DMA_SxCR_DIR_SHIFT 6 |

Definition at line 405 of file dma_common_f24.h.

◆ DMA_SxCR_DMEIE

| #define DMA_SxCR_DMEIE (1 << 1) |

Definition at line 386 of file dma_common_f24.h.

◆ DMA_SxCR_EN

| #define DMA_SxCR_EN (1 << 0) |

Definition at line 384 of file dma_common_f24.h.

◆ DMA_SxCR_HTIE

| #define DMA_SxCR_HTIE (1 << 3) |

Definition at line 390 of file dma_common_f24.h.

◆ DMA_SxCR_MBURST_MASK

| #define DMA_SxCR_MBURST_MASK (3 << 23) |

Definition at line 486 of file dma_common_f24.h.

◆ DMA_SxCR_MBURST_SHIFT

| #define DMA_SxCR_MBURST_SHIFT 23 |

Definition at line 485 of file dma_common_f24.h.

◆ DMA_SxCR_MINC

| #define DMA_SxCR_MINC (1 << 10) |

Definition at line 413 of file dma_common_f24.h.

◆ DMA_SxCR_MSIZE_MASK

| #define DMA_SxCR_MSIZE_MASK (3 << 13) |

Definition at line 437 of file dma_common_f24.h.

◆ DMA_SxCR_MSIZE_SHIFT

| #define DMA_SxCR_MSIZE_SHIFT 13 |

Definition at line 436 of file dma_common_f24.h.

◆ DMA_SxCR_PBURST_MASK

| #define DMA_SxCR_PBURST_MASK (3 << 21) |

Definition at line 473 of file dma_common_f24.h.

◆ DMA_SxCR_PBURST_SHIFT

| #define DMA_SxCR_PBURST_SHIFT 21 |

Definition at line 472 of file dma_common_f24.h.

◆ DMA_SxCR_PFCTRL

| #define DMA_SxCR_PFCTRL (1 << 5) |

Definition at line 394 of file dma_common_f24.h.

◆ DMA_SxCR_PINC

| #define DMA_SxCR_PINC (1 << 9) |

Definition at line 411 of file dma_common_f24.h.

◆ DMA_SxCR_PINCOS

| #define DMA_SxCR_PINCOS (1 << 15) |

Definition at line 440 of file dma_common_f24.h.

◆ DMA_SxCR_PL_MASK

| #define DMA_SxCR_PL_MASK (3 << 16) |

Definition at line 453 of file dma_common_f24.h.

◆ DMA_SxCR_PL_SHIFT

| #define DMA_SxCR_PL_SHIFT 16 |

Definition at line 452 of file dma_common_f24.h.

◆ DMA_SxCR_PSIZE_MASK

| #define DMA_SxCR_PSIZE_MASK (3 << 11) |

Definition at line 425 of file dma_common_f24.h.

◆ DMA_SxCR_PSIZE_SHIFT

| #define DMA_SxCR_PSIZE_SHIFT 11 |

Definition at line 424 of file dma_common_f24.h.

◆ DMA_SxCR_TCIE

| #define DMA_SxCR_TCIE (1 << 4) |

Definition at line 392 of file dma_common_f24.h.

◆ DMA_SxCR_TEIE

| #define DMA_SxCR_TEIE (1 << 2) |

Definition at line 388 of file dma_common_f24.h.

◆ DMA_SxFCR_DMDIS

| #define DMA_SxFCR_DMDIS (1 << 2) |

Definition at line 540 of file dma_common_f24.h.

◆ DMA_SxFCR_FEIE

| #define DMA_SxFCR_FEIE (1 << 7) |

Definition at line 560 of file dma_common_f24.h.

◆ DMA_SxFCR_FS_MASK

| #define DMA_SxFCR_FS_MASK (7 << 3) |

Definition at line 555 of file dma_common_f24.h.

◆ DMA_SxFCR_FS_SHIFT

| #define DMA_SxFCR_FS_SHIFT 3 |

Definition at line 554 of file dma_common_f24.h.

◆ DMA_SxFCR_FTH_MASK

| #define DMA_SxFCR_FTH_MASK (3 << 0) |

Definition at line 537 of file dma_common_f24.h.

◆ DMA_SxFCR_FTH_SHIFT

| #define DMA_SxFCR_FTH_SHIFT 0 |

Definition at line 536 of file dma_common_f24.h.

Function Documentation

◆ dma_channel_select()

| void dma_channel_select | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | channel | ||

| ) |

DMA Stream Channel Select.

Associate an input channel to the stream. Not every channel is allocated to a hardware DMA request signal. The allocations for each stream are given in the STM32F4 Reference Manual.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] channel unsigned int8. Channel selection DMA Channel Select

Definition at line 345 of file dma_common_f24.c.

References DMA_SCR.

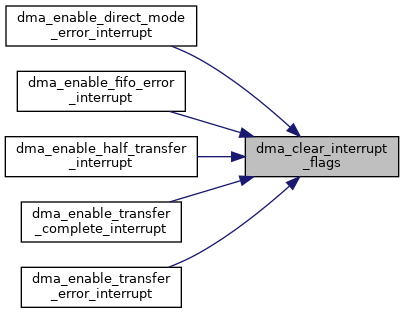

◆ dma_clear_interrupt_flags()

| void dma_clear_interrupt_flags | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | interrupts | ||

| ) |

DMA Stream Clear Interrupt Flag.

The interrupt flag for the stream is cleared. More than one interrupt for the same stream may be cleared by using the bitwise OR of the interrupt flags.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] interrupts unsigned int32. Bitwise OR of interrupt numbers: DMA Interrupt Flag Offsets within stream flag group.

Definition at line 97 of file dma_common_f24.c.

References DMA_HIFCR, DMA_ISR_OFFSET, and DMA_LIFCR.

Referenced by dma_enable_direct_mode_error_interrupt(), dma_enable_fifo_error_interrupt(), dma_enable_half_transfer_interrupt(), dma_enable_transfer_complete_interrupt(), and dma_enable_transfer_error_interrupt().

◆ dma_disable_direct_mode_error_interrupt()

| void dma_disable_direct_mode_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Direct Mode Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 593 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_double_buffer_mode()

| void dma_disable_double_buffer_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Double Buffer Mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 460 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_fifo_error_interrupt()

| void dma_disable_fifo_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Disable Interrupt on FIFO Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 618 of file dma_common_f24.c.

References DMA_SFCR.

◆ dma_disable_half_transfer_interrupt()

| void dma_disable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 543 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_memory_increment_mode()

| void dma_disable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Disable Memory Increment after Transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 253 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_peripheral_increment_mode()

| void dma_disable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Disable Peripheral Increment after Transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 286 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_stream()

| void dma_disable_stream | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable.

- Note

- The DMA stream registers retain their values when the stream is disabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 707 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_transfer_complete_interrupt()

| void dma_disable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 568 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_disable_transfer_error_interrupt()

| void dma_disable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Disable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 518 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_enable_circular_mode()

| void dma_enable_circular_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Memory Circular Mode.

After the number of bytes/words to be transferred has been completed, the original transfer block size, memory and peripheral base addresses are reloaded and the process repeats.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Note

- This cannot be used with memory to memory mode. It is disabled automatically if the peripheral is selected as the flow controller. It is enabled automatically if double buffered mode is selected.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 326 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CIRC.

◆ dma_enable_direct_mode()

| void dma_enable_direct_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable Direct Mode.

Direct mode is the default. Data is transferred as soon as a DMA request is received. The FIFO is not used. This must not be set when memory to memory mode is selected.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 650 of file dma_common_f24.c.

References DMA_SFCR.

◆ dma_enable_direct_mode_error_interrupt()

| void dma_enable_direct_mode_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Direct Mode Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 580 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_DMEIF, DMA_SCR, and DMA_SxCR_DMEIE.

◆ dma_enable_double_buffer_mode()

| void dma_enable_double_buffer_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Double Buffer Mode.

Double buffer mode is used for memory to/from peripheral transfers only, and in circular mode which is automatically enabled. Two memory buffers must be established with pointers stored in the memory pointer registers.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Note

- This cannot be used with memory to memory mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 448 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_DBM.

◆ dma_enable_fifo_error_interrupt()

| void dma_enable_fifo_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable Interrupt on FIFO Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 605 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_FEIF, DMA_SFCR, and DMA_SxFCR_FEIE.

◆ dma_enable_fifo_mode()

| void dma_enable_fifo_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Enable FIFO Mode.

Data is transferred via a FIFO.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 664 of file dma_common_f24.c.

References DMA_SFCR, and DMA_SxFCR_DMDIS.

◆ dma_enable_fixed_peripheral_increment_mode()

| void dma_enable_fixed_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Enable Fixed Sized Peripheral Increment after Transfer.

Following each transfer the current peripheral address is incremented by 4 regardless of the data size. The value held by the base peripheral address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 304 of file dma_common_f24.c.

References DMA_SCR, DMA_SxCR_PINC, and DMA_SxCR_PINCOS.

◆ dma_enable_half_transfer_interrupt()

| void dma_enable_half_transfer_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Half Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 530 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_HTIF, DMA_SCR, and DMA_SxCR_HTIE.

◆ dma_enable_memory_increment_mode()

| void dma_enable_memory_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Memory Increment after Transfer.

Following each transfer the current memory address is incremented by 1, 2 or 4 depending on the data size set in dma_set_memory_size. The value held by the base memory address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 239 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_MINC.

◆ dma_enable_peripheral_increment_mode()

| void dma_enable_peripheral_increment_mode | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Channel Enable Variable Sized Peripheral Increment after Transfer.

Following each transfer the current peripheral address is incremented by 1, 2 or 4 depending on the data size set in dma_set_peripheral_size. The value held by the base peripheral address register is unchanged.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 271 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PINC.

◆ dma_enable_stream()

| void dma_enable_stream | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 693 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_EN.

◆ dma_enable_transfer_complete_interrupt()

| void dma_enable_transfer_complete_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Complete.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 555 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_SCR, DMA_SxCR_TCIE, and DMA_TCIF.

◆ dma_enable_transfer_error_interrupt()

| void dma_enable_transfer_error_interrupt | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Enable Interrupt on Transfer Error.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 505 of file dma_common_f24.c.

References dma_clear_interrupt_flags(), DMA_SCR, DMA_SxCR_TEIE, and DMA_TEIF.

◆ dma_fifo_status()

| uint32_t dma_fifo_status | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Get FIFO Status.

Status of FIFO (empty. full or partial filled states) is returned. This has no meaning if direct mode is enabled (as the FIFO is not used).

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- uint32_t FIFO Status FIFO Status

Definition at line 634 of file dma_common_f24.c.

References DMA_SFCR, and DMA_SxFCR_FS_MASK.

◆ dma_get_interrupt_flag()

| bool dma_get_interrupt_flag | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | interrupt | ||

| ) |

DMA Stream Read Interrupt Flag.

The interrupt flag for the stream is returned.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] interrupt unsigned int32. Interrupt number: DMA Interrupt Flag Offsets within stream flag group.

- Returns

- bool interrupt flag is set.

Definition at line 123 of file dma_common_f24.c.

References DMA_HISR, DMA_ISR_OFFSET, and DMA_LISR.

◆ dma_get_number_of_data()

| uint16_t dma_get_number_of_data | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Get the Transfer Block Size.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- unsigned int16. Number of remaining data words to transfer (65535 maximum).

Definition at line 788 of file dma_common_f24.c.

References DMA_SNDTR.

◆ dma_get_target()

| uint8_t dma_get_target | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Read Current Memory Target.

In double buffer mode, return the current memory target (M0 or M1). It is possible to update the memory pointer in the register that is not currently in use. An attempt to change the register currently in use will cause the stream to be disabled and the transfer error flag to be set.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

- Returns

- unsigned int8. Memory buffer in use: 0 or 1

Definition at line 424 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CT.

◆ dma_set_dma_flow_control()

| void dma_set_dma_flow_control | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Set DMA Flow Control.

Set the DMA controller to control DMA flow. This is the default.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 493 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_fifo_threshold()

| void dma_set_fifo_threshold | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | threshold | ||

| ) |

DMA Set FIFO Threshold.

This is the filled level at which data is transferred out of the FIFO to the destination.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] threshold unsigned int8. Threshold setting FIFO Threshold selection

Definition at line 680 of file dma_common_f24.c.

References DMA_SFCR.

◆ dma_set_initial_target()

| void dma_set_initial_target | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint8_t | memory | ||

| ) |

DMA Stream Set Initial Target Memory.

In double buffered mode, set the target memory (M0 or M1) to be used for the first transfer.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] memory unsigned int8. Initial memory pointer to use: 0 or 1

Definition at line 401 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_CT.

◆ dma_set_memory_address()

| void dma_set_memory_address | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Base Memory Address 0.

Set the address pointer to the memory location for DMA transfers. The DMA stream must normally be disabled before setting this address, however it is possible to change this in double buffer mode when the current target is memory area 1 (see dma_get_target).

This is the default base memory address used in direct mode.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Memory Initial Address.

Definition at line 748 of file dma_common_f24.c.

References DMA_SCR, DMA_SM0AR, DMA_SxCR_CT, DMA_SxCR_DBM, and DMA_SxCR_EN.

◆ dma_set_memory_address_1()

| void dma_set_memory_address_1 | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Base Memory Address 1.

Set the address pointer to the memory location for DMA transfers. The DMA stream must normally be disabled before setting this address, however it is possible to change this in double buffer mode when the current target is memory area 0 (see dma_get_target).

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Memory Initial Address.

Definition at line 770 of file dma_common_f24.c.

References DMA_SCR, DMA_SM1AR, DMA_SxCR_CT, DMA_SxCR_DBM, and DMA_SxCR_EN.

◆ dma_set_memory_burst()

| void dma_set_memory_burst | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | burst | ||

| ) |

DMA Stream Set Memory Burst Configuration.

Set the memory burst type to none, 4 8 or 16 word length. This is forced to none if direct mode is used.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] burst unsigned int8. Memory Burst selection DMA Memory Burst Length

Definition at line 363 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_memory_size()

| void dma_set_memory_size | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | mem_size | ||

| ) |

DMA Stream Set Memory Word Width.

Set the memory word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] mem_size unsigned int32. Memory word width DMA Stream Memory Word Width.

Definition at line 198 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_MSIZE_MASK.

◆ dma_set_number_of_data()

| void dma_set_number_of_data | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint16_t | number | ||

| ) |

DMA Stream Set the Transfer Block Size.

- Note

- The DMA stream must be disabled before setting this count value. The count is not changed if the stream is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] number unsigned int16. Number of data words to transfer (65535 maximum).

Definition at line 805 of file dma_common_f24.c.

References DMA_SNDTR.

◆ dma_set_peripheral_address()

| void dma_set_peripheral_address | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | address | ||

| ) |

DMA Stream Set the Peripheral Address.

Set the address of the peripheral register to or from which data is to be transferred. Refer to the documentation for the specific peripheral.

- Note

- The DMA stream must be disabled before setting this address. This function has no effect if the stream is enabled.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] address unsigned int32. Peripheral Address.

Definition at line 726 of file dma_common_f24.c.

References DMA_SCR, DMA_SPAR, and DMA_SxCR_EN.

◆ dma_set_peripheral_burst()

| void dma_set_peripheral_burst | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | burst | ||

| ) |

DMA Stream Set Peripheral Burst Configuration.

Set the memory burst type to none, 4 8 or 16 word length. This is forced to none if direct mode is used.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] burst unsigned int8. Peripheral Burst selection DMA Peripheral Burst Length

Definition at line 382 of file dma_common_f24.c.

References DMA_SCR.

◆ dma_set_peripheral_flow_control()

| void dma_set_peripheral_flow_control | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Set Peripheral Flow Control.

Set the peripheral to control DMA flow. Useful when the number of transfers is unknown. This is forced off when memory to memory mode is selected.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 477 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PFCTRL.

◆ dma_set_peripheral_size()

| void dma_set_peripheral_size | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | peripheral_size | ||

| ) |

DMA Stream Set Peripheral Word Width.

Set the peripheral word width 8 bits, 16 bits, or 32 bits. Refer to datasheet for alignment information if the source and destination widths do not match, or if the peripheral does not support byte or half-word writes.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] peripheral_size unsigned int32. Peripheral word width DMA Stream Peripheral Word Width.

Definition at line 219 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PSIZE_MASK.

◆ dma_set_priority()

| void dma_set_priority | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | prio | ||

| ) |

DMA Stream Set Priority.

Stream Priority has four levels: low to very high. This has precedence over the hardware priority. In the event of equal software priority the lower numbered stream has priority.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] prio unsigned int32. Priority level DMA Stream Priority Levels.

Definition at line 179 of file dma_common_f24.c.

References DMA_SCR, and DMA_SxCR_PL_MASK.

◆ dma_set_transfer_mode()

| void dma_set_transfer_mode | ( | uint32_t | dma, |

| uint8_t | stream, | ||

| uint32_t | direction | ||

| ) |

DMA Stream Enable Transfer Direction.

Set peripheral to memory, memory to peripheral or memory to memory. If memory to memory mode is selected, circular mode and double buffer modes are disabled. Ensure that these modes are not enabled at a later time.

Ensure that the stream is disabled otherwise the setting will not be changed.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number [in] direction unsigned int32. Data transfer direction DMA Stream Data transfer direction

Definition at line 151 of file dma_common_f24.c.

References DMA_SCR, DMA_SxCR_CIRC, DMA_SxCR_DBM, and DMA_SxCR_DIR_MEM_TO_MEM.

◆ dma_stream_reset()

| void dma_stream_reset | ( | uint32_t | dma, |

| uint8_t | stream | ||

| ) |

DMA Stream Reset.

The specified stream is disabled and configuration registers are cleared.

- Parameters

-

[in] dma unsigned int32. DMA controller base address: DMA1 or DMA2 [in] stream unsigned int8. Stream number: DMA Stream Number

Definition at line 62 of file dma_common_f24.c.

References DMA_HIFCR, DMA_ISR_MASK, DMA_LIFCR, DMA_SCR, DMA_SFCR, DMA_SM0AR, DMA_SM1AR, DMA_SNDTR, and DMA_SPAR.