dcmi_common_f47.h File Reference

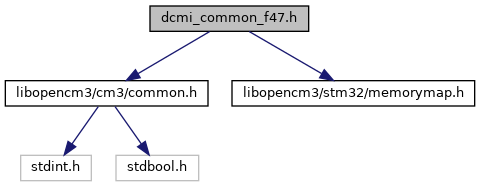

Include dependency graph for dcmi_common_f47.h:

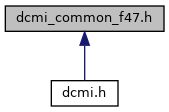

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | DCMI_CR MMIO32(DCMI_BASE + 0x0U) |

| DCMI control register 1. More... | |

| #define | DCMI_CR_EN (1 << 14) |

| #define | DCMI_CR_EDM1 (1 << 11) |

| #define | DCMI_CR_EDM0 (1 << 10) |

| #define | DCMI_CR_FCRC1 (1 << 9) |

| #define | DCMI_CR_FCRC0 (1 << 8) |

| #define | DCMI_CR_VSPOL (1 << 7) |

| #define | DCMI_CR_HSPOL (1 << 6) |

| #define | DCMI_CR_PCKPOL (1 << 5) |

| #define | DCMI_CR_ESS (1 << 4) |

| #define | DCMI_CR_JPEG (1 << 3) |

| #define | DCMI_CR_CROP (1 << 2) |

| #define | DCMI_CR_CM (1 << 1) |

| #define | DCMI_CR_CAPTURE (1 << 0) |

| #define | DCMI_SR MMIO32(DCMI_BASE + 0x04U) |

| DCMI status register. More... | |

| #define | DCMI_SR_FNE (1 << 2) |

| #define | DCMI_SR_VSYNCK (1 << 1) |

| #define | DCMI_SR_HSYNCK (1 << 0) |

| #define | DCMI_RIS MMIO32(DCMI_BASE + 0x08U) |

| DCMI raw interrupt status register. More... | |

| #define | DCMI_RIS_LINE (1 << 4) |

| #define | DCMI_RIS_VSYNC (1 << 3) |

| #define | DCMI_RIS_ERR (1 << 2) |

| #define | DCMI_RIS_OVR (1 << 1) |

| #define | DCMI_RIS_FRAME (1 << 0) |

| #define | DCMI_IER MMIO32(DCMI_BASE + 0x0CU) |

| DCMI interrupt enable register. More... | |

| #define | DCMI_IER_LINE (1 << 4) |

| #define | DCMI_IER_VSYNC (1 << 3) |

| #define | DCMI_IER_ERR (1 << 2) |

| #define | DCMI_IER_OVR (1 << 1) |

| #define | DCMI_IER_FRAME (1 << 0) |

| #define | DCMI_MIS MMIO32(DCMI_BASE + 0x10U) |

| DCMI masked interrupt status register. More... | |

| #define | DCMI_MIS_LINE (1 << 4) |

| #define | DCMI_MIS_VSYNC (1 << 3) |

| #define | DCMI_MIS_ERR (1 << 2) |

| #define | DCMI_MIS_OVR (1 << 1) |

| #define | DCMI_MIS_FRAME (1 << 0) |

| #define | DCMI_ICR MMIO32(DCMI_BASE + 0x14U) |

| DCMI interrupt clear register. More... | |

| #define | DCMI_ICR_LINE (1 << 4) |

| #define | DCMI_ICR_VSYNC (1 << 3) |

| #define | DCMI_ICR_ERR (1 << 2) |

| #define | DCMI_ICR_OVR (1 << 1) |

| #define | DCMI_ICR_FRAME (1 << 0) |

| #define | DCMI_ESCR MMIO32(DCMI_BASE + 0x18U) |

| DCMI embedded synchronization code register. More... | |

| #define | DCMI_ESCR_FEC_SHIFT 24 |

| #define | DCMI_ESCR_FEC_MASK 0xff |

| #define | DCMI_ESCR_LEC_SHIFT 16 |

| #define | DCMI_ESCR_LEC_MASK 0xff |

| #define | DCMI_ESCR_LSC_SHIFT 8 |

| #define | DCMI_ESCR_LSC_MASK 0xff |

| #define | DCMI_ESCR_FSC_SHIFT 0 |

| #define | DCMI_ESCR_FSC_MASK 0xff |

| #define | DCMI_ESUR MMIO32(DCMI_BASE + 0x1CU) |

| DCMI embedded synchronization unmask register. More... | |

| #define | DCMI_ESUR_FEU_SHIFT 24 |

| #define | DCMI_ESUR_FEU_MASK 0xff |

| #define | DCMI_ESUR_LEU_SHIFT 16 |

| #define | DCMI_ESUR_LEU_MASK 0xff |

| #define | DCMI_ESUR_LSU_SHIFT 8 |

| #define | DCMI_ESUR_LSU_MASK 0xff |

| #define | DCMI_ESUR_FSU_SHIFT 0 |

| #define | DCMI_ESUR_FSU_MASK 0xff |

| #define | DCMI_CWSTRT MMIO32(DCMI_BASE + 0x20U) |

| DCMI crop window start. More... | |

| #define | DCMI_CWSTRT_VST_SHIFT 16 |

| #define | DCMI_CWSTRT_VST_MASK 0x1fff |

| #define | DCMI_CWSTRT_HOFFCNT_SHIFT 0 |

| #define | DCMI_CWSTRT_HOFFCNT_MASK 0x3fff |

| #define | DCMI_CWSIZE MMIO32(DCMI_BASE + 0x24U) |

| DCMI crop window size. More... | |

| #define | DCMI_CWSIZE_VLINE_SHIFT 16 |

| #define | DCMI_CWSIZE_VLINE_MASK 0x3fff |

| #define | DCMI_CWSIZE_CAPCNT_SHIFT 0 |

| #define | DCMI_CWSIZE_CAPCNT_MASK 0x3fff |

| #define | DCMI_DR MMIO32(DCMI_BASE + 0x28U) |

| DCMI data register. More... | |