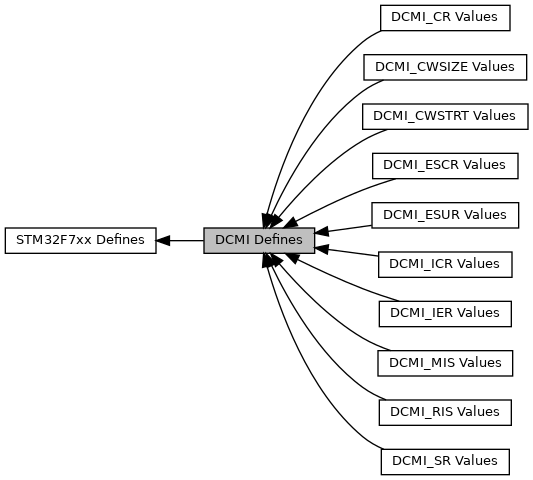

Defined Constants and Macros for the STM32F7xx DCMI Peripheral. More...

Modules | |

| DCMI_CR Values | |

| DCMI_SR Values | |

| DCMI_RIS Values | |

| DCMI_IER Values | |

| DCMI_MIS Values | |

| DCMI_ICR Values | |

| DCMI_ESCR Values | |

| DCMI_ESUR Values | |

| DCMI_CWSTRT Values | |

| DCMI_CWSIZE Values | |

Macros | |

| #define | DCMI_CR MMIO32(DCMI_BASE + 0x0U) |

| DCMI control register 1. More... | |

| #define | DCMI_SR MMIO32(DCMI_BASE + 0x04U) |

| DCMI status register. More... | |

| #define | DCMI_RIS MMIO32(DCMI_BASE + 0x08U) |

| DCMI raw interrupt status register. More... | |

| #define | DCMI_IER MMIO32(DCMI_BASE + 0x0CU) |

| DCMI interrupt enable register. More... | |

| #define | DCMI_MIS MMIO32(DCMI_BASE + 0x10U) |

| DCMI masked interrupt status register. More... | |

| #define | DCMI_ICR MMIO32(DCMI_BASE + 0x14U) |

| DCMI interrupt clear register. More... | |

| #define | DCMI_ESCR MMIO32(DCMI_BASE + 0x18U) |

| DCMI embedded synchronization code register. More... | |

| #define | DCMI_ESUR MMIO32(DCMI_BASE + 0x1CU) |

| DCMI embedded synchronization unmask register. More... | |

| #define | DCMI_CWSTRT MMIO32(DCMI_BASE + 0x20U) |

| DCMI crop window start. More... | |

| #define | DCMI_CWSIZE MMIO32(DCMI_BASE + 0x24U) |

| DCMI crop window size. More... | |

| #define | DCMI_DR MMIO32(DCMI_BASE + 0x28U) |

| DCMI data register. More... | |

Detailed Description

Defined Constants and Macros for the STM32F7xx DCMI Peripheral.

- Version

- 1.0.0

- Date

- 2020-05-15

LGPL License Terms libopencm3 License

- Version

- 1.0.0

- Date

- 15 May 2020

This library supports the Digital camera interface (DCMI) in the STM32F4xx and STM32F7xx series of ARM Cortex Microcontrollers by ST Microelectronics.

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ DCMI_CR

DCMI control register 1.

Definition at line 47 of file dcmi_common_f47.h.

◆ DCMI_CWSIZE

DCMI crop window size.

Definition at line 209 of file dcmi_common_f47.h.

◆ DCMI_CWSTRT

DCMI crop window start.

Definition at line 195 of file dcmi_common_f47.h.

◆ DCMI_DR

DCMI data register.

The digital camera Interface packages all the received data in 32-bit format before requesting a DMA transfer. A 4-word deep FIFO is available to leave enough time for DMA transfers and avoid DMA overrun conditions.

Definition at line 227 of file dcmi_common_f47.h.

◆ DCMI_ESCR

DCMI embedded synchronization code register.

Definition at line 158 of file dcmi_common_f47.h.

◆ DCMI_ESUR

DCMI embedded synchronization unmask register.

Definition at line 177 of file dcmi_common_f47.h.

◆ DCMI_ICR

DCMI interrupt clear register.

The DCMI_ICR register is write-only. Writing a ‘1’ into a bit of this register clears the corresponding bit in the DCMI_RIS and DCMI_MIS registers. Writing a ‘0’ has no effect.

Definition at line 143 of file dcmi_common_f47.h.

◆ DCMI_IER

DCMI interrupt enable register.

The DCMI_IER register is used to enable interrupts. When one of the DCMI_IER bits is set, the corresponding interrupt is enabled. This register is accessible in both read and write.

Definition at line 105 of file dcmi_common_f47.h.

◆ DCMI_MIS

DCMI masked interrupt status register.

This DCMI_MIS register is a read-only register. When read, it returns the current masked status value (depending on the value in DCMI_IER) of the corresponding interrupt. A bit in this register is set if the corresponding enable bit in DCMI_IER is set and the corresponding bit in DCMI_RIS is set.

Definition at line 125 of file dcmi_common_f47.h.

◆ DCMI_RIS

DCMI raw interrupt status register.

DCMI_RIS gives the raw interrupt status and is accessible in read only. When read, this register returns the status of the corresponding interrupt before masking with the DCMI_IER register value.

Definition at line 87 of file dcmi_common_f47.h.

◆ DCMI_SR

DCMI status register.

Definition at line 70 of file dcmi_common_f47.h.