ccm.h File Reference

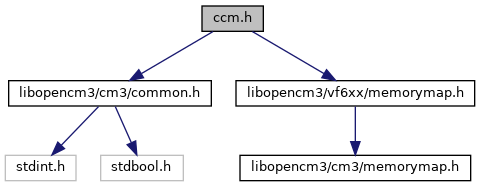

Include dependency graph for ccm.h:

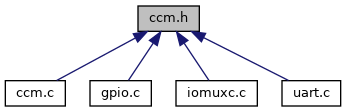

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | ccm_clock_gate_enable (enum ccm_clock_gate gr) |

| Enable clock of given device. More... | |

| void | ccm_clock_gate_disable (enum ccm_clock_gate gr) |

| Disable clock of given device. More... | |

| void | ccm_calculate_clocks (void) |

| Calculate clocks. More... | |

Variables | |

| uint32_t | ccm_core_clk |

| uint32_t | ccm_platform_bus_clk |

| uint32_t | ccm_ipg_bus_clk |

Macro Definition Documentation

◆ CCM_CACRR

◆ CCM_CACRR_ARM_CLK_DIV_MASK

◆ CCM_CACRR_ARM_CLK_DIV_SHIFT

◆ CCM_CACRR_BUS_CLK_DIV_MASK

◆ CCM_CACRR_BUS_CLK_DIV_SHIFT

◆ CCM_CACRR_FLEX_CLK_DIV_MASK

◆ CCM_CACRR_FLEX_CLK_DIV_SHIFT

◆ CCM_CACRR_IPG_CLK_DIV_MASK

◆ CCM_CACRR_IPG_CLK_DIV_SHIFT

◆ CCM_CACRR_PLL1_PFD_CLK_DIV_MASK

◆ CCM_CACRR_PLL1_PFD_CLK_DIV_SHIFT

◆ CCM_CACRR_PLL3_CLK_DIV

◆ CCM_CACRR_PLL4_CLK_DIV_MASK

◆ CCM_CACRR_PLL4_CLK_DIV_SHIFT

◆ CCM_CACRR_PLL6_CLK_DIV

◆ CCM_CCGR

◆ CCM_CCOSR

◆ CCM_CCOWR

◆ CCM_CCPGR

◆ CCM_CCR

◆ CCM_CCR_FIRC_EN

◆ CCM_CCR_FXOSC_EN

◆ CCM_CCR_OSCNT_MASK

◆ CCM_CCSR

◆ CCM_CCSR_DAP_EN

◆ CCM_CCSR_DDRC_CLK_SEL

◆ CCM_CCSR_FAST_CLK_SEL

◆ CCM_CCSR_PLL1_PFD_CLK_SEL_MASK

◆ CCM_CCSR_PLL1_PFD_CLK_SEL_SHIFT

◆ CCM_CCSR_PLL1_PFDN1_EN

◆ CCM_CCSR_PLL1_PFDN2_EN

◆ CCM_CCSR_PLL1_PFDN3_EN

◆ CCM_CCSR_PLL1_PFDN4_EN

◆ CCM_CCSR_PLL2_PFD_CLK_SEL_MASK

◆ CCM_CCSR_PLL2_PFD_CLK_SEL_SHIFT

◆ CCM_CCSR_PLL2_PFDN1_EN

◆ CCM_CCSR_PLL2_PFDN2_EN

◆ CCM_CCSR_PLL2_PFDN3_EN

◆ CCM_CCSR_PLL2_PFDN4_EN

◆ CCM_CCSR_PLL3_PFDN1_EN

◆ CCM_CCSR_PLL3_PFDN2_EN

◆ CCM_CCSR_PLL3_PFDN3_EN

◆ CCM_CCSR_PLL3_PFDN4_EN

◆ CCM_CCSR_PLL_PFD_CLK_SEL_MAIN

◆ CCM_CCSR_PLL_PFD_CLK_SEL_PFD1

◆ CCM_CCSR_PLL_PFD_CLK_SEL_PFD2

◆ CCM_CCSR_PLL_PFD_CLK_SEL_PFD3

◆ CCM_CCSR_PLL_PFD_CLK_SEL_PFD4

◆ CCM_CCSR_SLOW_CLK_SEL

◆ CCM_CCSR_SYS_CLK_SEL_FAST

◆ CCM_CCSR_SYS_CLK_SEL_MASK

◆ CCM_CCSR_SYS_CLK_SEL_PLL1_PFD

◆ CCM_CCSR_SYS_CLK_SEL_PLL2

◆ CCM_CCSR_SYS_CLK_SEL_PLL2_PFD

◆ CCM_CCSR_SYS_CLK_SEL_PLL3

◆ CCM_CCSR_SYS_CLK_SEL_SHIFT

◆ CCM_CCSR_SYS_CLK_SEL_SLOW

◆ CCM_CGPR

◆ CCM_CIMR

◆ CCM_CISR

◆ CCM_CLPCR

◆ CCM_CMEOR

◆ CCM_CPPDSR

◆ CCM_CSCDR1

◆ CCM_CSCDR2

◆ CCM_CSCDR3

◆ CCM_CSCMR1

◆ CCM_CSCMR2

◆ CCM_CSR

◆ CCM_CSR_FXOSC_RDY

◆ CCM_CTOR

Enumeration Type Documentation

◆ ccm_clock_gate

| enum ccm_clock_gate |