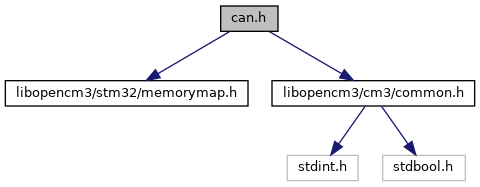

Include dependency graph for can.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | CAN1 BX_CAN1_BASE |

| #define | CAN2 BX_CAN2_BASE |

| #define | CAN_MCR(can_base) MMIO32((can_base) + 0x000) |

| #define | CAN_MSR(can_base) MMIO32((can_base) + 0x004) |

| #define | CAN_TSR(can_base) MMIO32((can_base) + 0x008) |

| #define | CAN_RF0R(can_base) MMIO32((can_base) + 0x00C) |

| #define | CAN_RF1R(can_base) MMIO32((can_base) + 0x010) |

| #define | CAN_IER(can_base) MMIO32((can_base) + 0x014) |

| #define | CAN_ESR(can_base) MMIO32((can_base) + 0x018) |

| #define | CAN_BTR(can_base) MMIO32((can_base) + 0x01C) |

| #define | CAN_MBOX0 0x180 |

| #define | CAN_MBOX1 0x190 |

| #define | CAN_MBOX2 0x1A0 |

| #define | CAN_FIFO0 0x1B0 |

| #define | CAN_FIFO1 0x1C0 |

| #define | CAN_TIxR(can_base, mbox) MMIO32((can_base) + (mbox) + 0x0) |

| #define | CAN_TI0R(can_base) CAN_TIxR(can_base, CAN_MBOX0) |

| #define | CAN_TI1R(can_base) CAN_TIxR(can_base, CAN_MBOX1) |

| #define | CAN_TI2R(can_base) CAN_TIxR(can_base, CAN_MBOX2) |

| #define | CAN_TDTxR(can_base, mbox) MMIO32((can_base) + (mbox) + 0x4) |

| #define | CAN_TDT0R(can_base) CAN_TDTxR((can_base), CAN_MBOX0) |

| #define | CAN_TDT1R(can_base) CAN_TDTxR((can_base), CAN_MBOX1) |

| #define | CAN_TDT2R(can_base) CAN_TDTxR((can_base), CAN_MBOX2) |

| #define | CAN_TDLxR(can_base, mbox) MMIO32((can_base) + (mbox) + 0x8) |

| #define | CAN_TDL0R(can_base) CAN_TDLxR((can_base), CAN_MBOX0) |

| #define | CAN_TDL1R(can_base) CAN_TDLxR((can_base), CAN_MBOX1) |

| #define | CAN_TDL2R(can_base) CAN_TDLxR((can_base), CAN_MBOX2) |

| #define | CAN_TDHxR(can_base, mbox) MMIO32((can_base) + (mbox) + 0xC) |

| #define | CAN_TDH0R(can_base) CAN_TDHxR((can_base), CAN_MBOX0) |

| #define | CAN_TDH1R(can_base) CAN_TDHxR((can_base), CAN_MBOX1) |

| #define | CAN_TDH2R(can_base) CAN_TDHxR((can_base), CAN_MBOX2) |

| #define | CAN_RIxR(can_base, fifo) MMIO32((can_base) + (fifo) + 0x0) |

| #define | CAN_RI0R(can_base) CAN_RIxR((can_base), CAN_FIFO0) |

| #define | CAN_RI1R(can_base) CAN_RIxR((can_base), CAN_FIFO1) |

| #define | CAN_RDTxR(can_base, fifo) MMIO32((can_base) + (fifo) + 0x4) |

| #define | CAN_RDT0R(can_base) CAN_RDTxR((can_base), CAN_FIFO0) |

| #define | CAN_RDT1R(can_base) CAN_RDTxR((can_base), CAN_FIFO1) |

| #define | CAN_RDLxR(can_base, fifo) MMIO32((can_base) + (fifo) + 0x8) |

| #define | CAN_RDL0R(can_base) CAN_RDLxR((can_base), CAN_FIFO0) |

| #define | CAN_RDL1R(can_base) CAN_RDLxR((can_base), CAN_FIFO1) |

| #define | CAN_RDHxR(can_base, fifo) MMIO32((can_base) + (fifo) + 0xC) |

| #define | CAN_RDH0R(can_base) CAN_RDHxR((can_base), CAN_FIFO0) |

| #define | CAN_RDH1R(can_base) CAN_RDHxR((can_base), CAN_FIFO1) |

| #define | CAN_FMR(can_base) MMIO32((can_base) + 0x200) |

| #define | CAN_FM1R(can_base) MMIO32((can_base) + 0x204) |

| #define | CAN_FS1R(can_base) MMIO32((can_base) + 0x20C) |

| #define | CAN_FFA1R(can_base) MMIO32((can_base) + 0x214) |

| #define | CAN_FA1R(can_base) MMIO32((can_base) + 0x21C) |

| #define | CAN_FiR1(can_base, bank) |

| #define | CAN_FiR2(can_base, bank) |

| #define | CAN_MCR_DBF (1 << 16) |

| #define | CAN_MCR_RESET (1 << 15) |

| #define | CAN_MCR_TTCM (1 << 7) |

| #define | CAN_MCR_ABOM (1 << 6) |

| #define | CAN_MCR_AWUM (1 << 5) |

| #define | CAN_MCR_NART (1 << 4) |

| #define | CAN_MCR_RFLM (1 << 3) |

| #define | CAN_MCR_TXFP (1 << 2) |

| #define | CAN_MCR_SLEEP (1 << 1) |

| #define | CAN_MCR_INRQ (1 << 0) |

| #define | CAN_MSR_RX (1 << 11) |

| #define | CAN_MSR_SAMP (1 << 10) |

| #define | CAN_MSR_RXM (1 << 9) |

| #define | CAN_MSR_TXM (1 << 8) |

| #define | CAN_MSR_SLAKI (1 << 4) |

| #define | CAN_MSR_WKUI (1 << 3) |

| #define | CAN_MSR_ERRI (1 << 2) |

| #define | CAN_MSR_SLAK (1 << 1) |

| #define | CAN_MSR_INAK (1 << 0) |

| #define | CAN_TSR_LOW2 (1 << 31) |

| #define | CAN_TSR_LOW1 (1 << 30) |

| #define | CAN_TSR_LOW0 (1 << 29) |

| #define | CAN_TSR_TME2 (1 << 28) |

| #define | CAN_TSR_TME1 (1 << 27) |

| #define | CAN_TSR_TME0 (1 << 26) |

| #define | CAN_TSR_CODE_MASK (0x3 << 24) |

| #define | CAN_TSR_ABRQ2 (1 << 23) |

| #define | CAN_TSR_TERR2 (1 << 19) |

| #define | CAN_TSR_ALST2 (1 << 18) |

| #define | CAN_TSR_TXOK2 (1 << 17) |

| #define | CAN_TSR_RQCP2 (1 << 16) |

| #define | CAN_TSR_ABRQ1 (1 << 15) |

| #define | CAN_TSR_TERR1 (1 << 11) |

| #define | CAN_TSR_ALST1 (1 << 10) |

| #define | CAN_TSR_TXOK1 (1 << 9) |

| #define | CAN_TSR_RQCP1 (1 << 8) |

| #define | CAN_TSR_ABRQ0 (1 << 7) |

| #define | CAN_TSR_TERR0 (1 << 3) |

| #define | CAN_TSR_ALST0 (1 << 2) |

| #define | CAN_TSR_TXOK0 (1 << 1) |

| #define | CAN_TSR_RQCP0 (1 << 0) |

| #define | CAN_RF0R_RFOM0 (1 << 5) |

| #define | CAN_RF0R_FOVR0 (1 << 4) |

| #define | CAN_RF0R_FULL0 (1 << 3) |

| #define | CAN_RF0R_FMP0_MASK (0x3 << 0) |

| #define | CAN_RF1R_RFOM1 (1 << 5) |

| #define | CAN_RF1R_FOVR1 (1 << 4) |

| #define | CAN_RF1R_FULL1 (1 << 3) |

| #define | CAN_RF1R_FMP1_MASK (0x3 << 0) |

| #define | CAN_IER_SLKIE (1 << 17) |

| #define | CAN_IER_WKUIE (1 << 16) |

| #define | CAN_IER_ERRIE (1 << 15) |

| #define | CAN_IER_LECIE (1 << 11) |

| #define | CAN_IER_BOFIE (1 << 10) |

| #define | CAN_IER_EPVIE (1 << 9) |

| #define | CAN_IER_EWGIE (1 << 8) |

| #define | CAN_IER_FOVIE1 (1 << 6) |

| #define | CAN_IER_FFIE1 (1 << 5) |

| #define | CAN_IER_FMPIE1 (1 << 4) |

| #define | CAN_IER_FOVIE0 (1 << 3) |

| #define | CAN_IER_FFIE0 (1 << 2) |

| #define | CAN_IER_FMPIE0 (1 << 1) |

| #define | CAN_IER_TMEIE (1 << 0) |

| #define | CAN_ESR_REC_MASK (0xF << 24) |

| #define | CAN_ESR_TEC_MASK (0xF << 16) |

| #define | CAN_ESR_LEC_NO_ERROR (0x0 << 4) |

| #define | CAN_ESR_LEC_STUFF_ERROR (0x1 << 4) |

| #define | CAN_ESR_LEC_FORM_ERROR (0x2 << 4) |

| #define | CAN_ESR_LEC_ACK_ERROR (0x3 << 4) |

| #define | CAN_ESR_LEC_REC_ERROR (0x4 << 4) |

| #define | CAN_ESR_LEC_DOM_ERROR (0x5 << 4) |

| #define | CAN_ESR_LEC_CRC_ERROR (0x6 << 4) |

| #define | CAN_ESR_LEC_SOFT_ERROR (0x7 << 4) |

| #define | CAN_ESR_LEC_MASK (0x7 << 4) |

| #define | CAN_ESR_BOFF (1 << 2) |

| #define | CAN_ESR_EPVF (1 << 1) |

| #define | CAN_ESR_EWGF (1 << 0) |

| #define | CAN_BTR_SILM (1 << 31) |

| #define | CAN_BTR_LBKM (1 << 30) |

| #define | CAN_BTR_SJW_1TQ (0x0 << 24) |

| #define | CAN_BTR_SJW_2TQ (0x1 << 24) |

| #define | CAN_BTR_SJW_3TQ (0x2 << 24) |

| #define | CAN_BTR_SJW_4TQ (0x3 << 24) |

| #define | CAN_BTR_SJW_MASK (0x3 << 24) |

| #define | CAN_BTR_SJW_SHIFT 24 |

| #define | CAN_BTR_TS2_1TQ (0x0 << 20) |

| #define | CAN_BTR_TS2_2TQ (0x1 << 20) |

| #define | CAN_BTR_TS2_3TQ (0x2 << 20) |

| #define | CAN_BTR_TS2_4TQ (0x3 << 20) |

| #define | CAN_BTR_TS2_5TQ (0x4 << 20) |

| #define | CAN_BTR_TS2_6TQ (0x5 << 20) |

| #define | CAN_BTR_TS2_7TQ (0x6 << 20) |

| #define | CAN_BTR_TS2_8TQ (0x7 << 20) |

| #define | CAN_BTR_TS2_MASK (0x7 << 20) |

| #define | CAN_BTR_TS2_SHIFT 20 |

| #define | CAN_BTR_TS1_1TQ (0x0 << 16) |

| #define | CAN_BTR_TS1_2TQ (0x1 << 16) |

| #define | CAN_BTR_TS1_3TQ (0x2 << 16) |

| #define | CAN_BTR_TS1_4TQ (0x3 << 16) |

| #define | CAN_BTR_TS1_5TQ (0x4 << 16) |

| #define | CAN_BTR_TS1_6TQ (0x5 << 16) |

| #define | CAN_BTR_TS1_7TQ (0x6 << 16) |

| #define | CAN_BTR_TS1_8TQ (0x7 << 16) |

| #define | CAN_BTR_TS1_9TQ (0x8 << 16) |

| #define | CAN_BTR_TS1_10TQ (0x9 << 16) |

| #define | CAN_BTR_TS1_11TQ (0xA << 16) |

| #define | CAN_BTR_TS1_12TQ (0xB << 16) |

| #define | CAN_BTR_TS1_13TQ (0xC << 16) |

| #define | CAN_BTR_TS1_14TQ (0xD << 16) |

| #define | CAN_BTR_TS1_15TQ (0xE << 16) |

| #define | CAN_BTR_TS1_16TQ (0xF << 16) |

| #define | CAN_BTR_TS1_MASK (0xF << 16) |

| #define | CAN_BTR_TS1_SHIFT 16 |

| #define | CAN_BTR_BRP_MASK (0x3FFUL << 0) |

| #define | CAN_TIxR_STID_MASK (0x7FF << 21) |

| #define | CAN_TIxR_STID_SHIFT 21 |

| #define | CAN_TIxR_EXID_MASK (0x1FFFFFF << 3) |

| #define | CAN_TIxR_EXID_SHIFT 3 |

| #define | CAN_TIxR_IDE (1 << 2) |

| #define | CAN_TIxR_RTR (1 << 1) |

| #define | CAN_TIxR_TXRQ (1 << 0) |

| #define | CAN_TDTxR_TIME_MASK (0xFFFF << 15) |

| #define | CAN_TDTxR_TIME_SHIFT 15 |

| #define | CAN_TDTxR_TGT (1 << 5) |

| #define | CAN_TDTxR_DLC_MASK (0xF << 0) |

| #define | CAN_TDTxR_DLC_SHIFT 0 |

| #define | CAN_RIxR_STID_MASK (0x7FF) |

| #define | CAN_RIxR_STID_SHIFT 21 |

| #define | CAN_RIxR_EXID_MASK (0x1FFFFFFF) |

| #define | CAN_RIxR_EXID_SHIFT 3 |

| #define | CAN_RIxR_IDE (1 << 2) |

| #define | CAN_RIxR_RTR (1 << 1) |

| #define | CAN_RDTxR_TIME_MASK (0xFFFF << 16) |

| #define | CAN_RDTxR_TIME_SHIFT 16 |

| #define | CAN_RDTxR_FMI_MASK (0xFF << 8) |

| #define | CAN_RDTxR_FMI_SHIFT 8 |

| #define | CAN_RDTxR_DLC_MASK (0xF << 0) |

| #define | CAN_RDTxR_DLC_SHIFT 0 |

| #define | CAN_FMR_CAN2SB_SHIFT 8 |

| #define | CAN_FMR_CAN2SB_MASK (0x3F << CAN_FMR_CAN2SB_SHIFT) |

| #define | CAN_FMR_FINIT (1 << 0) |

Functions | |

| void | can_reset (uint32_t canport) |

| CAN Reset. More... | |

| int | can_init (uint32_t canport, bool ttcm, bool abom, bool awum, bool nart, bool rflm, bool txfp, uint32_t sjw, uint32_t ts1, uint32_t ts2, uint32_t brp, bool loopback, bool silent) |

| CAN Init. More... | |

| void | can_filter_init (uint32_t nr, bool scale_32bit, bool id_list_mode, uint32_t fr1, uint32_t fr2, uint32_t fifo, bool enable) |

| CAN Filter Init. More... | |

| void | can_filter_id_mask_16bit_init (uint32_t nr, uint16_t id1, uint16_t mask1, uint16_t id2, uint16_t mask2, uint32_t fifo, bool enable) |

| CAN Initialize a 16bit Message ID Mask Filter. More... | |

| void | can_filter_id_mask_32bit_init (uint32_t nr, uint32_t id, uint32_t mask, uint32_t fifo, bool enable) |

| CAN Initialize a 32bit Message ID Mask Filter. More... | |

| void | can_filter_id_list_16bit_init (uint32_t nr, uint16_t id1, uint16_t id2, uint16_t id3, uint16_t id4, uint32_t fifo, bool enable) |

| CAN Initialize a 16bit Message ID List Filter. More... | |

| void | can_filter_id_list_32bit_init (uint32_t nr, uint32_t id1, uint32_t id2, uint32_t fifo, bool enable) |

| CAN Initialize a 32bit Message ID List Filter. More... | |

| void | can_enable_irq (uint32_t canport, uint32_t irq) |

| CAN Enable IRQ. More... | |

| void | can_disable_irq (uint32_t canport, uint32_t irq) |

| CAN Disable IRQ. More... | |

| int | can_transmit (uint32_t canport, uint32_t id, bool ext, bool rtr, uint8_t length, uint8_t *data) |

| CAN Transmit Message. More... | |

| void | can_receive (uint32_t canport, uint8_t fifo, bool release, uint32_t *id, bool *ext, bool *rtr, uint8_t *fmi, uint8_t *length, uint8_t *data, uint16_t *timestamp) |

| CAN Receive Message. More... | |

| void | can_fifo_release (uint32_t canport, uint8_t fifo) |

| CAN Release FIFO. More... | |

| bool | can_available_mailbox (uint32_t canport) |